.png) STMCU小助手

发布时间:2021-12-12 21:00

STMCU小助手

发布时间:2021-12-12 21:00

|

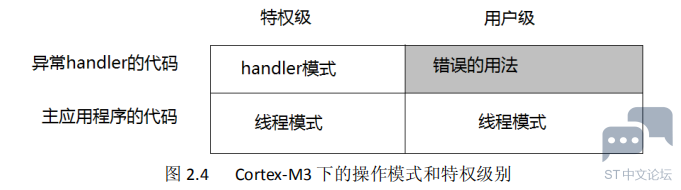

MPU(内存保护单元): B8 S" @: j5 D 1. 前言7 s5 c+ _% [% T3 ~! y: h- s 在跟项目过程中,使用的F7和H7两个芯片,在用FSMC和FPGA通信时,由于其CACHE的原因,导致数据一直出错,后来通过加入MPU顺利解决此问题。因此,去学习了一下MPU,在此记录下学习的笔记,可能有理解错误的地方,欢迎指出。 参考:7 y9 x; A" S: K$ s STM32F7中文参考手册.pdf STM32F7编程手册.pdf STM32 MPU说明.pdf/ Z/ Y* |1 r p) ~+ V Cortex M3权威指南(中文).pdf, }! V1 l: t2 J& x6 d+ ` STM32F7开发指南-寄存器版本_V1.0.pdf' t7 b/ Q& z. u) S0 c9 v 2. 操作模式和特权级别7 B5 V' B: p3 Q/ C 详情------Cortex M3权威指南(中文).pdf-----chpt023 b3 S: m; s8 z 2.1操作模式 Handler模式:异常服务相关的代码" D7 I' j0 L9 f- v/ a7 v, a 线程模式:普通应用相关的代码& }1 G) g- {8 X# ?$ ^( g0 _8 I 个人理解是如中断服务程序的代码与正常执行的代码。 k& c- E# d0 G& P7 `3 E, e+ s# ~; l 2.2 特权级别" S# e8 z% z: U$ X" e 分:a.特权级 b.用户级 区别在于对存储器的访问权限不同,特权级相当于管理员权限,除了MPU限制的区域外其他都可以访问,而并不是所有区域都对用户级开放。3 ?& s! {$ B5 S ( o: D! s& Y, P9 H" J# v% k. h _2 l 2.3 联系7 L0 R% q c# t" e

( j! z- T6 t5 R 正常执行的应用程序代码,对特权级和用户级开放;但是异常代码如中断服务程序,仅能对特权级开放。7 v& @$ d: H4 ~

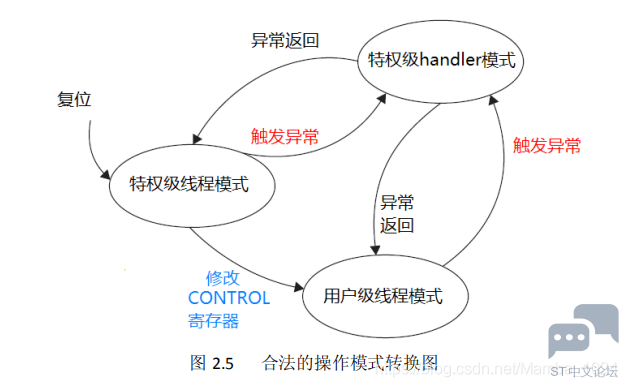

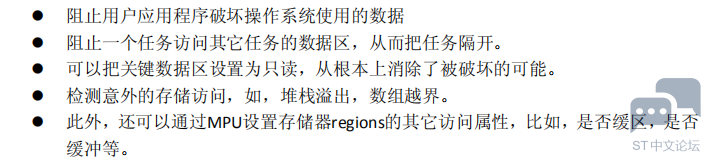

/ o( X6 l2 x/ u3 x' h 如图:当产生异常时要去执行异常代码,执行完成返回到断点。而无论在用户级还是特权级线程模式下,即使是用户级,在进入handler代码时也会暂时被提升到特权级模式,因为handler模式不能被用户级访问。 特权级可任意访问,包括切换到用户级,仅需要修改CONTROL寄存器即可。0 K7 p' B0 r; H 但是用户级切换到特权级不同,需要先申诉(执行SVC指令,触发该异常,进入异常服务代码),由于异常服务代码中是特权级模式,因此可以任意修改CONTROL寄存器,这样才能将用户级----转换---->特权级。 ; \7 u, c* h7 A# R6 W' r* l 3. MPU Y) w( P$ O. v3 j- X, q Memory Protect Uint-----内存保护单元- A" M4 R5 n. t) }& I 3.1 作用 参考了以上的PDF,大致说了以下的作用。, V* ]6 F+ ~8 ]$ K: n " U; J* z N( [# ~$ W" S' H3 \$ c

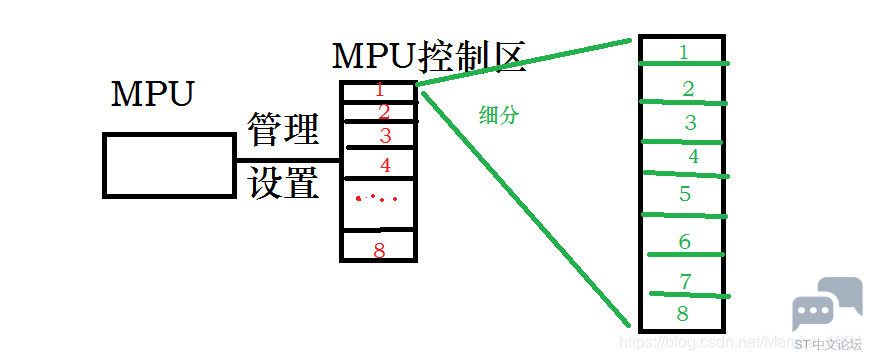

其实更多给我的理解是:通过MPU对存储器的某些区域进行属性设置,设置其对特权级/用户级开放,可读可写/只读/只写、禁止访问、全访问、支持/禁止CACHE、缓冲等等的属性,通过MPU管理存储器,不至于某块内存被非法访问、数据破坏、CACHE等等。' D* F3 M/ |; D' a8 I! w$ @ 3.2 REGION(区) STM32F7支持8个区,也就是说,MPU控制器通过8个区来管理存储器。2 P( s! T, n0 d 如果8个区不够,每个区都可以再细分为8个子区。大概理解图如下 7 g9 u8 n( t* k

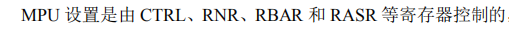

. n2 |5 b1 v( f. C* k; D7 W" T 背景区* F6 |! V( t/ g1 M! l' B- F0 m 背景区,即没有被设置到MPU管理区的其他所有地址,背景区只能被特权级访问。否则出现MemManage异常,如果开了MemManage,会进入MemManage中断服务程序。% b0 H9 P0 U8 |3 _; W/ N7 G 5 u4 x/ L/ E+ }) `" f& t4 s 3.3 MPU寄存器 M3权威指南中的MPU寄存器

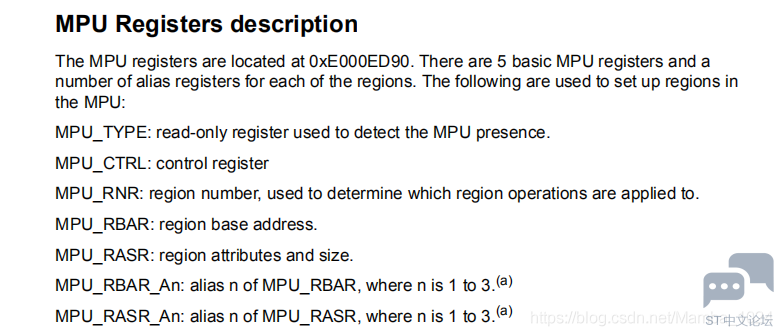

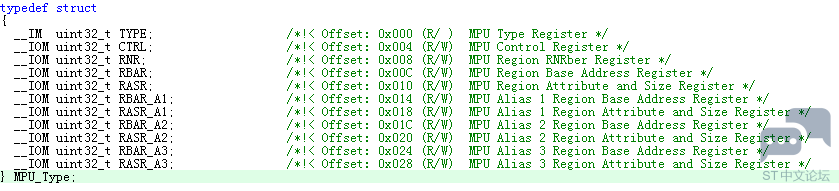

. J& h+ H5 \$ ^+ O, W7 R" Z ^9 q 原子教程中的寄存器

: {' \, T0 r% N" M: W7 [8 d! T7 ~3 h M7 MPU手册

MDK工程中MPU控制器的寄存器

3 b7 z! v b' |$ w/ i4 R8 q6 v 其中: b! l$ |1 A2 C7 G Y7 X

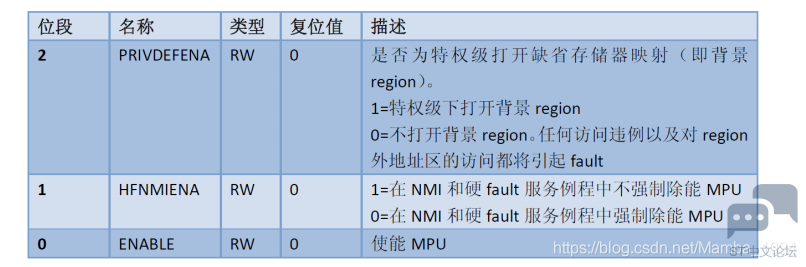

可以看出MPU指向0xE000ED90,并结合MPU_Type类型,可以推算出,其每个寄存器的地址,都和M3权威手册中的寄存器对得上,因此放心操作。 W) k/ ]! M& |' `& D7 p/ W( h MPU 控制寄存器(CTRL)

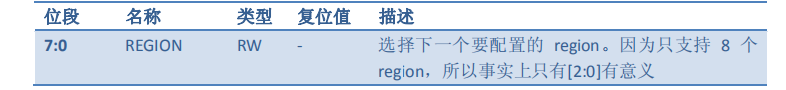

: E5 O$ {8 r0 }: r" Q) B+ Y+ w 仅三个位有效9 K% E# S! A8 p PRIVDEFENA:配置为1,特权级能访问背景区,用户级不行,而配置为0,仅能访问REGION区,其他都会出错,包括属于背景区的区域。 HFNMIENA:用于在NM1或者FAULT中断关闭MPU$ }* U/ u1 [9 ] J/ l ENABLE:使能 编号寄存器(RNR)# W! }. E& ^3 j+ d; b( W

配置每个区时要先写该寄存器,MPU控制器就知道在配置哪个区。比如要配置REGION 1,需要向RNR寄存器写入一个1;配置好后需要配置REGION5,仍向RNR写入5。 MPU 基地址寄存器(RBAR)% n4 q9 W' G& k% _ {8 S7 D $ a; P: g4 g* _* o, T8 c

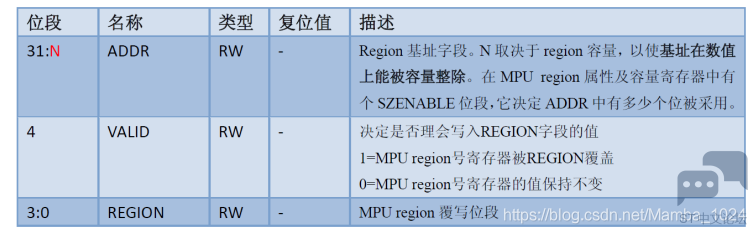

一般不适用VALID位和REGION位,这两位的意思是覆盖RNR里面的值,也就是这两个的值才是我们正在配置的REGION,RNR不生效。/ o( t+ L1 `& b: n7 E+ P1 C $ `% h9 ^' i+ f. r0 r; I; I ADDR:配置MPU某个REGION管理的存储器的基地址,要求是----需要该地址需要是REGION大小的整数倍,比如REGION1设置为64K,那么ADDR的值需要如0X0001 0000、0X0002 0000等,0X0001000065536/102464K刚刚好 MPU 区域属性和容量寄存器(RASR) 1 v( ]; }, Z" h! a0 G

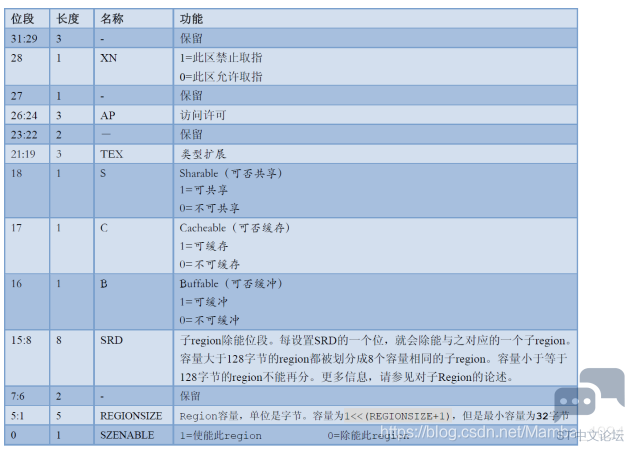

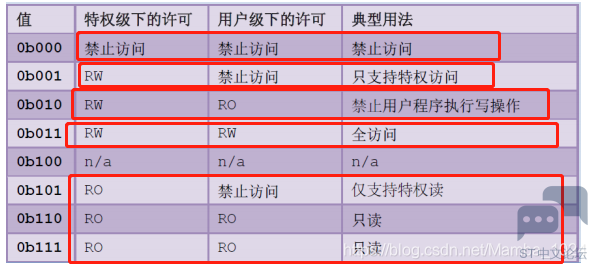

0 p& b7 I% B4 j! x XN:设置的REGION区管理范围是否允许取指+ T7 {$ J% O) |: Y1 l* Q AP:基本是6种形式。, d' u' W% |' Z; L8 e9 a D3 C/ \1 y: w: d

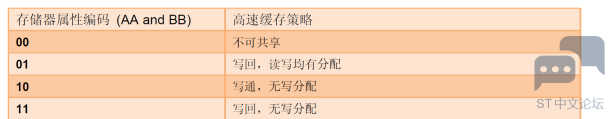

. W' c; @+ G( w/ g3 E 分别是:全禁止(任何级别不可读写),只特权可读可写,用户级不可写,任何级别可读可写,只特权只读,只读。 TXE,C,B,S

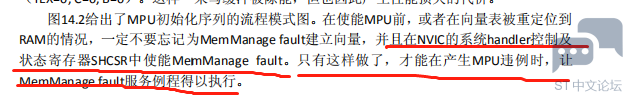

# A+ D1 v# Q$ }+ E* {& o3 V9 x 其中: 强序-------------按照程序一条指令一条指令顺序执行。 共享------------一块内存可同时被多个设备访问,比如两个DMA同时访问某个区域。 缓冲------------类似有个缓冲器,但是要考虑是否有数据缓冲的阈值,未验证。$ G! ^( T- T- y7 y# Q6 D6 n+ |5 E 缓存-----------CACHE,有命中和MISS,可能造成数据不一致,但是效率较快。 写回-----------CPU更新到CACHE,仅当需要丢弃时CPU将数据更新到主存,期间数据不一致。' R0 }9 t2 N8 M2 ^" Y 写通-----------CPU更新数据时,CACHE和主存都更新。 注意3 s- X3 i4 W0 {- G" k M3权威指南中,P195,需要SHCSR使能MEM中断。5 p$ i4 S/ }3 C( T5 Y' C, @, ^; }3 N

7 G( A4 v7 y% q5 D) L 3.3 相关代码3 m7 t* i. C( J. X+ m1 l& ]( z0 ` 初始化,将SRAM 0X20002000设置为128字节,不可共享/缓冲/CACHE,且只能特权级读* `' t. E4 m; T$ G1 A4 `2 z# m8 H

测试,写入一个值,即进入MEM中断

" B+ o( Z6 `: I7 N |

基于STM32F746G-Discover的扩展电路板

【合集】STM32F7教程、资料大集合

F769 Discovery实现播放U盘音乐的播放器

STM32 VS Code Extension (在Ubuntu上开发STM32,ST官方vscode插件使用指南)

STM32F765@216MHz跑NES模拟器【代码】【视频】

基于STM32F7实现ADC软件触发+轮询采集

基于STM32F7进行ADC采集解决更新问题

基于STM32F7使用定时器经验分享

实现基于STM32F7中周期采集

基于STM32F7中实现采集和中断