.png) STMCU小助手

发布时间:2021-12-18 17:42

STMCU小助手

发布时间:2021-12-18 17:42

|

一、Cache ( M, e# O3 l& r6 E/ \ 1、介绍, l; [6 |+ R( @# ~# V k N/ \ Z $ h3 Y% o* C. m `9 N b( q Cache又分数据缓存D-Cache和指令缓冲I-Cache,STM32H7的数据缓存和指令缓存大小都是16KB。STM32H7主频是400MHz,除了TCM和Cache以400MHz工作,其它AXI SRAM,SRAM1,SRAM2等都是以200MHz工作。数据缓存D-Cache就是解决CPU加速访问SRAM。0 _8 v# B8 x4 U9 S1 t8 x: c 如果每次CPU要读写SRAM区的数据,都能够在Cache里面进行,自然是最好的,实现了200MHz到400MHz的飞跃,实际是做不到的,因为数据Cache只有16KB大小,总有用完的时候。 + O3 U5 W* y! o g7 W 2、操作,分为读操作和写操作 读操作: 如果CPU要读取的SRAM区数据在Cache中已经加载好,这就叫读命中(Cache hit),如果Cache里面没有怎么办,这就是所谓的读Cache Miss。8 e* `. i+ P- s9 F( s7 L1 ]% k5 u1 j ; O% E: O' B, {2 { 写操作: 如果CPU要写的SRAM区数据在Cache中已经开辟了对应的区域(专业词汇叫Cache Line,以32字节为单位),这就叫写命中(Cache hit),如果Cache里面没有开辟对应的区域怎么办,这就是所谓的写Cache Miss。" X& k; ^4 {8 M P6 V; q( p8 Q 7 I5 H9 W" G3 p' k: G8 J( A M 3、H7支持的Cache策略,共4种 / c- @( q( y7 P! C* L

<回写:如果Cache中有,写数据只写到Cache,不写到RAM。> <透写:如果Cache中有,写数据也要同时写到Cache和RAM。>( W8 Z: u( x" @0 x+ ] <write allocate:写数据时,如果Cache中没有,那么就要在Cache中开辟一个空间,把数据写入Cache,同时把RAM中的相邻数据加载进来填充Cache。> <no write allocate:写数据时,如果Cache中没有,那么把数据直接写入RAM。> <read allocate:读数据时,如果Cache中没有,那么就要在Cache中开辟一个空间,把数据从RAM中加载进来,后续的读操作,就可以直接从Cache中读取了。>( @, q% L6 v1 F" Q& `1 F. d8 w <no read allocate:读数据时,如果Cache中没有,那么直接从RAM中读。>" h) T5 j x& \8 | 9 L- {7 f" r! _1 { 4、风险

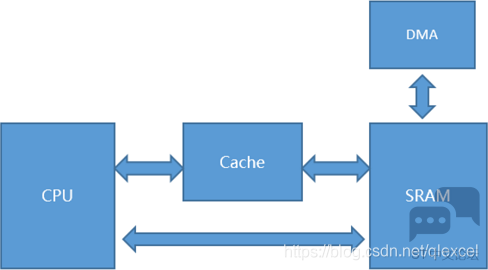

从上面的图就看出来使用Cache的风险,因为DMA是直接与SRAM交换数据的,而CPU与SRAM之间隔了一个Cache,如果DMA更新了某个数据到SRAM,CPU要去访问,而恰好Cache中有,那么CPU就不会去SRAM中拿,就会拿到Cache中已经过时的数据。因此使用了DMA的内存区要配置为无Cache或者拿数据前清一次Cache。6 \3 n m0 D9 Z9 ^, h1 O4 t6 U 9 L9 t2 I; z* }5 b) c2 R, Q$ J 5、相关函数: ^& i/ ?: z% G2 ^ ; [+ ^' ?( Z. N SCB_EnableICache(void) :用于使能指令Cache,系统上电后优先初始化即可。 . \. w/ e# e9 ~/ b0 V u SCB_DisableICache(void) :用于禁止指令Cache。 SCB_InvalidateICache(void) :用于将指令Cache无效化,无效化的意思是将Cache Line标记为无效,等同于删除操作。这样Cache空间就都腾出来了,可以加载新的指令。( u4 T) W; k4 C& A- b0 z SCB_EnableDCache(void) :用于使能数据Cache,系统上电后优先初始化即可。 $ x. g3 y1 h9 C. X1 N/ A- K( \ SCB_DisableDCache(void) :用于禁止数据Cache。8 E; a9 C5 s( s' L) i0 U . D/ X8 _2 _7 k: O- x SCB_InvalidateDCache(void) :用于将数据Cache无效化,无效化的意思是将Cache Line标记为无效,等同于删除操作。这样Cache空间就都腾出来了,可以加载新的数据。 + Q9 h5 L4 |1 M0 h! W1 [4 l8 C SCB_CleanDCache(void):用于将数据Cache清除,清除的意思是将Cache Line中标记为dirty的数据写入到相应的存储区。) l! u6 L9 [+ C6 P2 d SCB_CleanInvalidateDCache(void) :此函数是前面两个函数SCB_InvalidateDCache和SCB_CleanDCache的二合一。将Cache Line中标记为dirty的数据写入到相应的存储区后,再将Cache Line标记为无效,表示删除。这样Cache空间就都腾出来了,可以加载新的数据。 SCB_InvalidateDCache_by_Addr(uint32_t *addr,int32_t dsize):可以指定地址和存储区大小,地址要32字节对齐,大小要是32字节的整数倍。用于将数据Cache无效化,无效化的意思是将Cache Line标记为无效,等同于删除操作。这样Cache空间就都腾出来了,可以加载新的数据。 . e2 @ P4 v" f0 D SCB_CleanDCache_by_Addr(uint32_t *addr,int32_t dsize):可以指定地址和存储区大小,地址要32字节对齐,大小要是32字节的整数倍。用于将数据Cache清除,清除的意思是将Cache Line中标记为dirty的数据写入到相应的存储区。 : i! L+ ~8 j- t2 m) g, l& j SCB_CleanInvalidateDCache_by_Addr(uint32_t *addr,int32_t dsize):可以指定地址和存储区大小,地址要32字节对齐,大小要是32字节的整数倍。将Cache Line中标记为dirty的数据写入到相应的存储区后,再将Cache Line标记为无效,表示删除。这样Cache空间就都腾出来了,可以加载新的数据。$ h" J" d8 U: U% D) h* E! D ! U' K- G3 Z5 \ C0 o! z b" a$ m 8 g" p* E. y1 w& `3 q 0 ?& O9 W1 q% L2 ] 二、MPU9 o* [1 `: T. I8 e- G$ i5 F6 ~ 1、作用 4 g) j, p j6 e D 防止不受信任的应用程序访问受保护的内存区域; 防止用户应用程序破坏操作系统使用的数据;通过阻止任务访问其它任务的数据区;允许将内存区域定义为只读,以便保护重要数据;检测意外的内存访问。 简单的说就是内存保护、外设保护和代码访问保护。& d# n F) c& |" y3 ? 2、MPU可以配置的三种内存类型 5 `$ K2 U5 K: ^1 d' O6 [7 U8 ] 1)、Normal memory CPU以最高效的方式加载和存储字节、半字和字,对于这种内存区,CPU的加载或存储不一定要按照程序列出的顺序执行。 ) H7 N D& D* W h4 M 2)、Device memory ! _( q+ W: W* D# O- I" n4 w4 M- m& E* i 对于这种类型的内存区,加载和存储要严格按照次序进行,这样是为了确保寄存器按照正确顺序设置。 3)、Strongly ordered memory 程序完全按照代码顺序执行,CPU需要等待当前的加载/存储指令执行完毕后才执行下一条指令。这样会导致性能下降。 3、MPU的使用 MPU可以配置保护16个内存区域(这16个内存域是独立配置的),每个区域最小要求256字节,每个区域还可以配置为8个子区域。由于子区域一般都相同大小,这样每个子区域的大小就是32字节,正好跟Cache的Cache Line大小一样。9 x/ p3 S' y0 A+ d5 [! B& v- r; g& [0 ^ 3 Z% i4 @% z* C8 x% X 使用时把一段连续的内存区配置为一个MPU保护区域,然后再配置这个MPU保护区域的特性。比如128KB的DTCM、64KB的SRAM4、32MB的SDRAM。MPU保护区域的特性使用MPU_RASR寄存器来配置,描述如下:

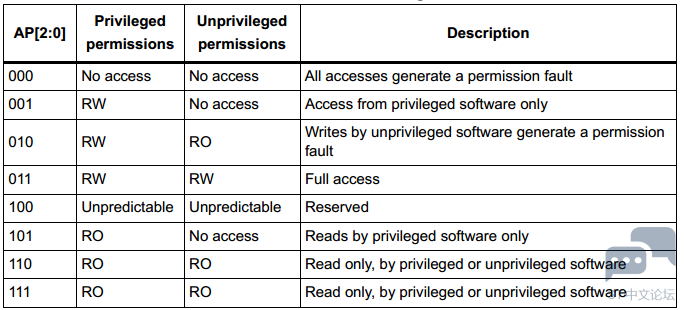

6 n6 o. T, z' T4 r 1)、XN:用于控制这个MPU保护区域能否执行程序代码。+ V$ G9 t) v8 j$ y0 r5 ^, E 2)、AP:用于控制这个MPU保护区域的特权级和非特权级的读写访问权限。6 w% r" s' ~9 W" S( ~& ~5 R" d

- q" v* t: `# ~! y7 @ 3)、TEX、C、B、S:H7支持4种Cache策略,这几位就是用来控制这个MPU保护区域使用哪一种。9 u w, c' Y- g' }5 r) u . |9 L6 s A* n( _

/ [' b( e, @, H: V S位用于解决多总线或者多核访问的共享问题,一般不要开启。3 }! ~6 \! o; q0 O# d; g L- @/ K7 d, A+ ]# F 4)、SRD:这个位用于控制内存区的子区域 ,使用的是bit[15:8],共计8个bit,一个bit控制一个子区域, 0表示使能此子区域, 1表示禁止。一般情况下,取值0x00,表示8个子区域都使能。 3 P( ^2 x B$ D3 ~9 k 5)、SIZE:配置这个MPU保护区域的大小。/ ^: i- g' G$ G; H 三、HAL配置例程4 }* h7 S8 \; u

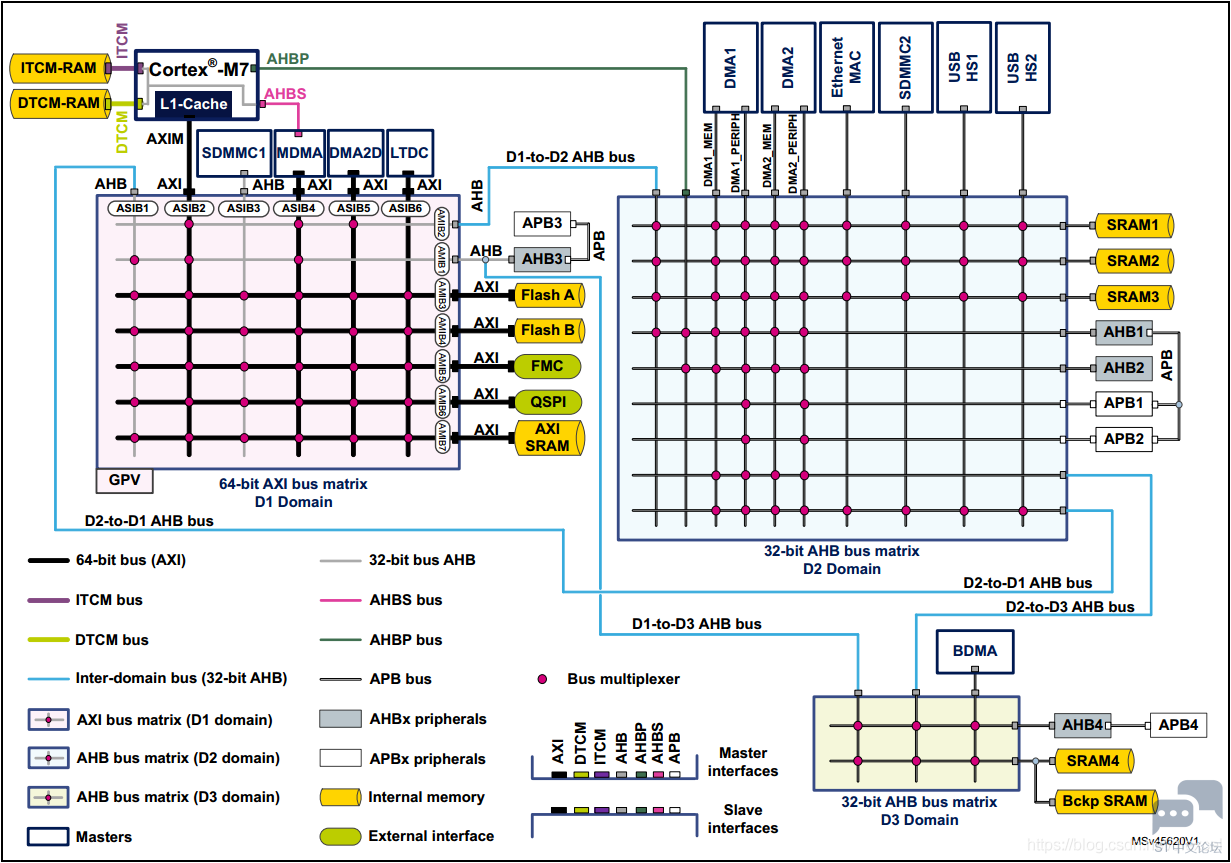

四、其他 值得一提的是,LTDC也是直接从RAM拿数据的,如果你使用了GUI(比如EMWIN),你的显示数据可能会暂存在Cache,而LTDC直接从RAM拿数据,就可能造成画面撕裂、重影、斑点之类的问题。解决方法是,把显存设置成透写。 从下面的图可以看到,Cache是在M7那个框里面的。而框外面的外设都可以直接与RAM交换数据,因此使用外设操作数据时都要考虑一下Cache的影响,不然异常可能难以预料。. v! b8 ~1 I3 a# s d1 a$ T

|

【经验分享】STM32_H7_ADC

STM32H7R/S高性能MCU:安全性,大存储和优异图显赋能更多应用创新

Stm32H7XX GCC下分散加载实现

【银杏科技ARM+FPGA双核心应用】STM32H7系列10——ADC

DIY-STM32H750核心板

[nucleo-H7A3ZI-Q]1-点亮一个皮皮灯

DIY-STM32H743核心板

【银杏科技ARM+FPGA双核心应用】STM32H7系列57——MDK_FLM

1月10日有奖直播 | 基于STM32 的CODESYS智能自动化解决方案

STM32的CAN FD位定时设置注意事项