|

手头的STM32开发板全家福

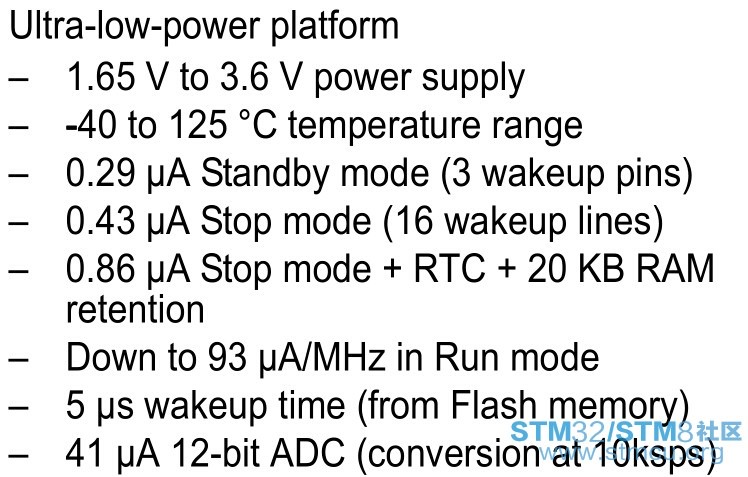

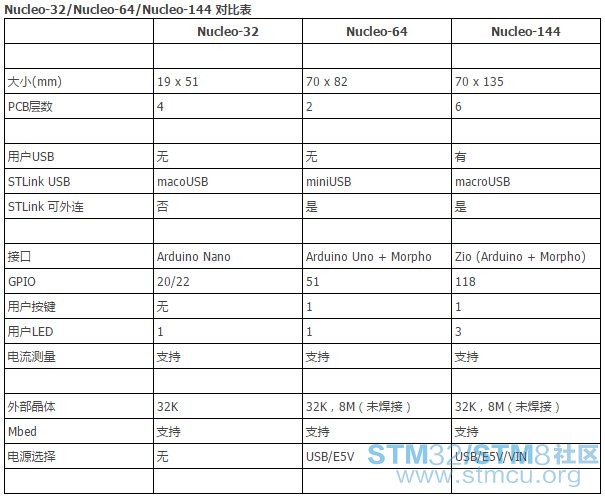

Nucleo-64是双层板,Nucleo-32是4层板, nucleo-64以STM32L073介绍,其资源丰富: 1、基于ARM系列cortex-mo+的MPU,系统时钟可以到32KHz~32Mhz之间选择。 2、拥有192KbFlash,20KbSRAM,6KbEPPROM。 3、集成LCD、USB、ADC、DACs等外设。 4、带有7channelDMA,4个USART,1个UART(低电压版),2个SPI最高频率可达16Mbit/s,3个I2C等 5、低电压(1.65V~3.6V),低功耗(standby 模式最低0.29uA, 停止模式最低0.43uA,唤醒时间只需要5us。 官网对L073介绍

L432最引人瞩目的当然是L系列的低功耗,相比TI的MSP432开发板,该开发板功耗更低。还有它的OPA功能,它的正向输入端可连接到内部DAC;输出端可连接到内部的ADC,便于采样分析 L432主要特征

相比今年新出的L011,L432的时钟一下提高到80M,换成了性能更强劲的cortex-M4内核,flash也由16k扩展到256K,SRAM由2K扩展到64K,内存大的提升。L011和432都兼容arduino Nano,L011的内存似乎就是和arduino的差不多,uno是32K flash,2KRAM、0.5Kbootloader。相比L011,L432还支持USB可图形处理,对linux也支持。 Nucleo-32/64/144b比较

如下关于cortex-M介绍 ARM Cortex-M系列主要面向单片机领域,拥有M0、M1、M3、M4等多款,Cortex-M4内核是最新的,在Cortex-M3的基础上进一步加强了控制和数字信号处理性能。Cortex-M3的速度比ARM7快三分之一,功耗低四分之三, TI的OMAP4系列里面集成了Cortex-M3,在最新的OMAP5 里面升级到Cortex-M4,主要负责底层处理。

Cortex-M系列基于ARMv7-M架构(用于Cortex-M3和Cortex-M4)构建,而较低的Cortex-M0+基于ARMv6-M架构构建。首款Cortex-M处理器于2004年发布,Cortex-M系列能够实现在FPGA中作为软核来用,但更常见的用法是作为集成了存储器、时钟和外设的MCU。 Cortex-M3和Cortex-M4是非常相似的内核。二者都具有1.25DMIPS/MHz的性能,配有3级流水线、多重32位总线接口、时钟速率可高达200MHz,并配有非常高效的调试选项。最大的不同是,Cortex-M4的内核性能针对的是DSP。Cortex-M3和Cortex-M4具有相同的架构和指令集(Thumb-2)。然而,Cortex-M4增加了一系列特别针对处理DSP算法而优化的饱和运算和SIMD指令。以每0.5秒运行一次的512点FFT为例,如果分别在同类量产的Cortex-M3 MCU和Cortex-M4 MCU上运行,完成同样的工作,Cortex-M3所需功耗约是Cortex-M4所需功耗的三倍。此外,也有在Cortex-M4上实现单精度浮点单元(FPU)的选项。如果应用涉及到浮点计算,那在Cortex-M4上完成比在Cortex-M3上完成要快得多。也就是说,对于不使用Cortex-M4上DSP或FPU功能的应用而言,其性能和功耗与Cortex-M3相同。换句话说,如果使用DSP功能,那就选择Cortex-M4。否则,就选择Cortex-M3完成工作。 虽然Cortex-M0+的性能为0.95DMIPS/MHz,比Cortex-M3和Cortex-M4的性能稍稍低一些,但仍可与同系列其他高端产品兼容。Cortex-M0+采用Thumb-2指令集的子集,而且这些指令大都是16位操作数(虽然所有数据运行都是32位的),这使得它们能够很好的适应Cortex-M0+所提供的2级流水线服务。通过减少分支映射,系统就能节约一些整体功耗,而且在大多数情况下,流水线将保留接下来的四个指令。Cortex-M0+还具有专用的总线用于单周期GPIO,这意味着你能够利用位控制的GPIO实现确定接口,就像8位MCU那样,但却以32位内核的性能来处理该数据。 Cortex-M0+的另外一个重要的不同特点是增加了微型跟踪缓冲器(MTB)。该外设可使设计人员在调试过程中使用一些片上RAM来存储程序分支。这些分支随后能够回传到集成开发环境中,而且可以重建程序流程。这一功能提供了一种初步的指令跟踪能力,这对于不具备扩展跟踪宏单元(ETM)功能的Cortex-M3和Cortex-M4来说比较有意义。 参考 Nucelo系列开发板硬件对比 - 【stm32/stm8】 - 电子工程世界-论坛 http://bbs.eeworld.com.cn/thread-496983-1-1.html |

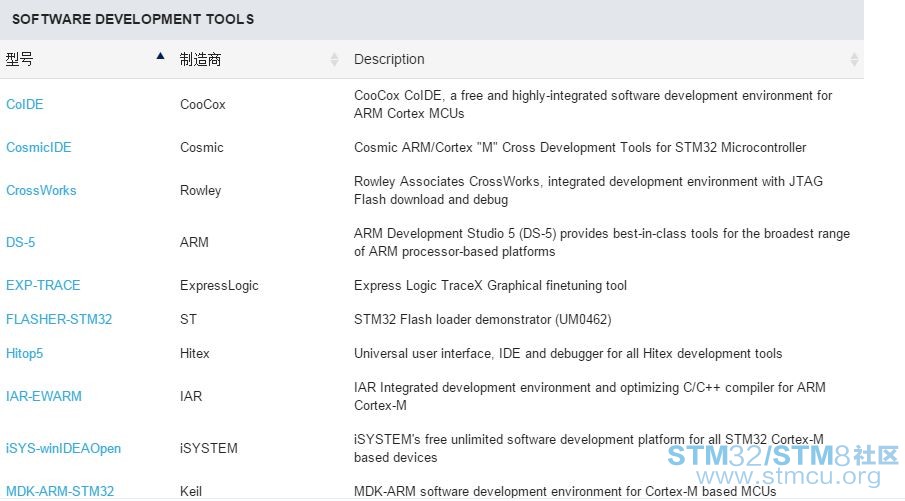

官网支持的软件

|

| 谢谢整理分享!! |

| 不错,谢谢分享! |

| 谢谢分享 |

| 谢谢分享,如果能提炼一下更好咯,哈哈 |