|

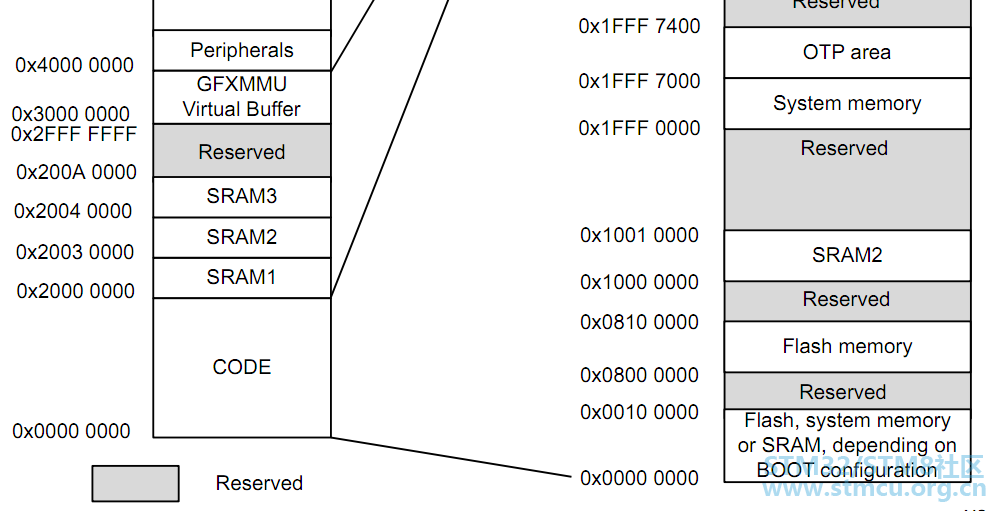

SRAM容量比较大的型号,常见的除了SRAM分为几块如 SRAM1, SRAM2, TCM RAM 等之外,还常见地址重映射的设计。 例如下面这个图是 STM32L4Rx 的地址空间,其中 SRAM2 在 0x20030000 和 0x10000000 两个地址都可以访问。

手册是这么叙述的: Execution can be performed from SRAM2 with maximum performance without any remap thanks to access through ICode bus. The SRAM2 is aliased at address 0x2004 0000, offering a continuous address space with the SRAM1 and SRAM3. 此外,选择了从片内SRAM启动时,SRAM1 会被重映射到 0x00000000 处: Boot from the embedded SRAM1: the SRAM1 is aliased in the boot memory space (0x0000 0000), but it is still accessible from its original memory space (0x2000 0000). 我有个疑问是,像上面这重地址重映射,是在 Cortex-m4 内核中实现的,还是在总线上,如 AHB Bus matrix 里面实现的?或者还有其它方式? 如果影射是总线的功能,那么DMA能够从两个地址访问同一个SRAM,没问题? |