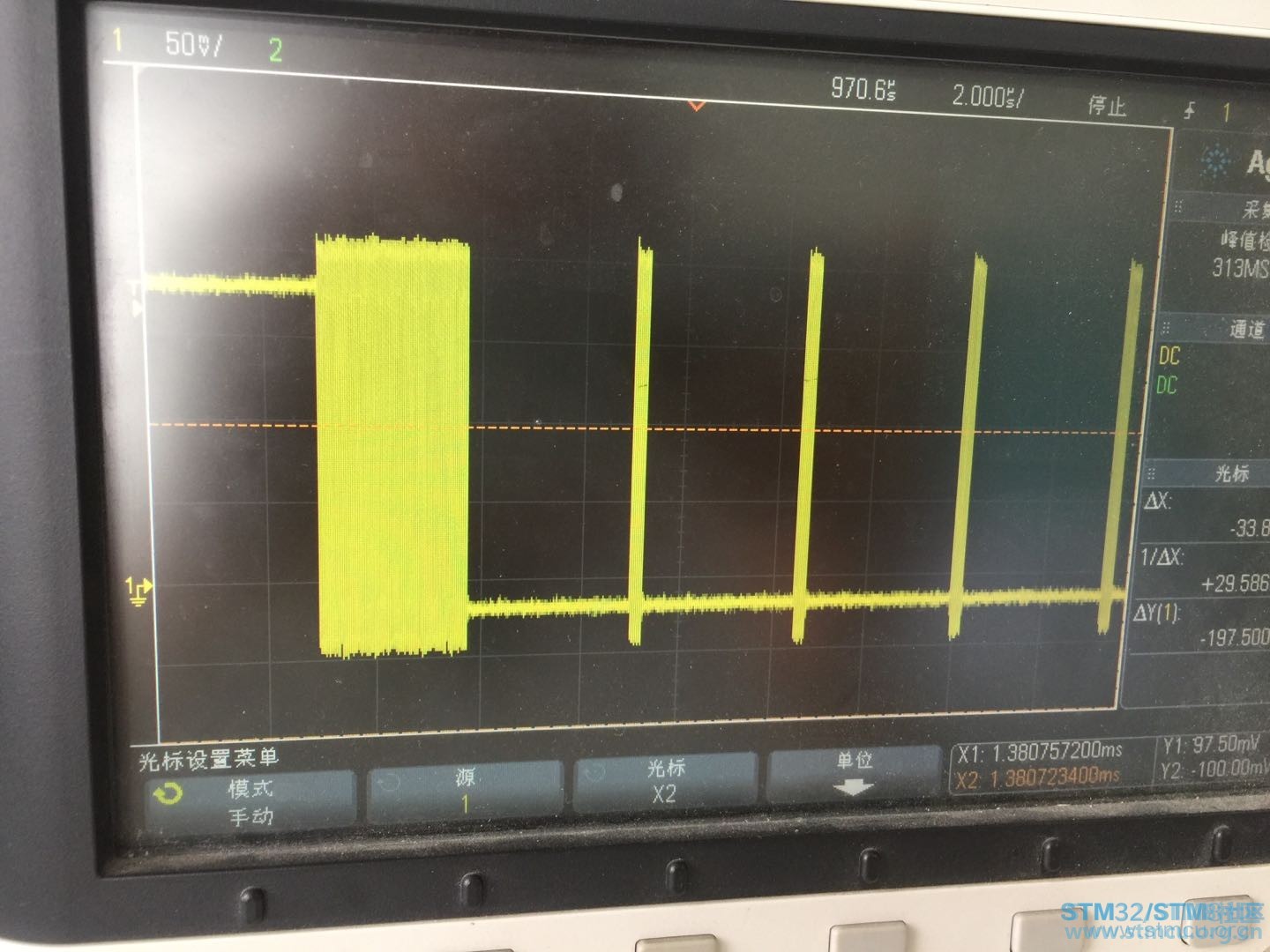

| 我使用STM32L496G,与这篇遇到相同的问题,"每次读取500个字节的数据的话,时钟会出现8个连续的周期,然后时钟被拉低了,过了很久再出现8个连续的周期" ,不知道是否是DMA的关系,不知道有没有方法可以不拉低Clock? :https://www.stmcu.org.cn/module/f ... xtra=page%3D&page=2 引用"永夜衣袂"的图片: |

| 你好,我也在弄QSPI DMA这块,能否交流下 Q734806050 |

从手册上看,这个QSPI在某些模式下无操作或者操作延误时,会使能CLK为低。所以要检查当时是否存在这种状态。此外如果DMA设置的NORMAL模式,当次数到了时候处理时要看看是否会延误QSPI动作。另外外部FLASH的页操作在特殊情况下是否也有处理成延时出现的情况 |

| 请问楼主这个问题解决没?我也在用QSPI发数据时在示波器中看到clk不连续。 |

微信公众号

微信公众号

手机版

手机版