|

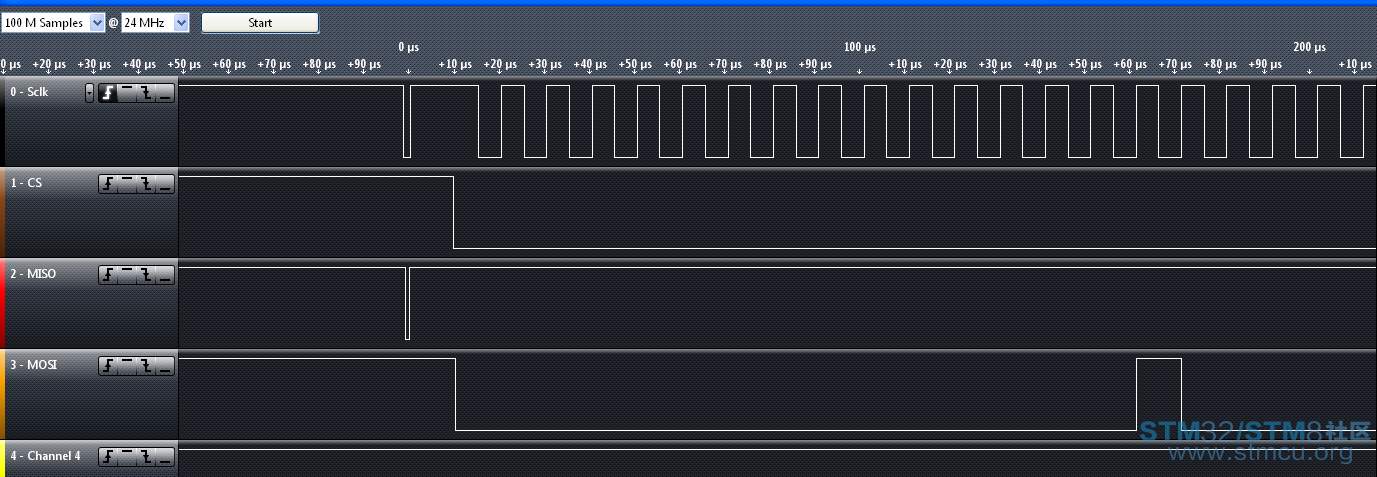

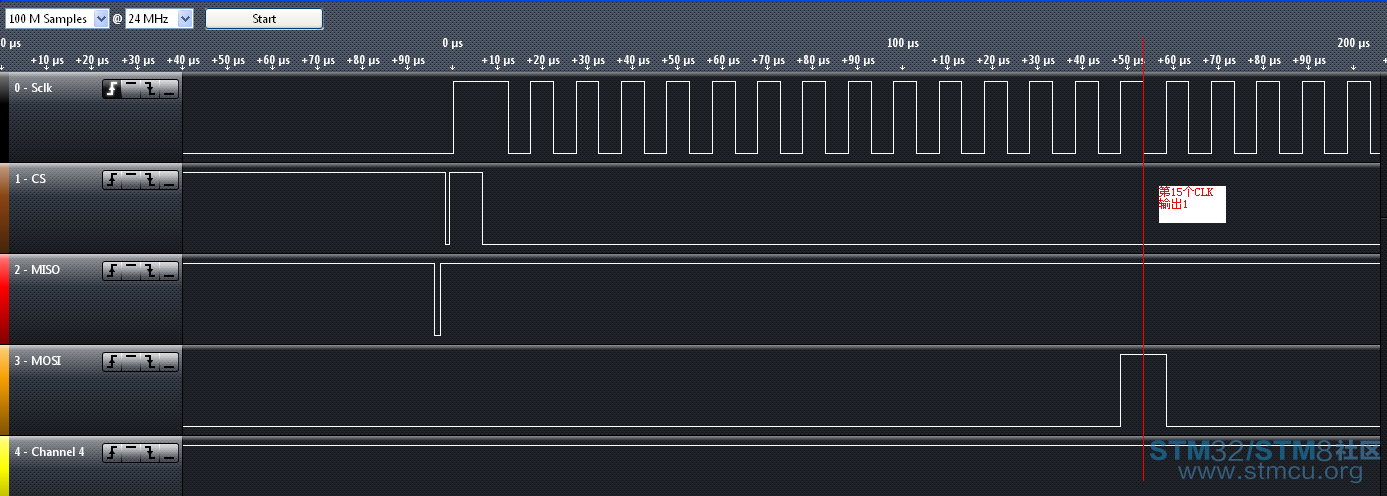

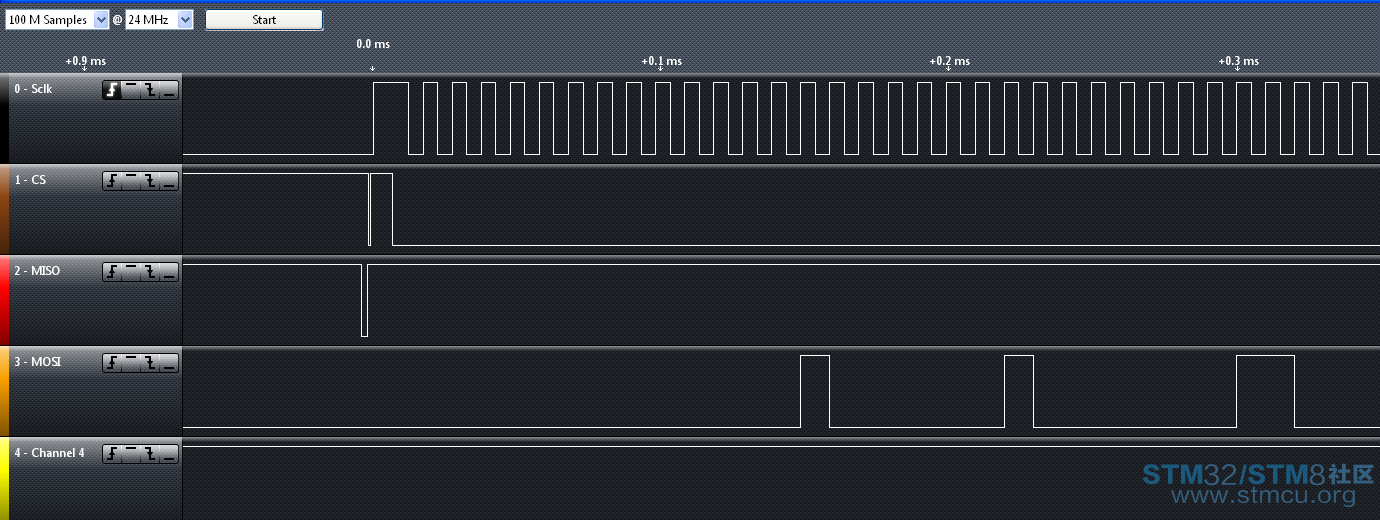

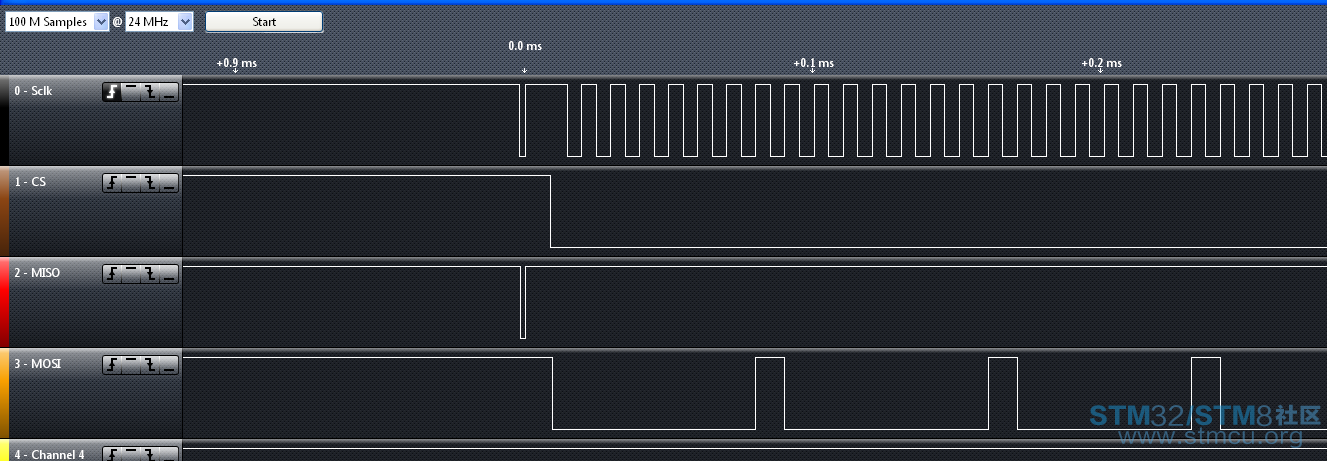

本帖最后由 zodiac-386300 于 2016-10-11 09:53 编辑 型号:STM32F411RE 如题在8bits mode,SPI SPI_CPOL_High,SPI_CPHA_1Edge模式下,Txdata 为0,1,2,3... 如图1在reset 后 bit 1在第15个 CLK出现,理应在第16个,从wave来看是reset后第一笔数据少了一个CLK导致 如图2 不再reset 再次发送则正常 如图3 在txdata为1,1,2,3... reset 后 bit 1依然在第15个 CLK出现,第一笔data “1” 神秘消失了 ,图4则为不再reset 再次发送正常 其它三种CPOL,CPHA模式下 wave 没有此类异常,还求大神指点 配置代码 GPIO_InitStruct.GPIO_Pin = GPIO_Pin_15 | GPIO_Pin_14 | GPIO_Pin_13; GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF; GPIO_InitStruct.GPIO_OType = GPIO_OType_PP; GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_NOPULL; GPIO_Init(GPIOB, &GPIO_InitStruct); GPIO_PinAFConfig(GPIOB, GPIO_PinSource13, GPIO_AF_SPI2); GPIO_PinAFConfig(GPIOB, GPIO_PinSource14, GPIO_AF_SPI2); GPIO_PinAFConfig(GPIOB, GPIO_PinSource15, GPIO_AF_SPI2); GPIO_InitStruct.GPIO_Pin = GPIO_Pin_12; GPIO_InitStruct.GPIO_Mode = GPIO_Mode_OUT; GPIO_InitStruct.GPIO_OType = GPIO_OType_PP; GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz; GPIO_InitStruct.GPIO_PuPd = GPIO_PuPd_UP; GPIO_Init(GPIOB, &GPIO_InitStruct); GPIOB->BSRRL |= GPIO_Pin_12; SPI_InitStruct.SPI_Direction = SPI_Direction_2Lines_FullDuplex; // set to full duplex mode, seperate MOSI and MISO lines SPI_InitStruct.SPI_Mode = SPI_Mode_Master; // transmit in master mode, NSS pin has to be always high SPI_InitStruct.SPI_DataSize = SPI_DataSize_8b; // one packet of data is 16 bits wide SPI_InitStruct.SPI_CPOL = SPI_CPOL_High; // clock is High when idle SPI_InitStruct.SPI_CPHA = SPI_CPHA_1Edge; // data sampled at first edge SPI_InitStruct.SPI_NSS = SPI_NSS_Soft | SPI_NSSInternalSoft_Set; // set the NSS management to internal and pull internal NSS high SPI_InitStruct.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_32; SPI_InitStruct.SPI_FirstBit = SPI_FirstBit_MSB;// data is transmitted MSB first SPI_Init(SPI2, &SPI_InitStruct); SPI_Cmd(SPI2, ENABLE); 另外:测试过两块 STM32F411 板子都是这样的行为,板子损坏的概率应该比较小,如果理解没错的话,可能是STM32F411 SPI Peripheral 的一个小bug |

å¾2 with no reset

å¾1 with reset

å¾3 第ä¸ç¬ä¸º1 with reset

å¾4 第ä¸ç¬ä¸º1 with no reset

微信公众号

微信公众号

手机版

手机版

签到签到

签到签到