本帖最后由 q10083129 于 2018-4-30 15:06 编辑

各位大侠好

我目前在编写FSMC初始化程序,给STM32F103VCT6外扩4MSRAM.,我在给仿真调试的时候,当我给0x60010001写入数据的时候,0x60110001,0x60210001,0x60310001。。。。0x63F10001,中的地址也会被写入相同的数据,而且我的SRAM只有4M,但keil中能读到0x63000000~0x63FFFFFF以内的数据,而且都是每隔1M内容重复。

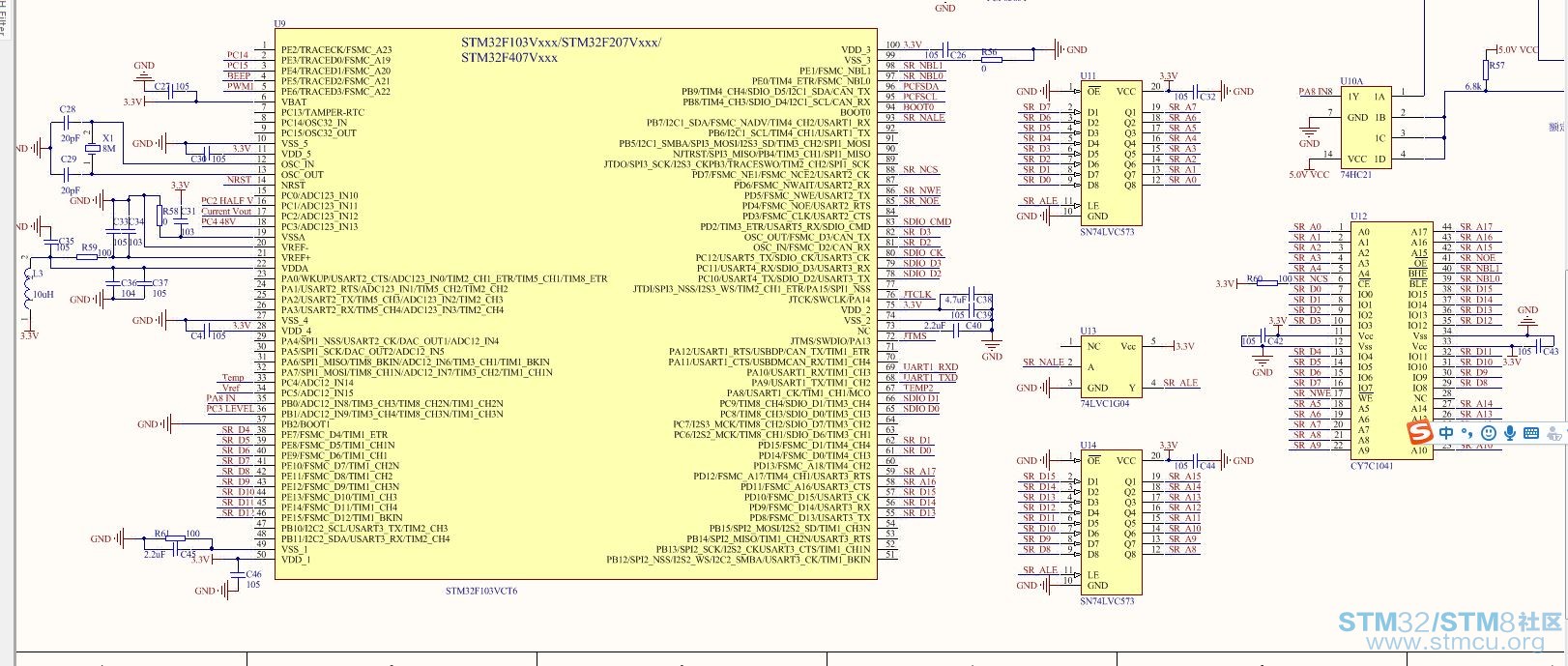

下面是我的SRAM初始化程序以及system_stm32f10x.c中的函数和测试程序和电路图。

- #include "sram.h"

- #include "usart.h"

- #define Bank1_SRAM3_ADDR ((u32)(0x60000000))

-

- //³õʼ»¯ÍⲿSRAM

- void FSMC_SRAM_Init(void)

- {

- FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;

- FSMC_NORSRAMTimingInitTypeDef readWriteTiming;

- GPIO_InitTypeDef GPIO_InitStructure;

-

- RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB|RCC_APB2Periph_GPIOD|RCC_APB2Periph_GPIOE,ENABLE);

- RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC,ENABLE);

-

- GPIO_InitStructure.GPIO_Pin = 0xDFB3; //PORTD¸´ÓÃÍÆÍìÊä³ö

- GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //¸´ÓÃÍÆÍìÊä³ö

- GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

- GPIO_Init(GPIOD, &GPIO_InitStructure);

-

- GPIO_InitStructure.GPIO_Pin = 0xFF83; //PORTE¸´ÓÃÍÆÍìÊä³ö

- GPIO_Init(GPIOE, &GPIO_InitStructure);

-

- GPIO_InitStructure.GPIO_Pin = 0x0080; //PORTE¸´ÓÃÍÆÍìÊä³ö

- GPIO_Init(GPIOB, &GPIO_InitStructure);

- readWriteTiming.FSMC_AddressSetupTime = 0x15;

- readWriteTiming.FSMC_AddressHoldTime = 0x15;

- readWriteTiming.FSMC_DataSetupTime = 0x0225;

- readWriteTiming.FSMC_BusTurnAroundDuration = 0x15;

- readWriteTiming.FSMC_CLKDivision = 0x00;

- readWriteTiming.FSMC_DataLatency = 0x00;

- readWriteTiming.FSMC_AccessMode = FSMC_AccessMode_B; //ģʽA

-

- FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1;// ÕâÀïÎÒÃÇʹÓÃNE3 £¬Ò²¾Í¶ÔÓ¦BTCR[4],[5]¡£

- FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Enable;

- FSMC_NORSRAMInitStructure.FSMC_MemoryType =FSMC_MemoryType_NOR;// FSMC_MemoryType_SRAM; //SRAM

- FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;//´æ´¢Æ÷Êý¾Ý¿í¶ÈΪ16bit

- FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode =FSMC_BurstAccessMode_Disable;// FSMC_BurstAccessMode_Disable;

- FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

- FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait=FSMC_AsynchronousWait_Disable;

- FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

- FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

- FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable; //´æ´¢Æ÷дʹÄÜ

- FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

- FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable; // ¶ÁдʹÓÃÏàͬµÄʱÐò

- FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

- FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &readWriteTiming;

- FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &readWriteTiming; //¶ÁдͬÑùʱÐò

- FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure); //³õʼ»¯FSMCÅäÖÃ

- FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM1, ENABLE); // ʹÄÜBANK3

-

- }

-

- void FSMC_SRAM_WriteBuffer(u8* pBuffer,u32 WriteAddr,u32 n)

- {

- for(;n!=0;n--)

- {

- *(vu8*)(Bank1_SRAM3_ADDR+WriteAddr)=*pBuffer;

- WriteAddr+=4;

- pBuffer++;

- }

- }

- void FSMC_SRAM_ReadBuffer(u8* pBuffer,u32 ReadAddr,u32 n)

- {

- for(;n!=0;n--)

- {

- *pBuffer++=*(vu8*)(Bank1_SRAM3_ADDR+ReadAddr);

- ReadAddr+=2;

- }

- }

- void fsmc_sram_test_write(u8 data,u32 addr)

- {

- FSMC_SRAM_WriteBuffer(&data,addr,1);//дÈë1¸ö×Ö½Ú

- }

- u8 fsmc_sram_test_read(u32 addr)

- {

- u8 data;

- FSMC_SRAM_ReadBuffer(&data,addr,1);

- return data;

- }

- void SystemInit_ExtMemCtl(void)

- {

- /*!< FSMC Bank1 NOR/SRAM3 is used for the STM3210E-EVAL, if another Bank is

- required, then adjust the Register Addresses */

- /* Enable FSMC clock */

- RCC->AHBENR = 0x00000114;

- /* Enable GPIOD, GPIOE, GPIOF and GPIOG clocks */

- RCC->APB2ENR = 0x000001E0;

-

- /* --------------- SRAM Data lines, NOE and NWE configuration ---------------*/

- /*---------------- SRAM Address lines configuration -------------------------*/

- /*---------------- NOE and NWE configuration --------------------------------*/

- /*---------------- NE3 configuration ----------------------------------------*/

- /*---------------- NBL0, NBL1 configuration ---------------------------------*/

-

- GPIOD->CRL = 0xB4BB44BB;

- GPIOD->CRH = 0xBB4BBBBB;

- GPIOE->CRL = 0xB44444BB;

- GPIOE->CRH = 0xBBBBBBBB;

- // GPIOF->CRL = 0x44BBBBBB;

- // GPIOF->CRH = 0xBBBB4444;

- // GPIOG->CRL = 0x44BBBBBB;

- // GPIOG->CRH = 0x44444B44;

-

- /*---------------- FSMC Configuration ---------------------------------------*/

- /*---------------- Enable FSMC Bank1_SRAM Bank ------------------------------*/

-

-

- FSMC_Bank1->BTCR[0] = 0x00001011;

- FSMC_Bank1->BTCR[1] = 0x00000200;

-

-

- // FSMC_Bank1->BTCR[2] = 0x00001011;

- // FSMC_Bank1->BTCR[3] = 0x00000201;

- // FSMC_Bank1E->BWTR[2] = 0x0FFFFFFF;

-

- // FSMC_Bank1->BTCR[4] = 0x00001011;

- // FSMC_Bank1->BTCR[5] = 0x00000200;

- }

FSMC_SRAM_WriteBuffer(&temp,0x00010001,2);

有哪位大大能指点一下迷津,谢谢。

|

微信公众号

微信公众号

手机版

手机版

这个主要得看STM32F103VCT6有多少根地址线,并且你用了多少根地址线。

超过的,它无法区分是低地址,还是高地址。

从你的现象看,说明你的FSMC_A19到FSMC_A23没有接。

从原理图看,的确没有接。

GPIO_InitStructure.GPIO_Pin = 0xDFB3; //2、3、6、13没管,13对FSMC_A18

GPIO_Init(GPIOD, &GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = 0xFF83; //2、3、4、5、6没管,对应FSMC_A19到A23

GPIO_Init(GPIOE, &GPIO_InitStructure);

但是这样,也是不对呀,从你的配置代码中看到FSMC_A18也没有配。而你实际用了的是A0到A17条地址线,16位数据,一共占用内存地址是512KB呀,也就是0x80000。你说的以1MB为间隔数据重复,这个有点讲不通,如果属实的话,应该是以512KB为单位重复呀。请看一下你的 0x60010001 + 0x80000*N地地址数据。

评分

查看全部评分