问题:在使用定时器输出PWM时,假如此时关闭PWM的输出,其IO口会出现高低电平交替出现的情况!1.代码设置:TIM2->CCER2寄存器设置的是输出使能和输出有效电平为低电平;$ w P# ?/ C0 p9 f% }* H

+ ^; F5 b' `& J; i% k4 ^

- /* Disable the Channel 1: Reset the CCE Bit, Set the Output State, the Output Polarity(low) */

/ o9 b5 N6 I3 n6 P - TIM2->CCER2 &= (uint8_t)(~( TIM2_CCER2_CC3E | TIM2_CCER2_CC3P));4 a; }+ u8 m2 c3 w% f

- /* Set the Output State & Set the Output Polarity */

# Z1 S3 N- k5 G" t" H+ U3 T - TIM2->CCER2 |= (uint8_t)((uint8_t)(0x11 & TIM2_CCER2_CC3E) | (uint8_t)(0x02 & TIM2_CCER2_CC3P));( X. r+ o; j& N

- /* Reset the Output Compare Bits & Set the Output Compare Mode(PWM1) */

* d" ]# V& M* n# v - TIM2->CCMR3 = (uint8_t)((uint8_t)(TIM2->CCMR3 & (uint8_t)(~TIM2_CCMR_OCM)) |<font color="#ff0000"> (uint8_t)0x60</font>);

) b) Y+ z- c3 F5 e& r" E6 G0 R6 @8 M. e3 m3 u% C/ N* D- M0 c3 U

- /* Disable timer2 */6 J9 A4 `1 K Z9 |8 z

- TIM2->CR1 &= (uint8_t)(~TIM2_CR1_CEN);

6 O" F9 d8 y% Z8 {" f - /* Reset the OCM Bits & Configure the Forced output Mode */5 W3 e; [% D9 s, W) ~- V

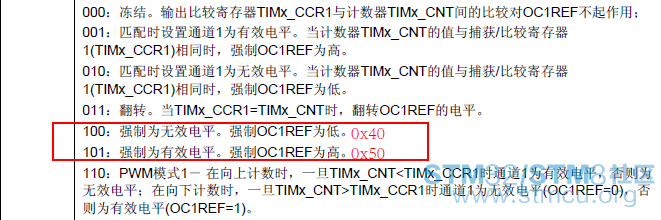

- TIM2->CCMR3 = (uint8_t)((uint8_t)(TIM2->CCMR3 & (uint8_t)(~TIM2_CCMR_OCM)) | <font color="#ff0000">(uint8_t)0x50</font>);

- /* Reset the OCM Bits & Configure the Forced output Mode */; L" g3 z$ S! O& A; M

- TIM2->CCMR3 = (uint8_t)((uint8_t)(TIM2->CCMR3 & (uint8_t)(~TIM2_CCMR_OCM)) | <font color="#ff0000">(uint8_t)0x60</font>);- E1 J4 b3 {9 X" j8 ?; z$ H

- TIM2->CR1 |= (uint8_t)TIM2_CR1_CEN; //产生pwm

5 W- s2 |5 V( P8 c1 Z来自于stm8s参考手册TIMx_CCMR1$ R6 {, }! T7 |, x6 k

|