|

本帖最后由 eefishing 于 2019-2-27 23:00 编辑 * r, d# |) F; l M { h% Q 描述3 s5 O- W) e& q3 o2 { 两个开发板合为为一个:第一个基于STM32的Arduino(“枫叶迷你”兼容)和第二个旋风II FPGA开发板,用来玩VHDL/Verilog。它还兼容“Multicomp”(“Multicomp”是一个模块化的VHDL设计,“运行”一些著名的复古8位CPU由Grant Searle),使选项“运行”容易VHDL SOC与Z80/6809/6502 CPU和I/O,包括高清(在SD)和彩色VDU。0 m4 n$ _8 m: ` \! C ) I4 s5 I0 T" D* ]' h 9 ?4 _( B& X) |, r 硬件概述! C2 C, u+ p+ o6 U* M 6 P* u/ }$ `9 M& A6 B 这就是CPLD趣味板的“自然”演变。这个想法是用廉价和容易找到的组件制作FPGA板,用STM32 Arduino作为FPGA的“刺激发生器”或“伴侣”处理器,用512KB的SRAM和通用I/O作为GPIOs, VGA和PS/2键盘来“运行”HDL SOCs。4 @$ a( q- o6 H1 n7 p4 z' g 更重要的是,它可以选择“运行”轻松地多comp VHDL SOCs具有所需的HW。 8 z4 z, Z; R" W7 y1 P Multicomp是一种模块化的VHDL设计,用于“运行”Grant Searle制造的一些著名的复古8位cpu。

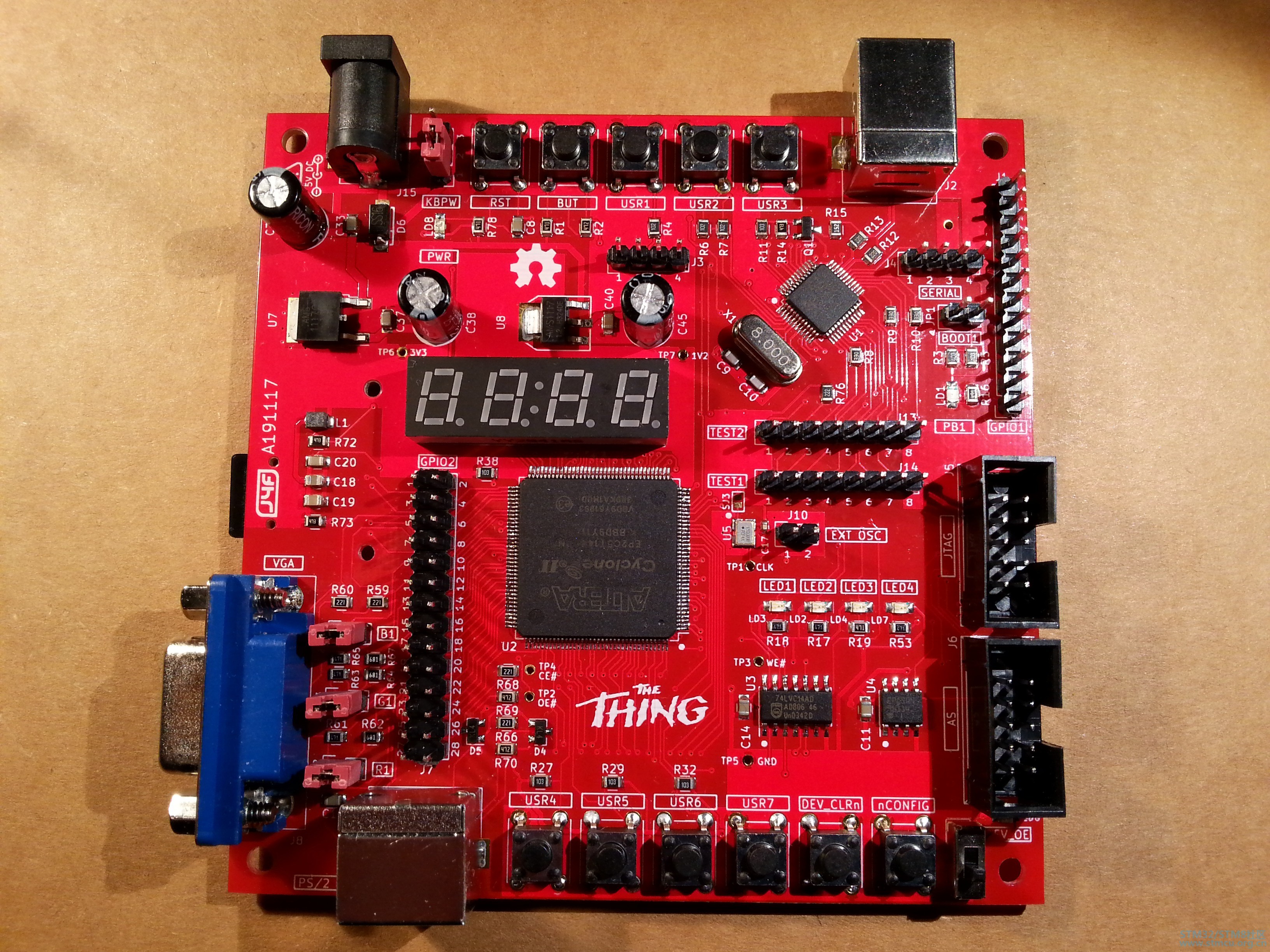

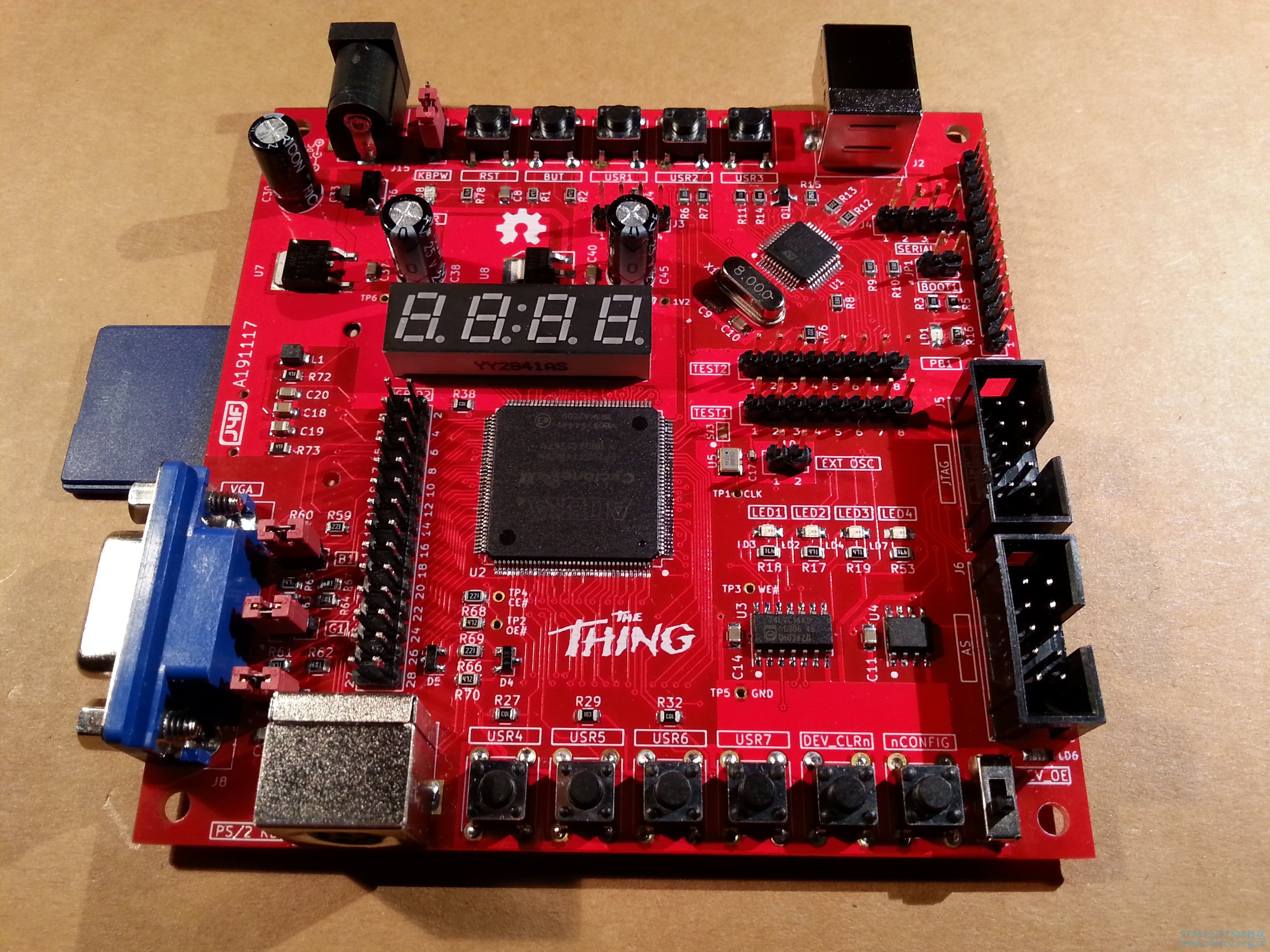

& J4 W, z. ]6 C% w9 r7 u8 g0 d2 U; o 这里是PCB的细节。请注意,下图中的PCB具有ENIG表面光洁度。这不是绝对必需的。您可以使用最便宜的HASL表面处理:

|5 N. y5 K+ l: U' k* w PCB留给选择焊接“遗留”的SD插座(如之前的图片)或微型SD插座,如下图所示:

# m! d1 H* h$ [7 W' a 3 `7 J2 y/ ^8 b6 t1 K0 R) L5 M. w STM32的ARDUINO STM32F103C8T6单片机作为FPGA的“刺激发生器”或“伴侣”单片机,通过USB接口使用友好的Arduino IDE轻松编程。 MCU保留了五个按钮(RST, BUT, USER1-USER3)和一个led (PB1)。% w8 T2 S' B/ M2 |0 B& j ) \4 l6 @% ]/ S7 ~# E 还有一个专用的GPIO连接器(GPIO1)。 l x' U- C8 P4 j- f& q4 f STM32F103单片机的端是“Maple Mini”兼容的,所以可以使用http://www.stm32duino.com提供的STM32F103 Arduino core(更多信息请点击这里)。想了解关于Maple Mini和stm32duino的小故事,请点击这里。 1 ~3 K; t& F$ W+ j+ A0 n; N 您需要首先使用廉价的“St-Link V2”加密狗通过SWD连接器(或者在串行连接器上使用串行usb适配器)来闪存引导加载程序。! R7 N; P7 P1 V! G$ U0 P6 e7 o1 W

THE CYCLONE II FPGA2 t+ F! I8 B1 Q" Y# U 9 v* i* `9 X/ w" B9 R* Y0 ~7 X1 s 为了配置FPGA (EP2C5T144C8N),它使用Quartus II IDE (v13sp1免费版是支持Cyclone II FPGA的最后一个版本)和一个通过JTAG或作为连接器的廉价“USB Blaster”加密狗。 ; S6 h7 {8 |: N9 i4 n) W; R 要将FPGA配置永久存储到eeprom中,您可以使用AS连接器,也可以使用具有SFL IP核心的JTAG连接器,如本Intel视频中所述。

FPGA保留4位7段led显示、4个按钮(USER4-USER7)和4个led (LED1-LED4,前3个为“user”led,最后一个为配置活动指示器)。5 V. h7 u6 G; ]6 x' N! y: Y2 ^ FPGA的一面也有DEV_CLRn按钮来清除所有内部FFs nCONFIG按钮强制配置重载(重启的FPGA),和一个DEV_OE开关强制所有的FPGA别针HiZ(使用DEV_CLRn按钮和DEV_OE开关必须使他们首先在第二第四的IDE)。5 J2 ]8 b" j$ B " h+ M( c! R7 E3 x3 G4 m( h8 P6 r! v 还提供了机载50MHz振荡器,以及用于外部振荡器的连接器。 9 M7 ? K+ ?5 e% ~* g 有13条I/O线“连接”STM32和FPGA,每条线上都有一个由两个连接器(TEST1和TEST2)组成的引脚。这样就可以很容易地用作用域或LA“观察”它们之间交换的信号。 在这13条I/O线路上,单片机端有各种外设(如串行、I2C、SPI)。 2 @: ^! x) l6 I5 n6 n+ w: r 在FPGA端(GPIO2连接器)还有其他22个GPIOs。注意,有些GPIO与VGA、PS/2和SD共享)。 也可以使用Arduino STM32“侧”或FPGA“侧”作为一个独立的开发板,TEST1-TEST2连接器作为普通GPIOs(在HiZ中持有另一个“侧”的插脚)。 ) u8 m; w( x# j6 v * *项目状态* * 4 E# N1 M, D4 z. I6 a 这里必须编写大量文档来解释如何使用它…… # I% n# _; Q. A1 S/ t+ X, i 我还准备了一些可以运行的“一些”Multicomp示例(包括SD图像)。我可能会用github。' n6 U& r D* }: c1 J 如何得到一个PCB* *5 Y- I* y6 L. u4 h 像往常一样,我准备了一个“简单”的链接来获得少量(最少5个)PCB。链接是这个。1 l1 B1 y5 e" f& o% o3 }3 h: F ' v/ y; G9 [; _6 c# Z- f, A: a* } " p {5 {" a+ @; c * *学分和执照* * Multicomp VHDL是基于Grant Searle的原始工作,并以以下许可证发布:6 v1 i l1 _2 N: {) G5 a 下载这些文件时,您必须同意以下内容:我们尊重ROM内容的原始版权所有者。使用任何文件的内容在自己的项目中自由是允许的,但任何出版的材料包含全部或部分的任何文件分发,或来源于我在这里所做的工作将包含确认回我自己,格兰特塞尔,回到这个页面的链接。任何发布或分发的包含本页所有或部分文件的文件必须免费提供。”(http://searle.hostei.com/grant/Multicomp/index.html)。 8 h3 h5 p( f2 f# ?1 H 所有的项目文件(SW和HW)都是在GPL v3下授权的。 $ ?$ h6 }* z% t) j5 n [% A 如果您以任何方式使用本材料,请注明作者(本人  ),我们将不胜感激。 ),我们将不胜感激。5 s9 H0 s6 M1 I6 k1 h7 s* d / E2 ?7 r& u5 n% w' @$ [# Z6 | c 原创:Just4Fun 出处:http://hackaday.io/project/163683-the-thing-fpga-stm32/details - X; c$ u1 I% g + [5 x2 u+ q. z% j, [' k + Y$ w/ H8 V3 v3 d( S - u7 x3 h+ C, b/ `( `/ v |

| 学习下 |

微信公众号

微信公众号

手机版

手机版