.png) STMCU小助手

提问时间:2021-3-2 13:17 /

STMCU小助手

提问时间:2021-3-2 13:17 /

|

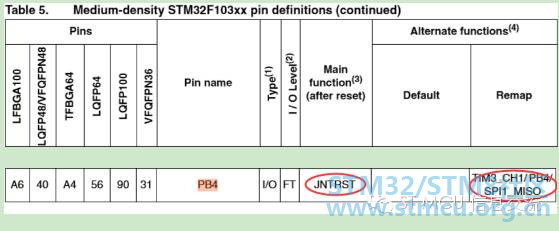

一个关于STM32 GPIO管脚复用冲突的话题 某工程师用STM32F103C8开发产品,用到TIM3的PWM输出功能。他发现TIM3_CH2可以实现PWM【此通道对应的GPIO脚是PB5】;而TIM3_CH1却不能实现PWM【此通道对应的GPIO脚是PB4】。 该工程师在基于ST官方之前提供的标准外设固件库做应用软件设计。 从客户的描述来看,基本可以肯定TIM3的时钟、GPIOB的时钟都已正确使能了。关于TIM3_CH1的PWM初始化代码应该不会有啥问题,除非偶尔的笔误没发现。后来一起查看了相关PWM初始化代码也的确没发现问题。 PB5脚对应的TIM3_CH2可以实现PWM,而PB4对应的TIM3_CH1却无法实现PWM。怀疑该脚是否还有其它的复用了。客户说,PB4他只用来做PWM输出,并无其它功能安排,硬件线路上也无其它连接。 打开芯片数据手册,查看PB4的管脚说明如下:

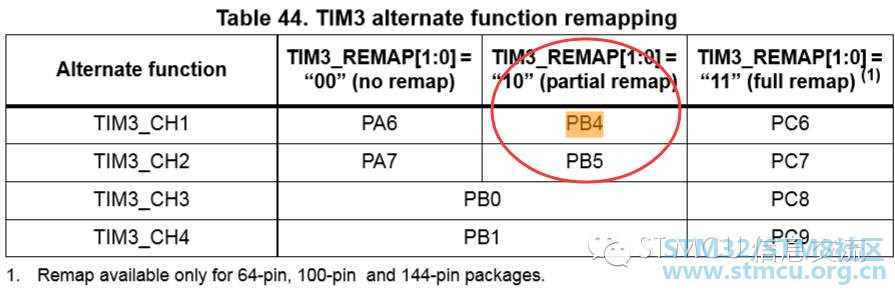

从这里可以看出,PB4脚的复位后的主功能是个特定功能脚,是JTAG口的一个复位脚。如果要用做TIM3_CH1的话得先做REMAP操作才可以。 经与客户工程师沟通,他的确也做了相关REMAP操作,而且REMAP是没问题的。因为PB5也是经过同一REMAP操作后才能成为TIM3_CH2通道的。

既然REMAP没问题,那应该是别的原因。询问该工程师是否使用JTAG调试口,答曰用SWD口,只涉及PBA13/PA14,根本没用到PB4。

查看STM32F1参考手册可以发现PB4及PA13\PA14\PA15\PB3等5个脚在芯片复位后默认的就是专用的调试口,非通用GPIO。现在客户工程师虽然用SWD接口,只用到PA13\PA14两根线,但PB4及PA15、PB3三根线的属性没变,还是专用调试口。如果要把不用的PB4等三根线作为GPIO,还得额外做些相关寄存器配置,即操作AFIO_MAPR寄存器中的SWJ_CFG【2:0】三个位。

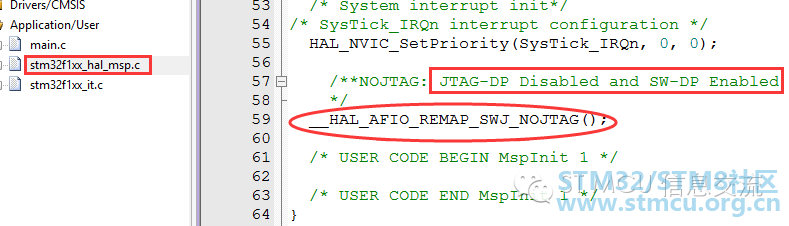

让客户工程师在程序代码里添加有关AFIO_MAPR寄存器的配置代码后,测试基于PB4脚的TIM3_CH1的PWM输出功能,一切正常。看来,问题就出在跟调试口复用的GPIO脚释放问题上。即对于复位后呈现专用调试口的功能脚,欲部分或全部用在GPIO,得额外通过相关软件代码配置来修改其属性,将相关管脚释放为GPIO。 STM32 MCU芯片管脚复用之灵活而复杂是其一特色,增强了管脚使用与安排的灵活性。也正因为这个灵活,经常有人会因为管脚复用的安排遇到些小麻烦。像类似问题,在数据手册里各个管脚的复用功能都一一列出了,然后逐一核对有无多重使用问题也不难找到原因。 不过,如果使用ST公司的STM32CubeMx图形化配置工具来做管脚安排及时钟初始化等就可以避免很多类似上面谈到的繁琐或麻烦。利用STM32CubeMx配置工具,很多初始化的东西都可以依据你的管脚和时钟安排、外设功能的使能等而生成出相应的配置代码,不必手动二次添加配置,让你去专注你的用户应用代码设计与调试。 比方是以上面事例来谈,关于TIM3的功能脚的REMAP、JTAG脚的配置以及项目中用到的各外设的时钟使能、相关GPIO的配置等都可自动生成,不会出现配置代码方面丢这个少那个的问题,使用起来给开发者带来了不少方便,节省了不少时间。

文章出处: 茶话MCU |

微信公众号

微信公众号

手机版

手机版