|

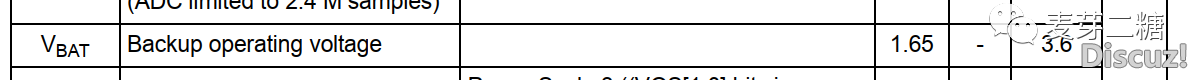

STM32除IO脚的其他引脚功能说明 一、二糖有话说 很多时候我们做stm32硬件设计的时候都是直接用以前的工程将最小系统直接复制过来使用,只需要修改IO脚就好,但是为什么要这么设计却一知半解,今天去了解一下除IO口外其他引脚的功能作用。包括(VBAT, VDD, VSS, VDDA, VSSA, VREF+, VREF-,BYPASS_REG,VCAP, PDR_ON, BOOT0, BOOT1, NRST)。 9 y2 O" H: C& s% x 二、详细介绍 VBAT:备份区供电电压,1.65V≤VBAT≤3.6V。

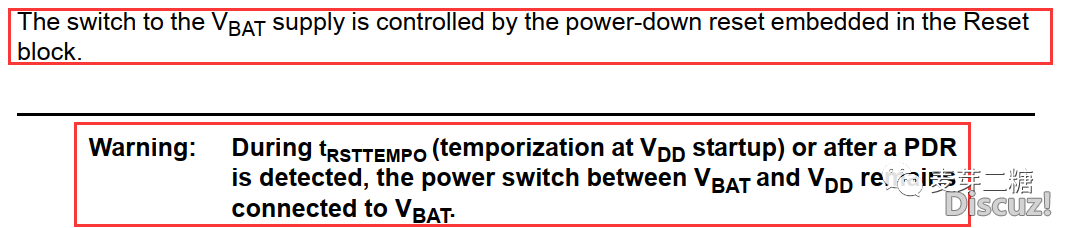

此引脚主要为以下模块供电: 1. RTC实时时钟 2. 外部低速时钟振荡器 3. 备份寄存器和备份SRAM $ l7 B: ^+ _4 [ 为了在VDD断电后(系统断电,设备断电等)保留备份寄存器的内容,可以将VBAT引脚连接到电池或其他备选电源。(我们一般接在超级电容或者电池上)。 VBAT电源的开关由复位模块中内置的掉电复位(PDR)电路进行控制,如下图,在参考手册中可查到。此处有个很关键的问题,等下在PDR_ON引脚处说明。

若应用中没有使用外部电池,建议将VBAT外部连接至VDD。 6 R1 r& V0 y" {% P6 h! I VDD:VDD是指芯片的工作电压,查看数据手册,典型值为3.3V,最小值1.7V,最大值3.6V。

VSS:除特殊说明所有电压都参考VSS,即以VSS为参考地(接电源地)。

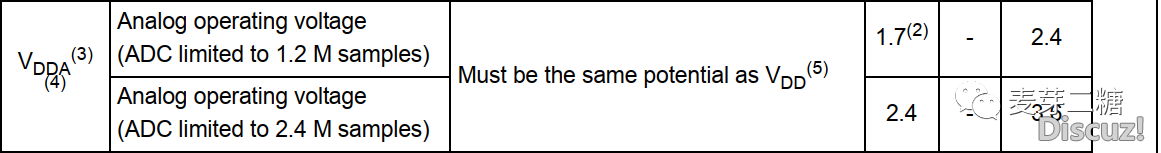

VDDA:独立A/D转换器电源,模拟电路电源。如图所示,VDDA电位要与VDD电位相同,当采样率小于每秒一百二十万次时,1.7V≤VDDA≤2.4V,当采样率超过每秒一百二十万次时,2.4V≤VDDA≤3.6V。

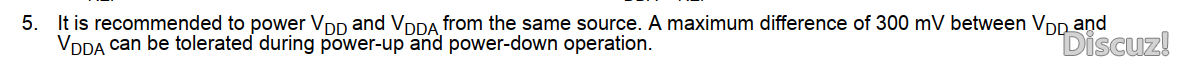

如图所示,官方推荐VDD和VDDA使用同一电源供电,所以我们一般将VDDA通过磁珠连接到VDD引脚上。

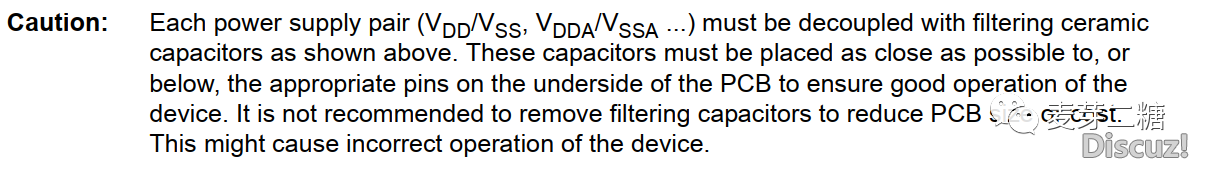

VSSA:与VDDA对应,此引脚与VSS连接即可。 注意:每对VDD/VSS,VDDA/VSSA一定要接滤波电容,并且要靠近芯片引脚放置。

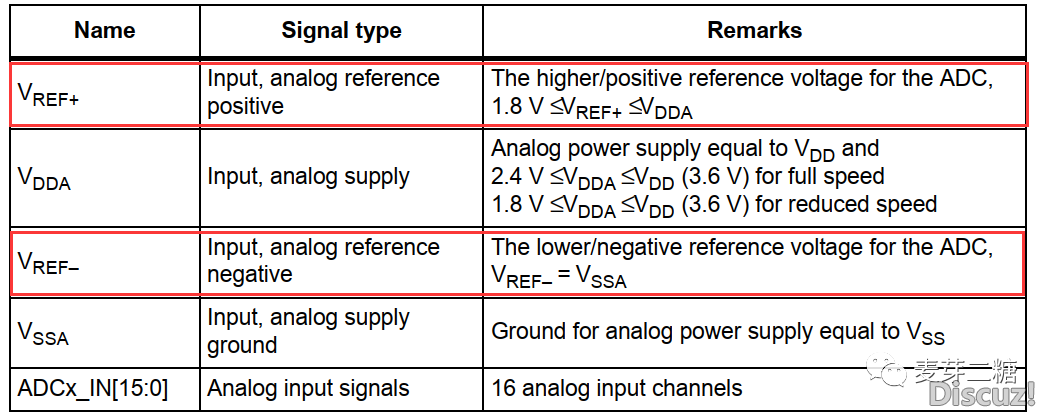

VREF+/VREF-:为模拟参考电压,1.8V≤VREF+≤VDDA。此组引脚在100个以上引脚的封装上才会有。

VREF+,VREF-分别在芯片内部连接到VDDA和VSSA。

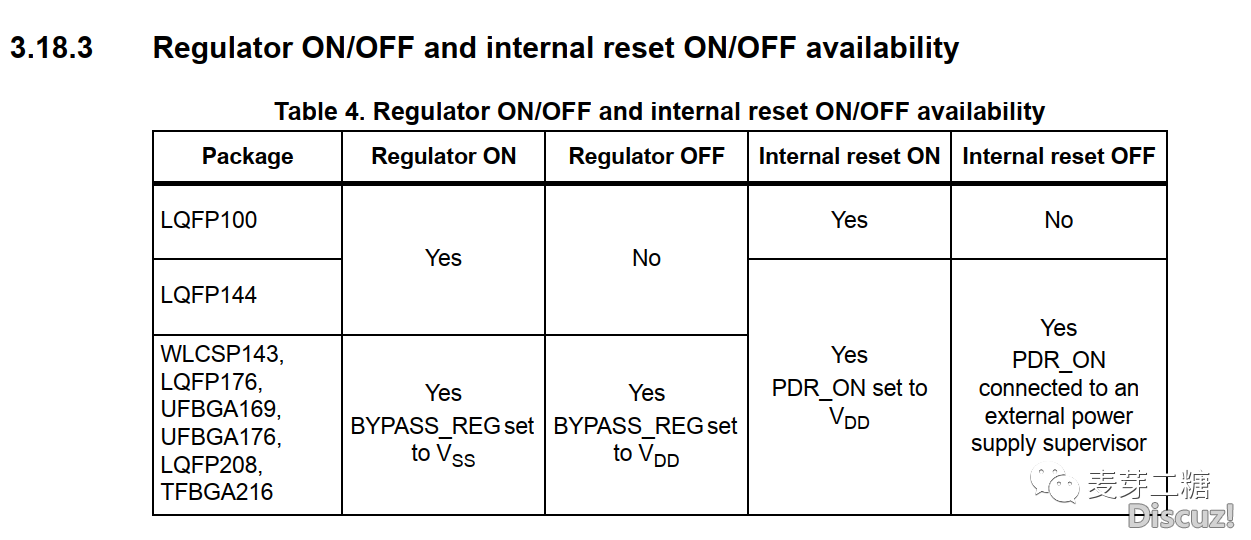

由于系统电压会波动,而我们有些功能对ADC采集精度的要求较高,则会专门设计参考电源电路。如果对精度要求没那么高,VREF+直接接到VDDA上就好。 BYPASS_REG:在有此引脚的封装上,此引脚接地可启用内部稳压调节器,没有引出此脚的芯片,内部默认启动稳压调节器。 9 h$ [3 W7 M7 E

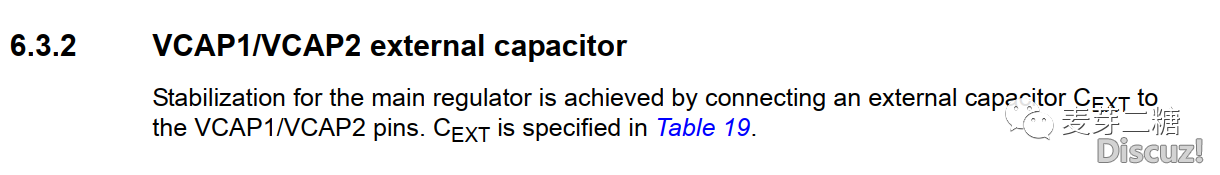

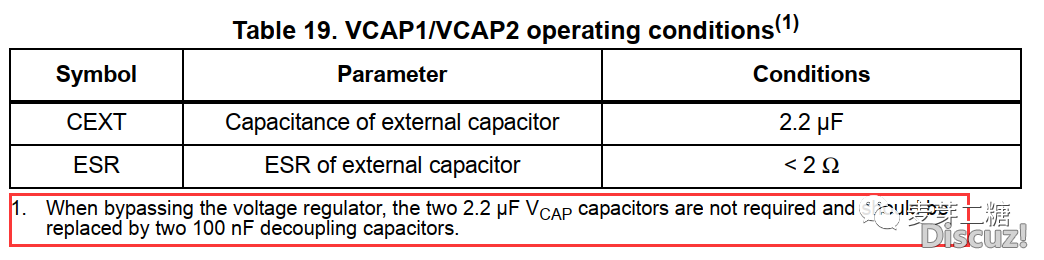

关于内部稳压调节器,当启用时,可通过软件配置三种电源模式 1. 运行模式 2. 睡眠模式 3. 停止模式 : {8 t4 o o3 e6 S4 Z, M VCAP:有的封装没有此引脚,有的只有一个,还有的有两个。

如果芯片内部稳压调节器启用,VCAP引脚外部需要接电容(典型值2.2uF)到地,目的是为了使内部稳压调节器更稳定。 如果此芯片支持关闭稳内部稳压调节器并且将其关闭,那么VCAP引脚接100nF退耦电容到地。

PDR_ON:在有此引脚的封装上,通过将此引脚接到高电平来启用电源监视器,没有此引脚的封装,芯片内部默认启用电源监视器。 & S& C, g3 F5 Z9 d t* T) n X

这是什么意思,经过我的分析,PDR是掉电复位的意思,那么PDR_ON引脚主要是控制开启关闭内部上电/掉电复位的。如果关闭了内部上电/掉电复位,则应该接一个外部电源监视器。 # f8 A$ p/ T# P5 p0 S/ P9 W+ u

内部复位关闭以后会影响到如下功能: 1. 内部的上电/掉电复位失能。 2. 欠压复位(BOR)电路必须禁用。 3. 嵌入式可编程电压检测(PVD)功能失能。 4. VBAT功能不再可用,并且VBAT要接到VDD引脚。

在上边介绍VBAT引脚的时候说有一个很关键的问题,在此说明一下,如果PDR_ON引脚接地了,那么内部掉电复位功能禁用,而内部掉电复位电路控制着切换VBAT电源,所以PDR_ON引脚接地,会导致VBAT功能不再可用。 关于BYPASS_REG和PDR_ON引脚总结:

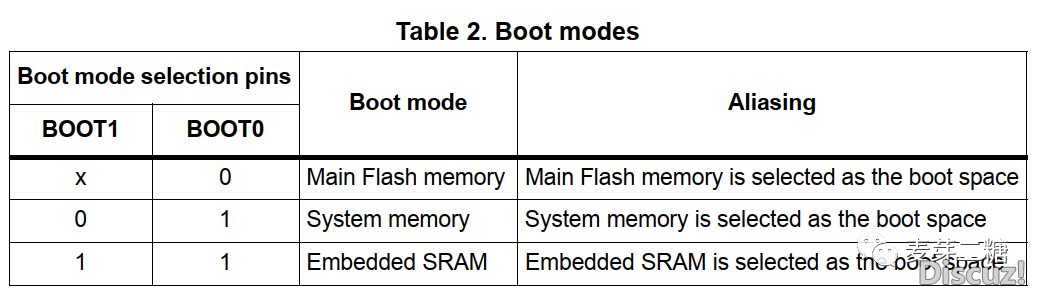

BOOT0/BOOT1:主要是配置启动模式。 , M2 u+ W) R4 X5 F9 B2 r

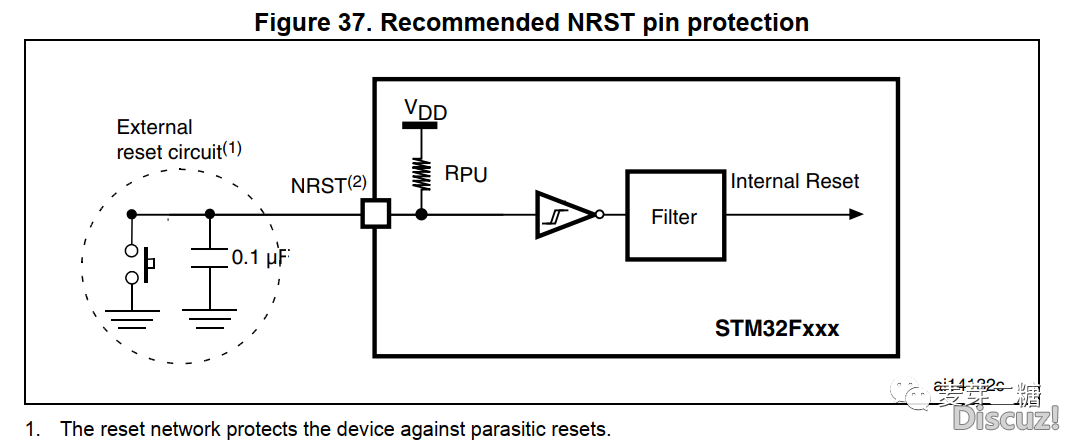

三种启动模式说明: MainFlash memory:程序从flash引导启动。 Systemmemory:ST出厂的boot引导程序存放位置。 EmbeddedSRAM:从SRAM引导启动程序。 我们一般会把自己boot程序写到flash中,所以设计电路时只将BOOT0接地就可以了。而BOOT1可以当作普通IO口使用。 NRST:芯片复位引脚,我们一般会用RC上电复位,为了保证系统稳定性我们也会使用专门的复位芯片。

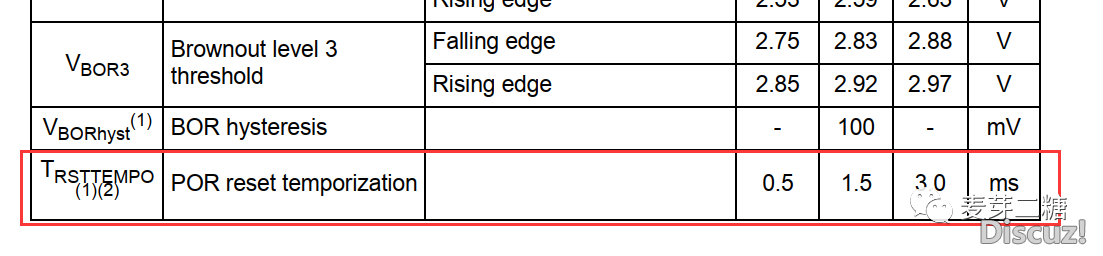

设计外围电路时主要需考虑上电复位时间,从而选用合适的RC值。如图所示,至少要保持1.5ms到3ms的复位时间。

我们一般会使用10K电阻配一个10uF电容。粗略计算,复位时间t=RC=10K*10uF=0.1s。100ms远大于3ms。 参考来源: 1. 《stm32数据手册》 2. 《stm32参考手册》 3. 《AN4488_STM32F4xx MCU硬件开发入门》 文章出处: 麦芽二糖 |