使用LL库编程时,发现外设中断即使使能也进不了中断。

一般外设都会有自己的寄存器来控制中断的开关,比如ADC 中断使能寄存器 (ADC_IER),但是,将里面相应的位置位后,中断仍然不能相应。

这是因为总的NVIC开关没有打开。这点也好理解。有过STM32开发经验的人都知道,NVIC有开关来控制外设的中断使能。但是在LL库如何实现呢?

翻遍了LL库并没有相应的函数。因为NVIC属于CORTEX内核的东西,外设函数是触摸不到的。(而HAL库是有类似的函数的)

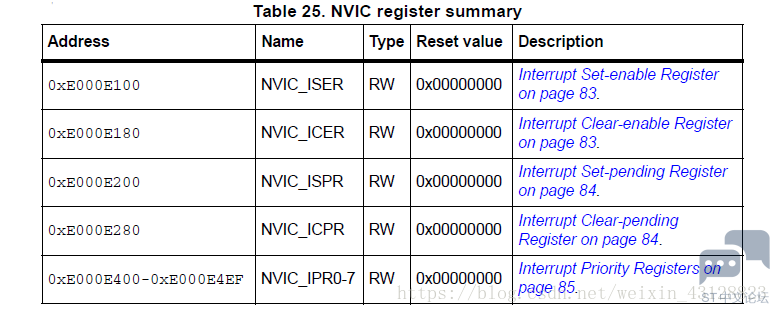

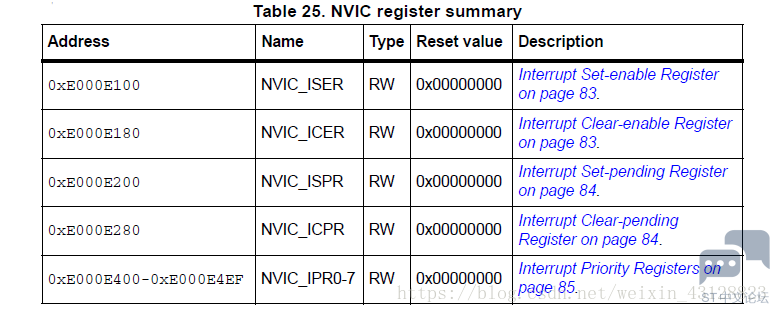

以下是NVIC寄存器

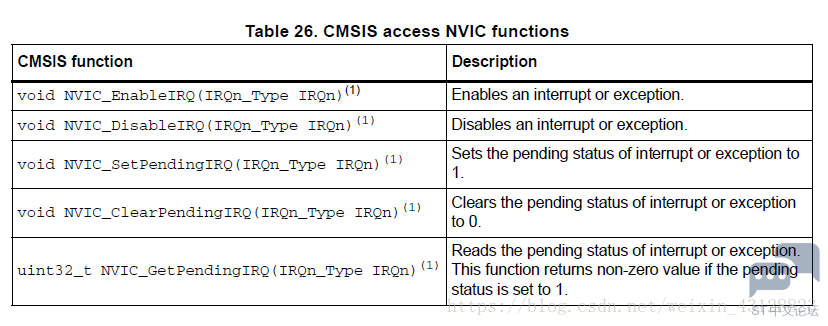

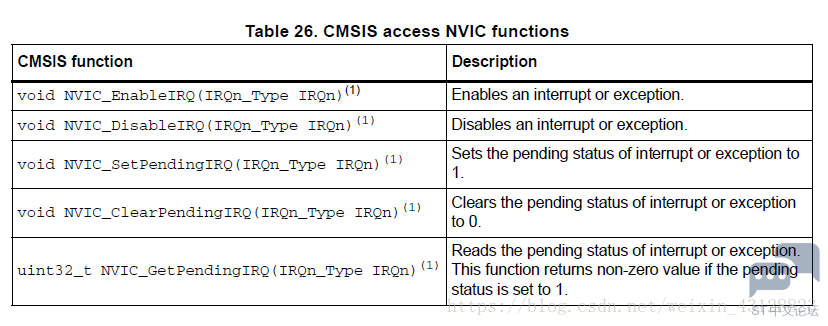

下图是对NVIC操作的函数

下面是各个中断的序号

- /** @addtogroup Peripheral_interrupt_number_definition

- * @{

- */

- /**

- * @brief stm32l011xx Interrupt Number Definition, according to the selected device

- * in @ref Library_configuration_section

- */

- /*!< Interrupt Number Definition */

- typedef enum

- {

- /****** Cortex-M0 Processor Exceptions Numbers ******************************************************/

- NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

- HardFault_IRQn = -13, /*!< 3 Cortex-M0+ Hard Fault Interrupt */

- SVC_IRQn = -5, /*!< 11 Cortex-M0+ SV Call Interrupt */

- PendSV_IRQn = -2, /*!< 14 Cortex-M0+ Pend SV Interrupt */

- SysTick_IRQn = -1, /*!< 15 Cortex-M0+ System Tick Interrupt */

- /****** STM32L-0 specific Interrupt Numbers *********************************************************/

- WWDG_IRQn = 0, /*!< Window WatchDog Interrupt */

- PVD_IRQn = 1, /*!< PVD through EXTI Line detect Interrupt */

- RTC_IRQn = 2, /*!< RTC through EXTI Line Interrupt */

- FLASH_IRQn = 3, /*!< FLASH Interrupt */

- RCC_IRQn = 4, /*!< RCC Interrupt */

- EXTI0_1_IRQn = 5, /*!< EXTI Line 0 and 1 Interrupts */

- EXTI2_3_IRQn = 6, /*!< EXTI Line 2 and 3 Interrupts */

- EXTI4_15_IRQn = 7, /*!< EXTI Line 4 to 15 Interrupts */

- DMA1_Channel1_IRQn = 9, /*!< DMA1 Channel 1 Interrupt */

- DMA1_Channel2_3_IRQn = 10, /*!< DMA1 Channel 2 and Channel 3 Interrupts */

- DMA1_Channel4_5_6_7_IRQn = 11, /*!< DMA1 Channel 4, Channel 5, Channel 6 and Channel 7 Interrupts */

- ADC1_COMP_IRQn = 12, /*!< ADC1, COMP1 and COMP2 Interrupts */

- LPTIM1_IRQn = 13, /*!< LPTIM1 Interrupt */

- TIM2_IRQn = 15, /*!< TIM2 Interrupt */

- TIM21_IRQn = 20, /*!< TIM21 Interrupt */

- I2C1_IRQn = 23, /*!< I2C1 Interrupt */

- SPI1_IRQn = 25, /*!< SPI1 Interrupt */

- USART2_IRQn = 28, /*!< USART2 Interrupt */

- LPUART1_IRQn = 29, /*!< LPUART1 Interrupt */

- } IRQn_Type;

例如将ADC1中断使能,除了对ADC1内部的相应中断位(ADC_IER)使能外,还需要使用下列语句才可以:

NVIC_EnableIRQ(ADC1_COMP_IRQn);

|

.png) STMCU小助手

发布时间:2021-11-19 22:00

STMCU小助手

发布时间:2021-11-19 22:00

微信公众号

微信公众号

手机版

手机版