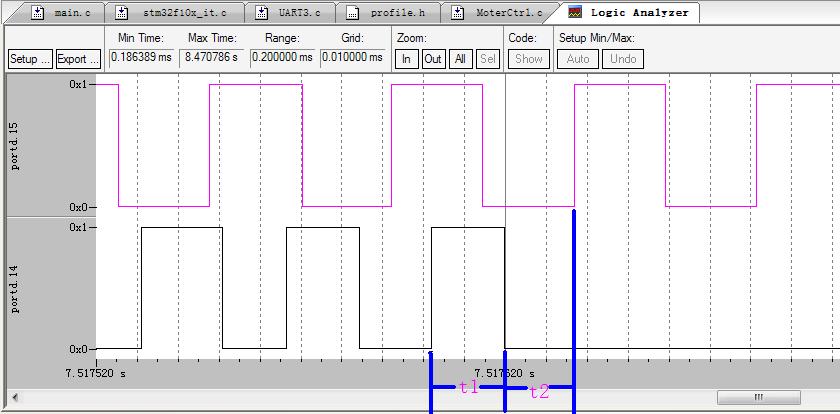

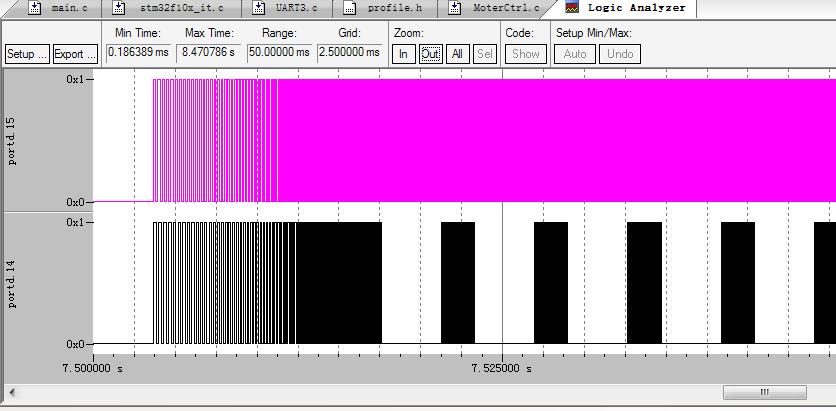

我想用TIM4的输出比较模式来控制两路步进电机,将TIM4设置为输出比较模式,在比较中断中修改相应的比较值来输出两路脉冲信号,可是发现输出的脉冲信号会出现丢失的现象,如下图所示,我仔细分析了一下发现,脉冲丢失出现的地方t1=t2,也就是说两路比较中断接近于同时到来时就会出现这种情况,请问同一定时器的输出比较中断同时到来是处理器内部是如何处理?好像并没有这样对应的优先级设置,望高手指导

|

微信公众号

微信公众号

手机版

手机版

RE:定时器输出比较问题

RE:定时器输出比较问题

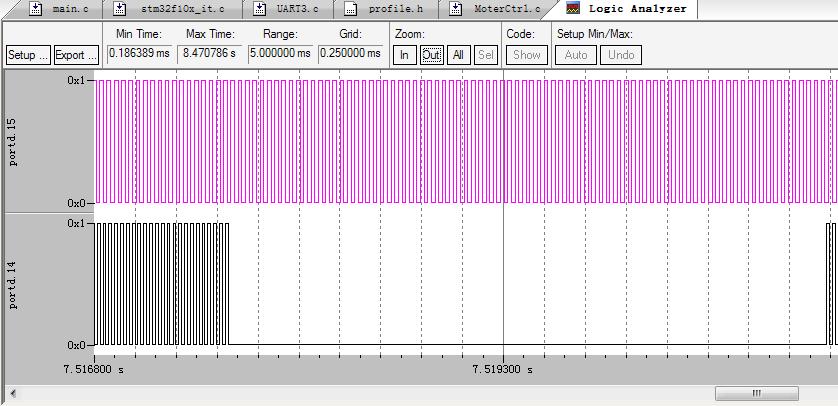

当我使用库函数TIM_ClearITPendingBit(TIM4, TIM_IT_CC4)清零第4通道中断标志位时,第三通道的比较中断刚好到达,硬件上会置位第3通道的中断标志位,而这两个通道的中断标志位在同一个寄存器TIM4_SR中,这样造成了紊乱,清标志位的时候会把两个通道的中断标志位都清掉。

TIM_ClearITPendingBit(TIM4, TIM_IT_CC4)函数的具体实现如下:

TIMx->SR &= (u16)~TIM_IT;//这是其中的有效执行语句,TIM_SR是状态寄存器,这条语句执行前,TIMx->SR==0x19;TIM_IT ==0x10;

然而执行完的结果却是 TIMx->SR==0x01,同时清掉了两位

请高手帮忙分析,给出解决办法 跪求!!!!!!!!!!!!

RE:定时器输出比较问题

请问,你是如何判断执行TIM_ClearITPendingBit之前和之后TIMx->SR的内容?最好能够在调用TIM_ClearITPendingBit之前读出TIMx->SR并保存在一个变量中,调用之后再读出TIMx->SR并保存在另一个变量中,这段过程中不要设置断点也不要单步调试,直接正常运行,然后再查看比较两个变量内容。

RE:定时器输出比较问题