|

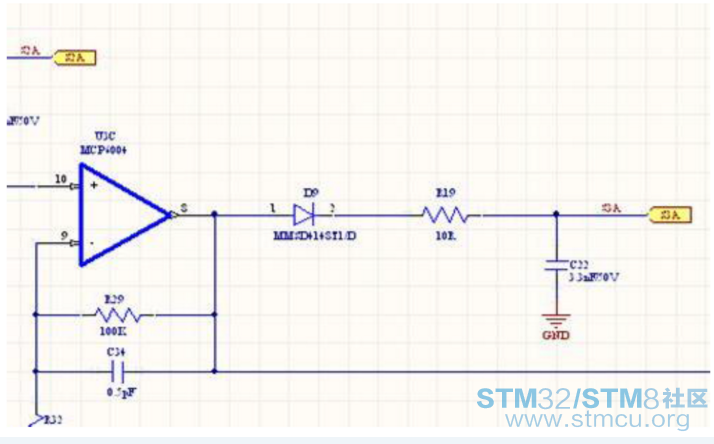

ADC 连续模式采样浮空引脚问题 前言 本篇讨论了一个由ADC 连续模式下采样浮空引脚出现的问题,分析了其原因。 问题: 某用户使用F0 产品进行设计。在使用ADC 采样时,发现当工作于连续模式时,即使外部信号为零时, 依然采到一个数值,近似1/2VDD(此处Vref+和VDD 接在一起)。 相关部分原理图如下:

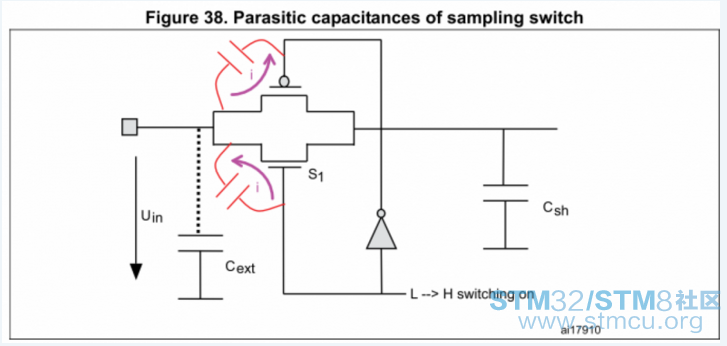

分析: 分析上图,可知当跟随器输出为高时,D9 导通,IO 上处于固定的电平;当跟随器输出为0 时,由于 D9 的存在 IO 口实际处于Floating 状态。此时,采样此通道上电压似乎应当是一个不确定的值才对。 在应用笔记AN2834 中,有一个关于ADC 的图:

当处于连续模式时,开关S1 会始终打开,它的两个内部寄生电容(图中红色部分)会被充电。这两个 内部寄生电容的电荷继而会被转移到采样电容Csh 上,从而使得采样数值并非为0。此时采样得到的 数值是没有意义的,因为并不能反应该引脚上真正的电压,而这个看似存在的电压也没有驱动能力。 进一步分析,原理图中的D9 可以去除。这样,当原先D9 截止时,将使得该引脚处于浮空状态;而去 除后,该引脚将会被拉到低,从而采样得到一个稳定的有意义的值。 文档下载地址: https://www.stmcu.org.cn/document/list/index/category-1037 实战经验汇总: https://www.stmcu.org.cn/module/forum/thread-576401-1-1.html |

微信公众号

微信公众号

手机版

手机版