|

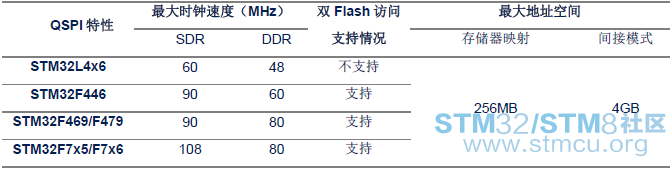

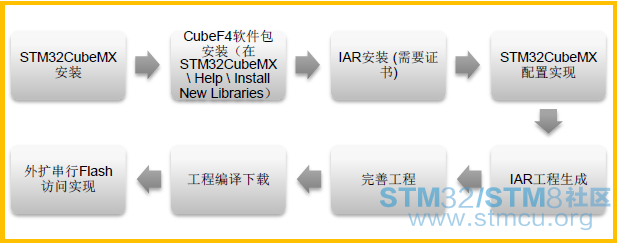

利用 QuadSPI外扩 串行 NOR Flash的实现 前言 STM32提供了灵活多样的外扩存储器访问实现。本文中,介绍如何利用QSPI (QuadSPI) 外扩串行NOR Flash存储器。首先对QSPI接口功能特性进行介绍,然后分别介绍硬件设计和软件开发。并基于STM32CubeMX,提供访问MICRON N25Q128A13EF840F的实现参考。 一 实现环境 开发板:STM32F469G-DISCO 开发库:STM32CubeF4 v1.16.0 STM32CubeMX: v4.22.0 集成开发环境:IAR v7.70.1.11486 实现过程在STM32F469I-DISCO板上展开,利用板上已有的串行NOR Flash存储器(MICRON N25Q128A13EF840F)。呈现整个开发涉及环节。在本文中,首先根据QSPI接口,介绍QSPI与外扩串行存储器硬件连接。另外,Cube软件包中包含QSPI实现例,在本文对库中实现的QSPI例不做讨论,读者也可参考这些QSPI例进行设计。本文围绕由STM32CubeMX生成的工程,介绍如何实现对外扩串行NOR Flash存储器的访问。 二 QSPI介绍 在呈现QSPI访问外扩Flash的实现例前, 需要对QSPI有一定的了解,在此对QSPI进行简短的介绍。更多内容请参考AN4760。 QSPI(Quad-SPI)支持四线串行访问形式。同时,QSPI支持传统SPI和Dual-SPI模式,Dual-SPI模式支持两线串行访问。与FMC/FSMC比较,QSPI支持更低成本、更小封装外部串行Flash存储器,更少的IO引脚占用,有效减少PCB面积,降低PCB设计复杂度。 QSPI在不同系列STM32产品线的支持情况(仅部分罗列,未涵盖所有支持型号)。

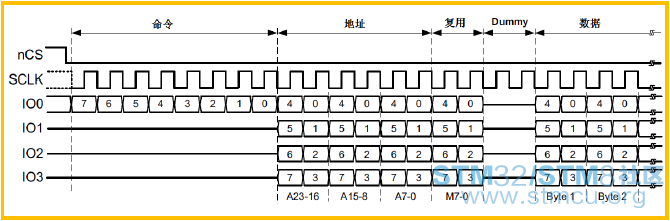

QSPI接口提供了灵活可配置的5个阶段,如下图所示(仅用于理解阶段构成,时序图根据配置不同存在差异)。分别是命令阶段、地址阶段、复用字节阶段、Dummy阶段和数据阶段。可以根据外扩Flash中命令时序对不同阶段进行配置。后续会以实例进行呈现。更多内容请参考AN4760。

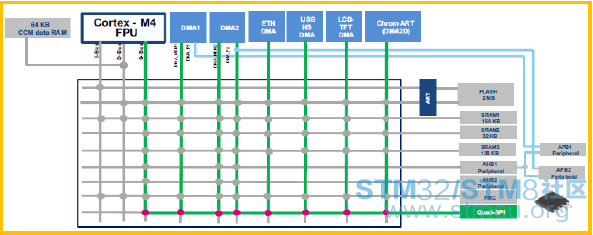

QSPI支持三种模式,分别是: 间接模式---所有操作通过QSPI寄存器实现,类似于传统SPI,可以使用阻塞模式、中断模式或者DMA模式进行读写等访问。本文中提供的实现例为间接模式下的实现。 状态轮询模式---接口自动轮询指定寄存器,直到回读寄存器内容与指定条件匹配。可应用于状态检测,从而实现忙等待等效果。本文不对此模式进行实现介绍,应用实现可参考Cube软件包中QSPI例程。 存储器映射模式---外扩Flash被视为内部存储器,支持AHB主器件直接访问,CPU能够直接运行位于QSPI存储器的执行代码。内部系统架构如下图所示(以STM32F469/F479为例)。本文不对此模式进行实现介绍,应用实现可参考Cube软件包中QSPI例程QSPI_ExecuteInPlace。

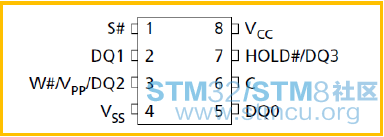

三 QSPI外扩串行Flash实现例 3.1 串行Flash介绍 以MICRON N25Q128A13EF840F为例,更多细节请参考存储器手册。N25Q128A13EF840F引脚图、时序图和电气参数来源于N25Q128A13 手册文档。 支持协议: SPI, Dual I/O(对应Dual-SPI), Quad I/O(对应Quad-SPI) 支持访问模式: 单线访问、双线访问、四线访问,得益于 QSPI接口的灵活可配性,三种访问模式全部支持。 供电电压范围: 2.7 ~ 3.6V 最大时钟频率: 108MHz 存储空间: 128Mb (16MB) 器件引脚示意图如下所示。由两根电源引脚和六根QSPI信号线构成。

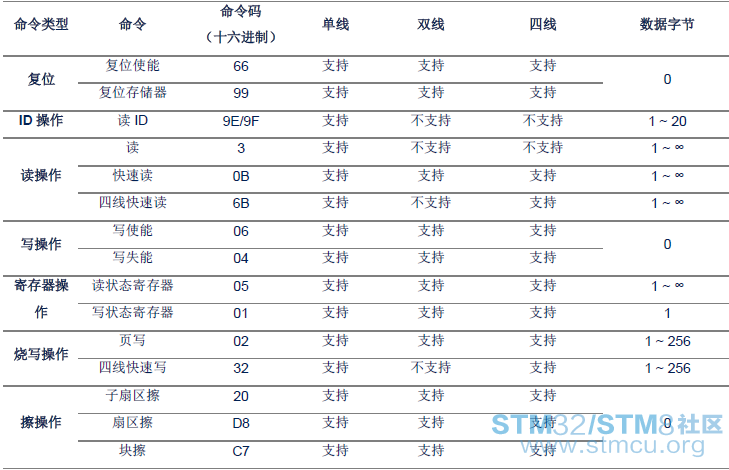

下表为存储器N25Q128A13xxx命令(未列出全部命令)。通过下表可知,存储器提供了灵活的访问实现形式,而结合同样灵活可配的QSPI接口,能够实现存储器命令全支持。而本文仅为提供设计思路,呈现了部分命令在QSPI上的实现。

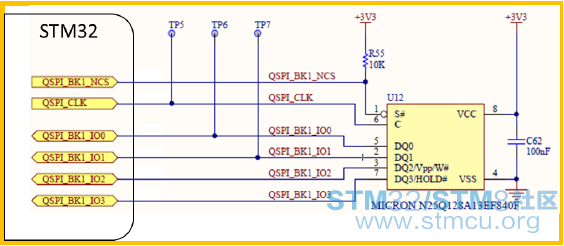

其中,默认读写默认3字节地址,四线快速读命令默认Dummy 周期数为8。 3.2 硬件设计 涉及到的信号线少,硬件设计简单,只需直接将QSPI的六根信号线与存储器连接即可。考虑到可测性,可以增加串行电阻或者测试点。硬件电路图如下所示。

QSPI接口PCB设计遵循如下几点,更多硬件设计内容请参考AN4488。 a. 线阻 50Ω ± 10% b. 最大线长 < 120mm c. 避免在不同信号层走信号线 d. 时钟线至少离其他信号线3倍线宽距离 e. 数据信号线长差 ≤ 10mm f. 避免时钟线采用蛇形走线,同时尽量减少数据线上过孔。 3.3 软件开发流程

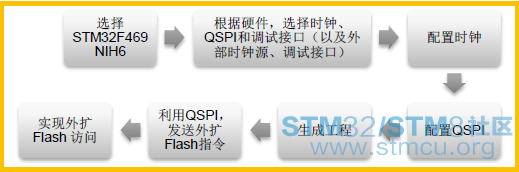

3.4 软件实现例 在环境搭建完成后,就可以利用STM32CubeMX根据硬件连接情况,进行QSPI配置,获取IAR工程。具体软件实现流程如下。

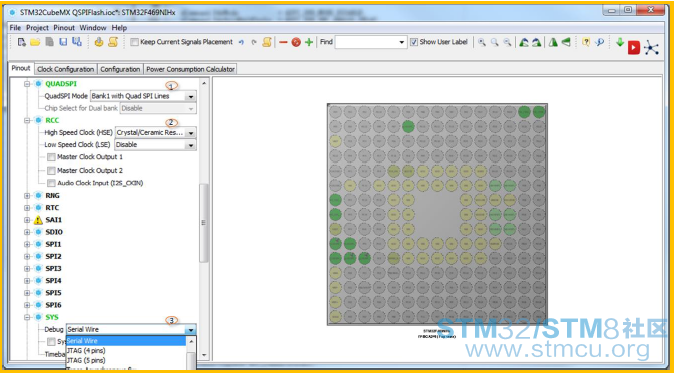

a. 利用STM32CubeMX生成IAR工程 打开STM32CubeMX---点击”New project”---在”Part Number Search’中输入STM32F469NI---点击”MCUs Liast”中出现的STM32F469NIHx---点击“Start Project” 此时,基于STM32F469NIHx的STM32CubeMX工程被打开。 如下,根据STM32F469I-DISCO板硬件连接情况(QSPI NCS, CLK, Q0, Q1, Q2, Q3对应PB6, PF10, PF8, PF9, PF7, PF6;外部高速晶振为8MHz无源晶振;调试接口采用SWD接口,其中SWCLK, SWDIO对应PA14, PA13): 选择” QuadSPI”为”Bank1 with Quad SPI Lines”(注:也可在开发过程中,先用STM32CubeMX查看QSPI接口对应的IO引脚,进行硬件开发) 。 注: 在如上选择后,右侧引脚图中QSPI对应的引脚会呈现绿色显示。需要根据电路图中所连接的QSPI引脚,进行复用引脚确认。例如,在默认情况下,QSPI IO0对应到PC9引脚,而STM32F469I-DISCO板上的QSPI IO0与PF8连接,并非PC9。所以,需要在右侧引脚图中,按住Ctrl键,左键在PC9引脚按下,拖动至PF8处,松开左键和Ctrl键,实现IO0引脚的关联。 选择“High Speed Clock(HSE)”为“Crystal/Ceramic Resonator”。 选择”Debug”为”Serial Wire”

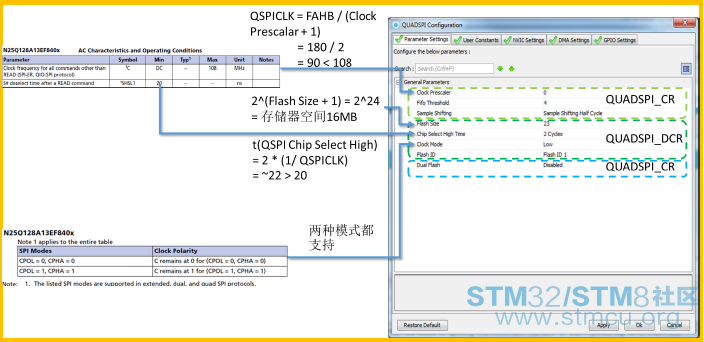

时钟配置如下图所示。设置输入时钟频率为8MHz 选择”HSE”做为PLL倍频时钟源 选择”PLLCLK”做为主频时钟源 设置 “HCLK”为180MHz (FAHB 为180MHz) 点击 Enter键,自动生成对应主频的时钟参数(仅提供时钟配置参考,并不限制一定要设置180MHz主频)。

QSPI配置如下图。参数的配置需要与存储器参数匹配。 • FIFO Threshold(FIFO阈值) 配置为4,并不严格要求。 • Smaple shift 选择“Sample shifting half cycle”。延后半个时钟,获取数据线上数据。可以使用在由于线路设计,数据信号存在较大延迟的场景。

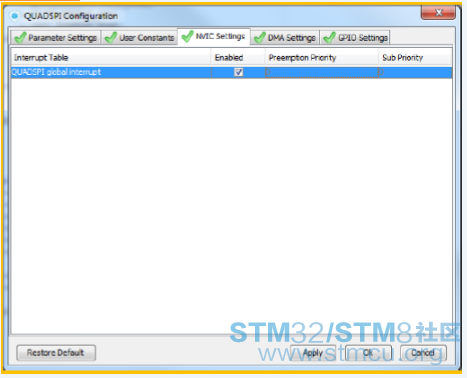

使能QSPI中断。

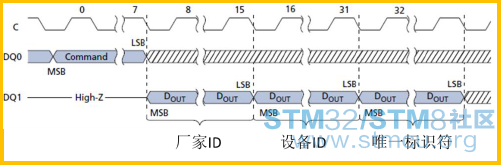

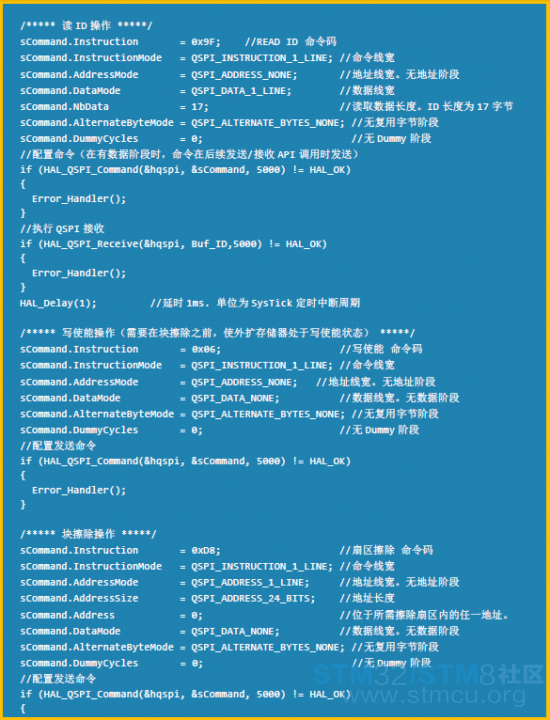

点击菜单栏”Project”---“Settings”---设置”Project Name” , “Project Location” 和 “Toolchain / IDE” 。其中“Toolchain / IDE”设置为EWARM以便生成对应IDE的工程。其他选项保持默认。 点击菜单栏”Project”---“Generate Code”---等待IAR工程生成,出现”Code Generation”界面---点击”Open Project”打开工程。 b. 完善工程。 由上述步骤获得的IAR工程中,包含了时钟配置及QSPI接口的初始化。对于外扩Flash的操作,还需要 添加外扩Flash支持的命令进行操作。N25Q128A13EF840F支持的部分命令可参见本文3.1小结。 在这里出于简化考虑,仅提供了阻塞式读取ID,擦除Flash,块写和快读操作的实现。更多实现模式,可以参考Cube软件包中提供的QSPI例程。 在N25Q128A13EF840F手册中提供了读ID命令时序,如下图所示。

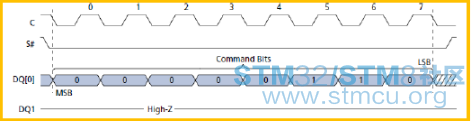

由时序图可知,读ID时序构成: 命令阶段 + 数据阶段。命令阶段和数据阶段线宽都为1,读ID命令码为0x9E或者0x9F,ID数据长度为17字节。 在N25Q128A13EF840F手册中提供了写使能命令时序,如下图所示。

由时序图可知,块擦除时序仅有命令阶段。命令阶段线宽为1,写使能命令码为0x06。(注:这里仅呈现了单线命令模式的实现。除此之外,STM32 QSPI接口和外扩存储器支持双线、四线模式)。 在N25Q128A13EF840F手册中提供了扇区擦除命令时序,如下图所示。

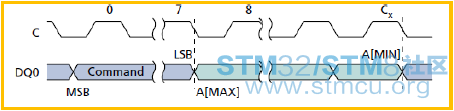

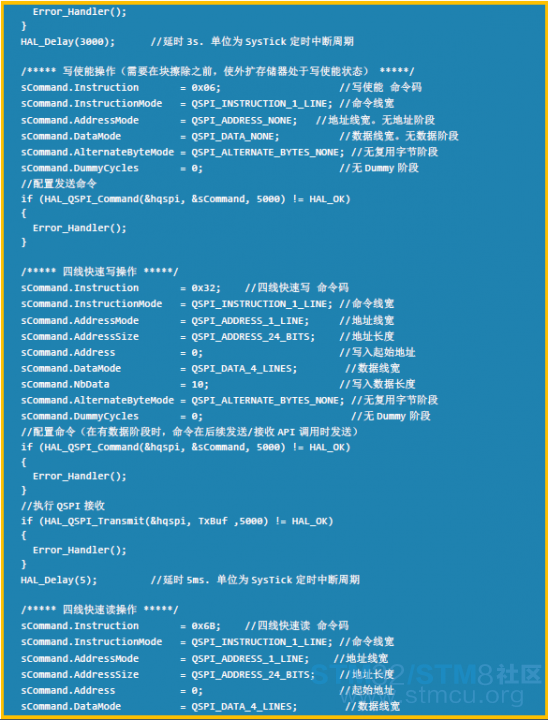

由时序图可知,扇区擦除时序构成:命令阶段+地址阶段。命令阶段和地址阶段线宽为1,扇区擦除命令码为0xD8。其中地址为24-bit,任一位于需要进行擦除操作的扇区范围内地址都有效。在此简单选择扇区0进行擦除,选择地址为0。(注:这里仅呈现了单线命令模式的实现。除此之外,STM32 QSPI接口和外扩存储器支持双线、四线模式)。 在N25Q128A13EF840F手册中提供了四线快速写命令时序,如下图所示。

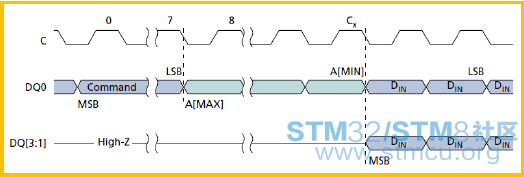

由时序图可知,四线快速写命令时序构成:命令阶段+地址阶段+数据阶段。命令阶段和地址阶段线宽为1,数据阶段线宽为4,四线快速写命令码为0x32。其中地址为24-bit,对应写入起始地址。(注:这里仅呈现了单线命令模式的实现。除此之外,STM32 QSPI接口和外扩存储器支持双线、四线模式)。 在N25Q128A13EF840F手册中提供了四线快速读命令时序,如下图所示。

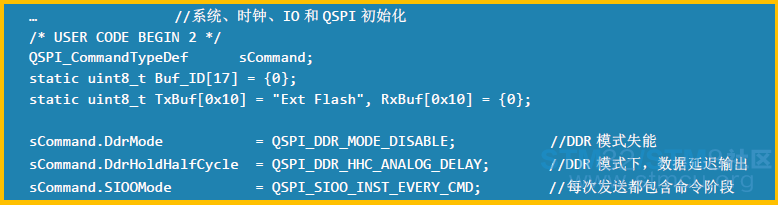

由时序图可知,四线快速读命令时序构成:命令阶段+地址阶段+数据阶段。命令阶段和地址阶段线宽为1,数据阶段线宽为4,四线快速读命令码为0x6B。其中地址为24-bit,对应写入起始地址。四线快速读命令默认Dummy cycles为8。(注:这里仅呈现了单线命令模式的实现。除此之外,STM32 QSPI接口和外扩存储器支持双线、四线模式)。 在main.c \ main函数中,增加代码如下。

四 小结 STM32的QuadSPI接口灵活可配,对于命令阶段、地址阶段、复用字节阶段、Dummy阶段和数据阶段都可以进行配置。基于这种灵活性,能够实现市面上SPI、Dual IO、Quad IO的串行Flash支持。但出于简化考虑,QSPI支持的中断访问及DMA访问等更多功能没有在本文进行介绍,更多实现可以参考ST提供的Cube软件包中的QSPI例程。另外,不同厂家的串行Flash命令及操作实现略有差异,具体以采用的Flash文档描述为准。 文档下载1>> 文档下载2>> 更多实战经验>> |

微信公众号

微信公众号

手机版

手机版

mark一下