|

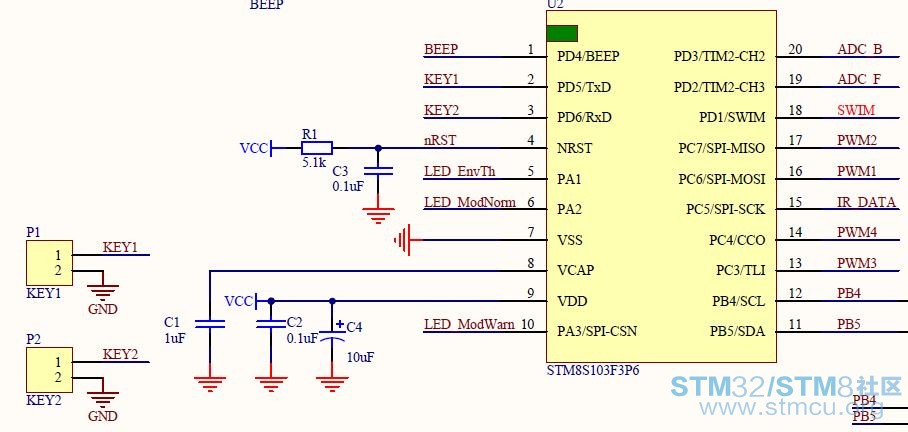

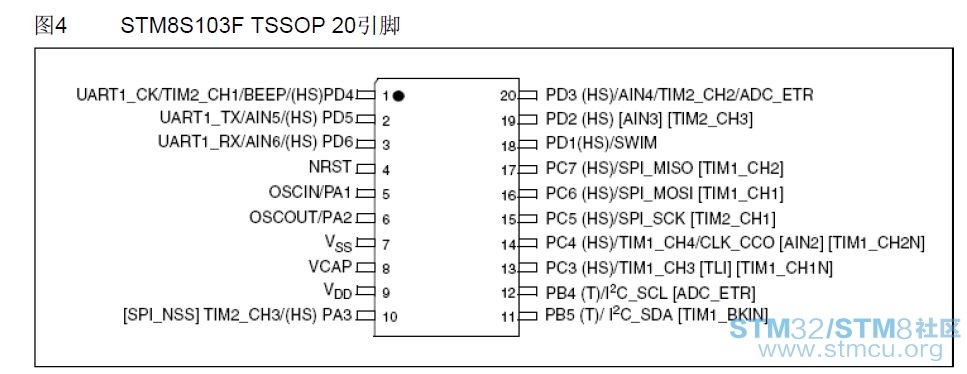

本帖最后由 iyumi 于 2018-8-20 10:12 编辑 用接口PD2和PD3作为ADC的输入,PD5,PD6做为key1和key2的输入

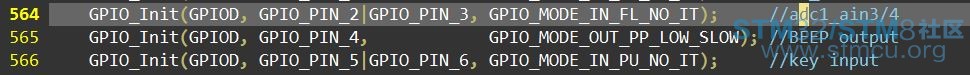

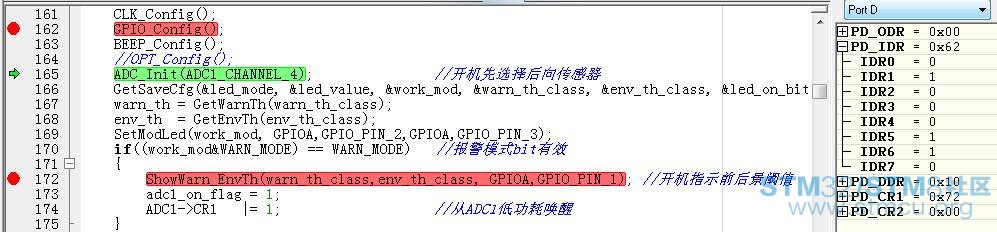

GPIO初始化:

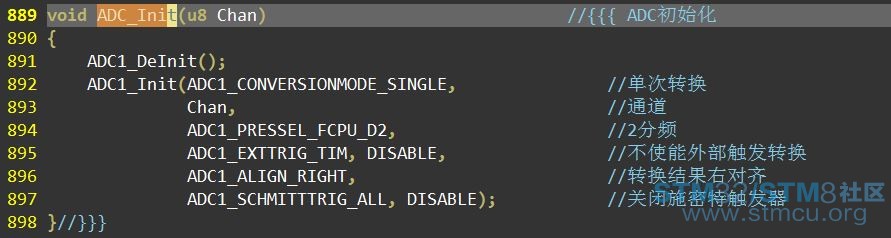

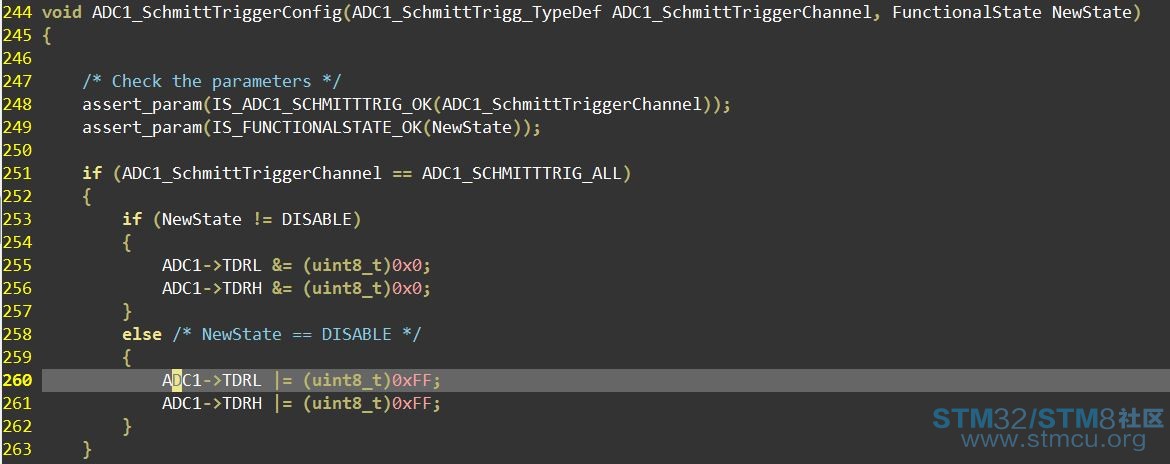

ADC初始化,897行,关闭全部施密特触发器

ADC初始化会执行到下边的260行

执行前,PD5与PD6都是高电平

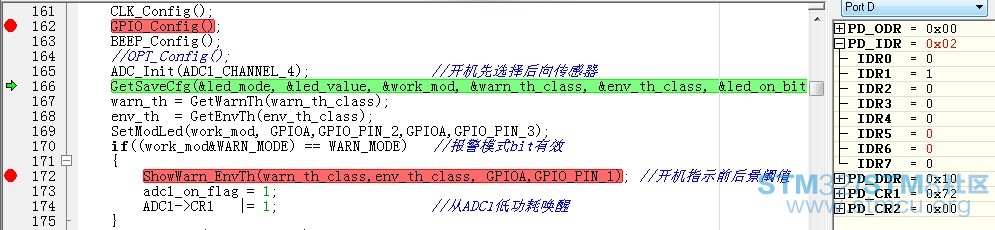

执行后,PD5和PD6都变成了低电平并且不会再变为高

把关闭全部施密特触发器改为关闭对应管脚的施密特触发器就不会把PD5和PD6管脚拉低了,但是没搞明白: 1、让ADC1->TDRL = 0x0FF与PD5和PD6有什么关系,为什么PD5和PD6这两个口的电平会被拉低呢? 2、施密特触发器有什么用,关闭可以降低功耗,打开有什么好处吗? 知道的大神请解答一下,谢谢 |

微信公众号

微信公众号

手机版

手机版

库函数不懂,帮顶我刚看了下,你这样置位ADC_TDRL |= 0xff,

是不是把这个寄存器的6,7位也给置位了,手册上说这两个位必须是0,ADC_TDRH也是一样必须是0

你改下试下

评分

查看全部评分

评分

查看全部评分

中文版的那个手册已经改了,而且感觉有笔误,下边是最新版的英文版本,TDRL的[7:0]都是可读写的,原因不是这个

经过大神的解答,我又在网上搜了一下,发现下边这个贴子:http://www.eepw.com.cn/article/201609/310076.htm

帖子最后边有这样一句话:“当施密特触发器被关闭后,不管外部引脚电平如何变化,它的输出恒定为0“

下图中打红叉的地方,禁止施密特触发器以后,这条路就断了

总结一下:就是作为输入时对应的施密特触发器必须使能,否则管脚的信号进不来;作为ADC时,对应的施密特触发器可以禁止,可以不禁止,禁止了可以降低一点功耗