|

以 IAR EWARM、 Keil MDK-ARM 和基于 GNU 的工具链来使用STM32F303/358xx CCM RAM 的概述与技巧 前言 本应用笔记的目的在于介绍适用于STM32F303xB/xC和STM32F358xC微控制器的内核耦合存储区(CCM)RAM,并描述利用不同的工具链从该存储区域执行部分应用程序代码所需的操作。 本应用笔记分为四个部分:第一部分是 STM32F3 CCM RAM 的概述,第二部分描述了利用以下工具链执行部分应用程序代码的步骤: • IAR EWARM • KEIL MDK-ARM™ • RIDE 和 Atollic 基于 GNU 的工具链 本文档通篇所述的步骤均适用于其它 RAM 区域,比如某些 F4 设备中的 CCM 数据 RAM 或外部 SRAM。 关于微控制器嵌入式 CCM RAM 的列表,请参考表 1。

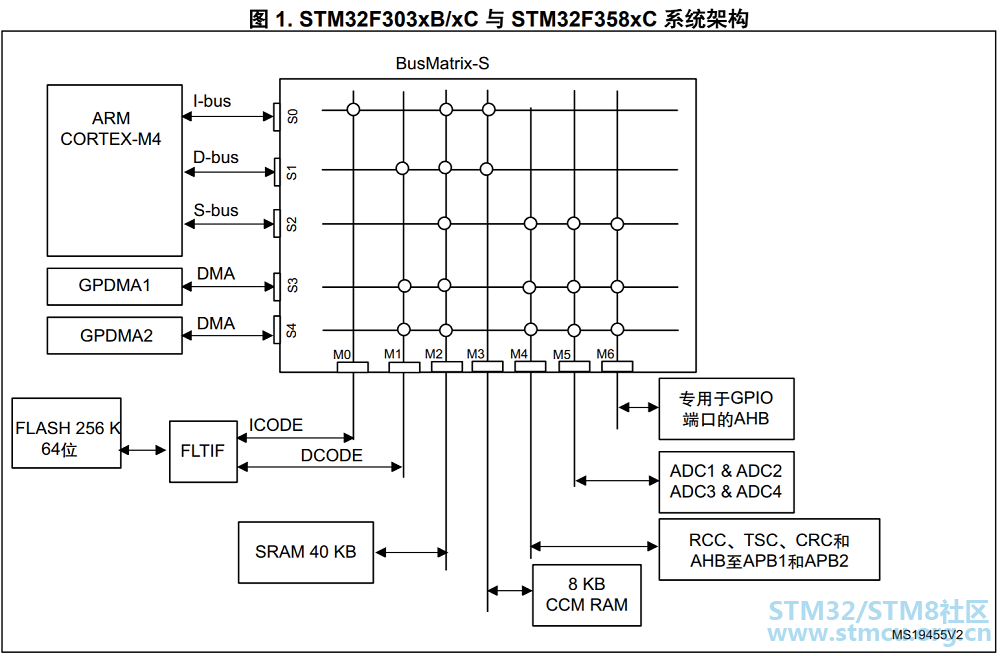

1 STM32F303xB/C 与 STM32F358xC CCM RAM 的概述 1.1 目的 STM32F303xB/C 和 STM32F358xC CCM RAM 与 Cortex™ 内核紧密结合。这主要为了以最高的系统时钟频率(72 MHz)来执行代码,同时避免出现等待状态。因此,与闪存的代码执行情况相比,该器件大大减少了关键任务的执行时间。 CCM RAM 一般用于实时的计算密集型程序,比如: • 数字电源转换的控制环 (开关电源,照明) • 矢量 3 相电机控制 • 实时 DSP 任务 当代码位于 CCM RAM 且数据保存在普通 SRAM 当中时,Cortex-M4 内核便处于最优的哈佛配置。专用的零等待状态存储器与所有 I 总线及 D 总线连接(请参考图 1: STM32F303xB/xC与 STM32F358xC系统架构),由此可实现 1.25DMIPS/MHz的执行速度,频率可达 72 MHz,最终性能可达 90 DMIPS。如果中断服务程序处于 CCM RAM 当中,这还确保了最短的延迟时间。 示例 STM32F103xx 与 STM32F303xx 微控制器之间的基准(使用意法半导体电机库 V3.4)表明,对于采用 3 电阻算法的单电机控制, STM32F303xx 的 FOC 总执行时间为 16.97 µs,而STMF103xx 的总执行时间为 21.3 µs (参考以下注释); STM32F303xx 中的 FOC 算法和无传感器算法环均从 CCM RAM 上运行。这意味着,得益于 CCM RAM, STM32F303xx 比STM32F103xx 快 20.33%。 注 : FOC 程序以结构化的 C 语言编写,因此以上数值并不代表 STM32F103xx 和 STM32F303xx的最快执行时间。此外,执行时间还受到所使用的编译器及其版本的影响。如果 CCM RAM 没有用来存储代码,可以像额外 SRAM 内存那样保存数据。然而,它无法通过 DMA 被访问。不建议将代码和数据一起放在 CCM 中,因为这样 Cortex 内核将不得不从同一个内存中获取代码和数据,有可能发生冲突。这样,内核会变为冯 · 诺依曼配置,性能从1.25DMIPS/MHz 下降至 1DMIPS/MHz 以下。

|

微信公众号

微信公众号

手机版

手机版