|

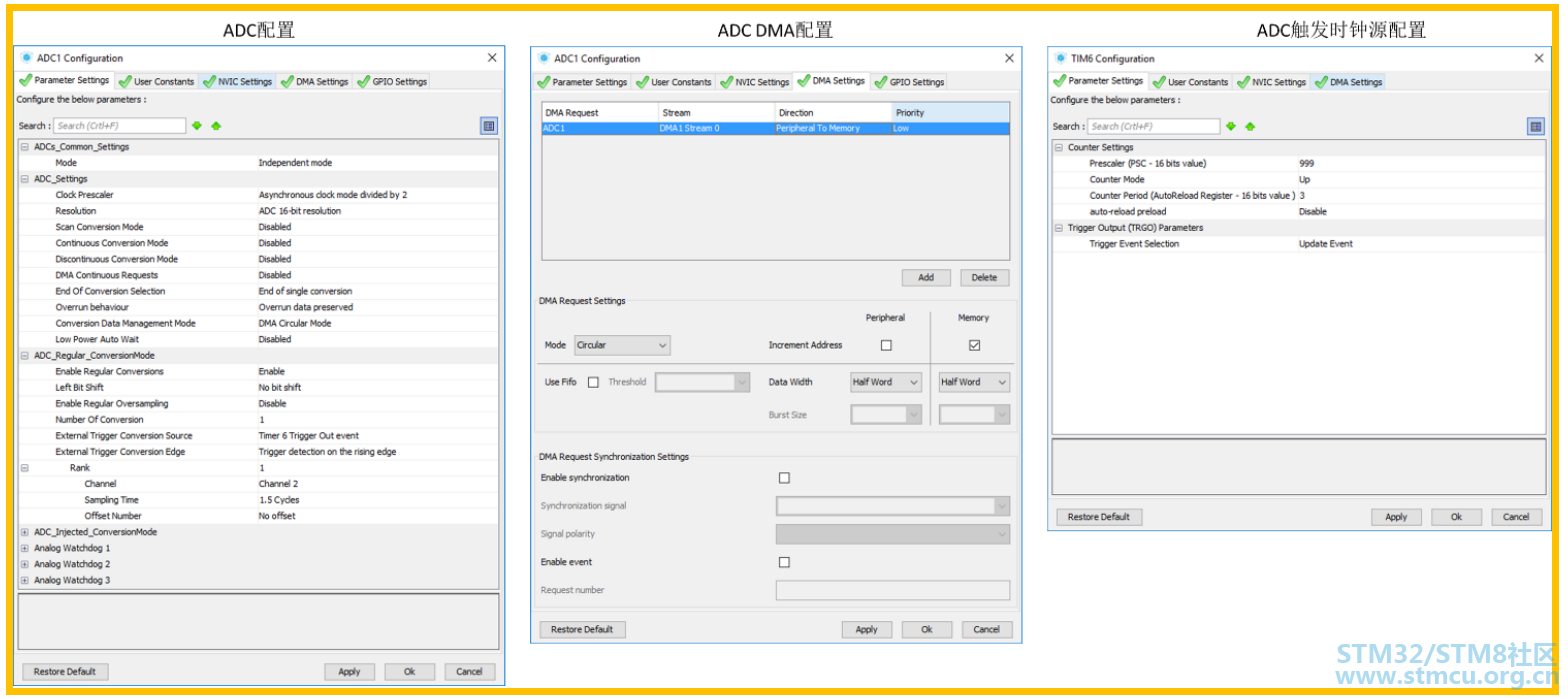

前言 利用ST提供的辅助开发工具STM32CubeMX,可以快速开发STM32应用。在本文中讨论的ADC应用,同样是建立在STM32CubeMX生成工程的基础上。具体为在STM32H743ZI上,利用DMA自动实现ADC数据周期采集和转移,在采集指定数量的采样值后产生中断,对数据进行处理。 文中仅对上述实现过程中出现的一种异常,进行介绍和分析。不涉及具体的ADC采集和处理实现的介绍。 一、实验环境 硬件平台:Nucleo-H743ZI STM32CubeMX 版本:v4.28.0 STM32CubeH7 版本:v1.2.0 IDE: MDK-ARM v5.25.2.0 (优化级别 Level3) 首先利用STM32CubeMX生成ADC应用的初始化工程,涉及的配置如下所示:

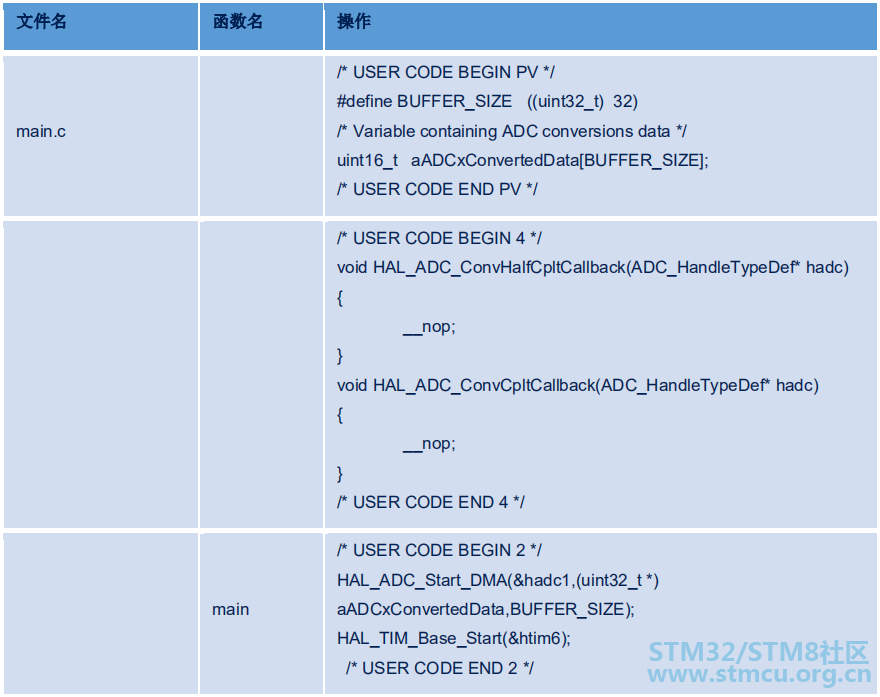

然后在工程中增加对ADC周期采集和DMA传输实现的命令,如下所示。并且增加回调函数内容,本文中实现仅添加了空指令。在调试过程中,在空指令处增加断点,判断ADC DMA传输半完成和传输完成中断是否正常进入。

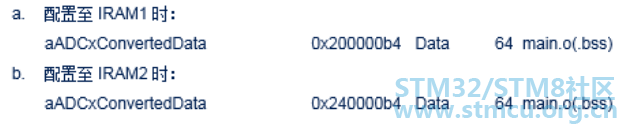

二、异常现象 在运行过程中,无法进入 HAL_ADC_ConvHalfCpltCallback 和HAL_ADC_ConvCpltCallback 回调函数(分别对应DMA传输半完成和传输完成回调函数)。 跟踪中断服务函数,发现在首次DMA1传输后,DMA_LISR寄存器值为0x8。即TEIF0置位,Stream 0 出现传输错误。 三、原因分析 根据错误信息,问题可能与DMA 1传输错误有关。重点围绕DMA1传输配置, 进行检查,并没有发现异常。 不过,同样的初始化配置和执行命令,放置在ADC例程(路径: STM32Cube_FW_H7_V1.2.0\Projects\STM32H743ZI-Nucleo\Examples\ADC\ADC_DMA_Transfer),进行编译链接后,能够正常执行。 比对两者间的工程配置,发现在RAM分配上存在差异。下图为STM32CubeMX生成工程中,对应的RAM分配情况。 与此对应,例程中RAM分配至IRAM2 (0x24000000)。

打开.map文件可以看到:

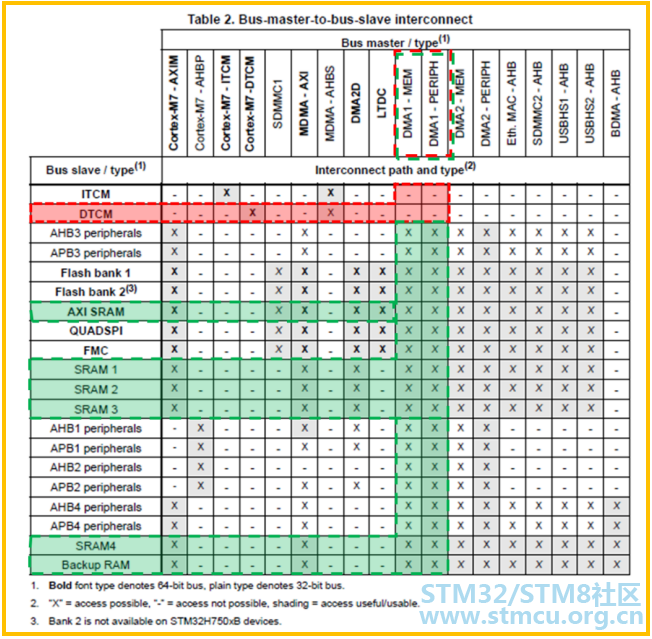

而aADCxConvertedData数组设置为DMA目标地址。问题定位为DMA目标地址引起的异常。 aADCxConvertedData数组都分配在RAM中,RAM区域情况如下表所示。

STM32H7内部包含三个域,每个区域中含有总线矩阵,具有不同的DMA主设备支持。不同区域DMA主设备能够访问的空间不同,如下表所示(下表摘自RM0433,更多详细介绍请参考RM0433)。其中,红色框中表示DMA1不支持对DTCM区域的访问。绿色框中,表示DMA1支持对SRAM1/2/3/4,后备SRAM和AXI SRAM的访问。 上述不同的工程配置,分别将aADCxConvertedData分配至DMA1不能访问的DTCM区域和DMA1能够访问的AXI SRAM区域。 从而出现描述的现象。

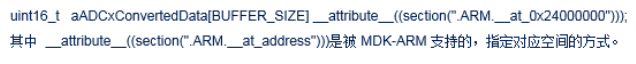

四、解决方法 通过上述分析,问题产生的原因在于DMA1 访问了无法访问到的地址。 介绍两种解决方法,方法一,通过原因分析中描述的方法,在工程中指定RAM使用空间实现目标地址(访问的数组)落在支持的RAM区域。方法二,通过在数组定义时,强制分配至支持的RAM空间区域,如下所示。

小结 STM32H7相对于之前STM32系列,具有更灵活,更多样的内存区域,以及总线矩阵。带来应用灵活性提升的同时,也一定程度上增加了使用的复杂度。用户在进行STM32H7开发时,要注意各区域和多区域之间应用实现的实际情况。在遇到问题时,可与ST提供的大量例程进行比对,并结合数据手册和参考手册,进行问题的定位和解决。 参考文档 RM0433 STM32H743/753 and STM32H750 advanced ARM®-based 32-bit MCUs DS12110 32-bit Arm® Cortex®-M7 400MHz MCUs, up to 2MB Flash,1MB RAM, 46 com. and analog interfaces |

【STM32】总线架构

没学过51单片机,能否零基础学STM32?

STM32电机控制用什么型号?高级定时器功能详解与芯片选型指南

STM32H7R/S+TouchGFX:解锁智能家电沉浸式体验新维度

什么是STM32? STM32与ARM有什么关系? STM32能做什么?

STM32 不同时钟频率有什么不同的影响

《STM32H7R/S信息安全线上课程》学习笔记+安全存储

《STM32H7R/S信息安全线上课程》学习笔记+时域隔离,片内与片外存储器保护

《STM32H7R/S信息安全线上课程》学习笔记+跟着视频学一学

《STM32H7R/S信息安全线上课程》学习笔记+2.0 生命周期管理

微信公众号

微信公众号

手机版

手机版