|

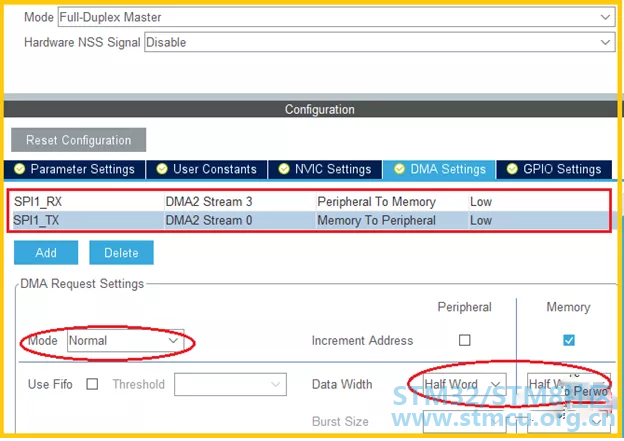

这里使用stm32h743-Nucleo板做个基于DMA传输的SPI收发应用示例。选择SPI1,MOSI与MISO短接,通过DMA自发自收,分开启Cache和不开启Cache来配置演示,以供参考。 利用STM32CubeMx进行配置,生成基于ARM MDK环境和Cube库的初始化代码。 SPI1配置在双工主角色,数据位设置为16位。开启SPI的TX/RX的DMA请求。

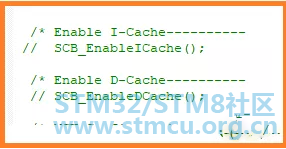

完成其它有关时钟、中断配置后,生成初始化代码并建立工程。 一、先不打开Cache。【屏蔽掉相关代码语句】

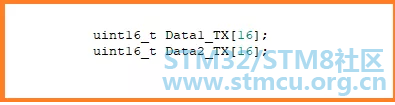

我在主程序里周期性地修改待发送的数据,并使能SPI及DMA传输进行数据收发。 这里定义了两个内存数组用于数据的收发缓冲,分别是:

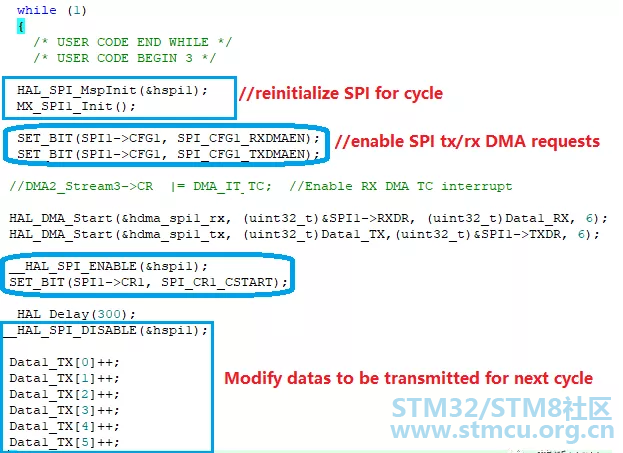

实验中我只各用到6个数据,并事先初始化。【对于验证而言,初始值是多少不重要】。 添加相关用户代码。这里我没有开启DMA传输相关中断,这点可以根据需要开启。

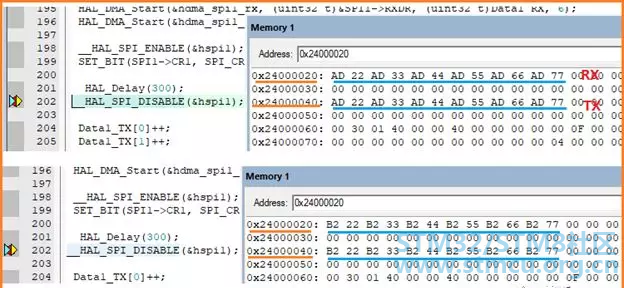

代码整理、调试完毕,看看结果。下面是通过打断点,在两个时刻的两幅截图。【注:接收缓冲区的起始地址为0x24000020,属于AXIM RAM区】。

不难看出,收发数据很一致,那我们接下来看看使用Cache的情况。 二、开启Cache时的情况。

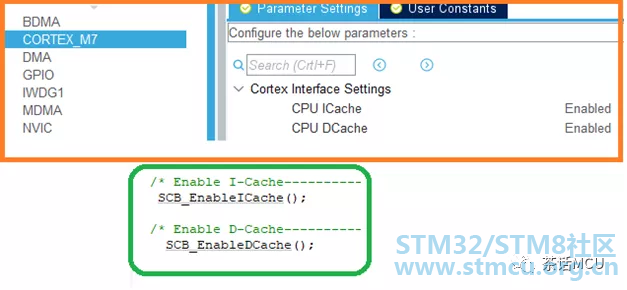

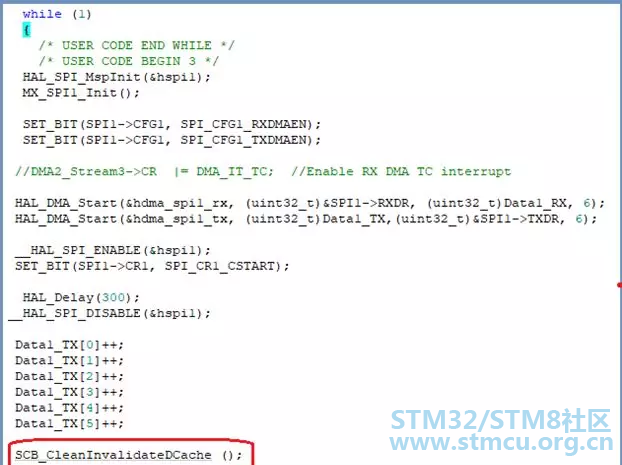

整个工作流程跟上面一样,在主程序里循环地触发SPI的DMA传输。因为开启了Cache,我们要注意数据一致性问题的处理。在主循环的修改发送收据操作后做了Dcache的清除和失效操作。当然,我们也可以开启DMA传输中断,比方在传输完成中断里做Cache相关的数据更新与维护操作。整个用户代码跟上面不开启Cache时几乎一样,就最后多了一句跟Cache相关的代码。

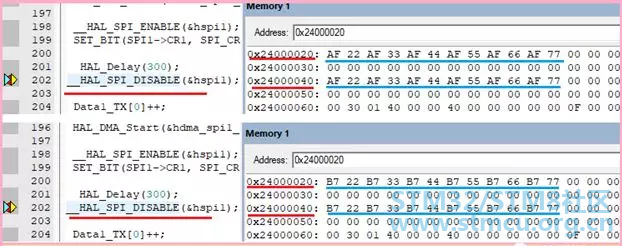

稍作整理、编译运行,看看结果。同样,下面是通过打断点,在两个时刻的两幅截图。【注:接收缓冲区起始地址是0x24000020,属于AXIM RAM区】。

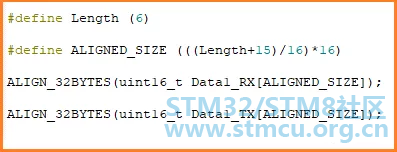

从验证结果可以看出,发送、接收的数据非常地一致。 这里提醒下,如果开启DCache,对于会被Cache的数据缓冲区,其地址以及缓冲区大小须遵循32字节对齐的原则。所以,关于收发缓冲区的定义及初始化,开启Cache时跟不开启Cache稍有点差异。【下面的6代表代码中用到的六个16位半字数据】

|

【STM32】总线架构

没学过51单片机,能否零基础学STM32?

STM32电机控制用什么型号?高级定时器功能详解与芯片选型指南

STM32H7R/S+TouchGFX:解锁智能家电沉浸式体验新维度

什么是STM32? STM32与ARM有什么关系? STM32能做什么?

STM32 不同时钟频率有什么不同的影响

《STM32H7R/S信息安全线上课程》学习笔记+安全存储

《STM32H7R/S信息安全线上课程》学习笔记+时域隔离,片内与片外存储器保护

《STM32H7R/S信息安全线上课程》学习笔记+跟着视频学一学

《STM32H7R/S信息安全线上课程》学习笔记+2.0 生命周期管理

微信公众号

微信公众号

手机版

手机版