|

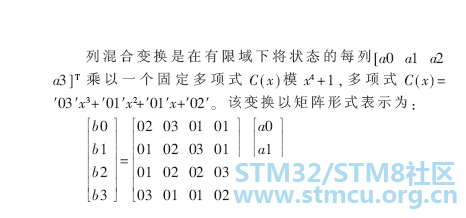

1 AES算法 1.1 AES算法描述 AES加密算法是密码学中的高级加密标准,该加密算法采用对称分组密码体制,密钥长度的最少支持为128、192、256,分组长度128位,算法应易于各种硬件和软件实现。这种加密算法是美国联邦政府采用的区块加密标准,这个标准用来替代原先的DES,已经被多方分析且广为全世界所使用。 密钥密码体制分为流密码和分组密码两种。分组密码是信息与网络安全中实现数据加密、数字签名、认证及密钥管理的核心体制,具有速度快、易于标准化和便于软硬件实现等特点。 AES加密算法被设计为支持128/192/256位(/32=nb)数据块大小(即分组长度);支持128/192/256位(/32=nk)密码长度,,在10进制里,对应34&TImes;1038、62&TImes;1057、1.1&TImes;1077个密钥。 另外,AES密码在相同的轮函数作用下,迭代运算次数的不同可达到不同级别的安全强度。128 bit分组长度的情况下,循环轮数指定为11次,目前还没有可行的算法可以对该模型进行有效攻击。每一轮处理均为作用在中间结果上的一批运算,该中间结果称为状态,用4&TImes;4字节矩阵表示,其中,数据矩阵称为State、密钥矩阵称为Key。AES加密涉及5种运算,分别是字节代换 (SubBytes)、行移变换(ShiftRows)、列混合变换(MixColumns)、密钥加法(AddRoundKey)和密钥扩展 (ExpandedKey)。 字节代换是对State每个字节进行独立非线性变换,由字节在GF(28)域中求其乘法逆并外加一个仿射变换完成。具体实现中广泛使用查表方式完成该步变换(实现该功能单元被称为Sbox),以避免复杂的乘法运算。 行移变换是对State进行按行移位操作,第0行不移位,第1行循环左移一位,第2行循环左移两位,第3行循环左移三位。

密钥加法是将轮密钥Key和状态State中对应字节按位“异或”。 密钥扩展提供轮变换对应密钥加法用到的各轮密钥。各轮运算中使用到的轮密钥都不相同,密钥扩展运算通过控制迭代运算次数计算出对应轮所需轮密钥。 加密过程由11轮运算组成,其中首轮只进行密钥加法,接着进行9次轮变换,轮变换由字节代换、行移变换、列混合变换及密钥加法4个步骤构成,再进行末轮变换,在末轮中跳过列混合变换。末轮完成后输出密文数据。AES加密过程如图1所示。 1.2 常用AES优化实现 AES算法的轮操作特点看似更适合于在通用CPU平台下编程实现,而实际上,此种实现方式在性能方面存在加密速度慢等先天局限性。AES加密处理单元一般处于数据主干道上,其处理数据能力直接影响整个应用系统的外在性能表现,因此,研究数据处理能力强的硬件加密实现方式具有重要的意义。如何实现高性价比的硬件AES加密一直是加密算法应用领域研究的热点问题。 常见的硬件优化实现有如下几种方式:(1)串行方式。将轮函数展平,每轮对应一级组合逻辑,11轮迭代过程直接相连,前一级输出作为次一级的输入,每一个时钟周期均可完成一个分组处理;(2)迭代方式。各轮迭代只用一个对应轮函数功能的组合逻辑实体实现,每11个时钟周期完成一个分组处理;(3)流水线方式。用于提高系统工作时钟周期的流水线技术,一般仅在局部使用,或是与串行方式并用,可提高工作时钟频率,使其满足极大带宽的应用要求;(4)轮内实现流水线。在轮函数对应实体中插入寄存器,将一轮运算分至多个逻辑段完成,每个时钟周期仍能完成一个数据分组处理。 以上AES算法实现方式各有优缺点,但总体来说缺乏灵活性。当前应用于嵌入式系统的AES加密模块在灵活性、资源占用上还不是很理想。在对常用优化方法进行研究后,本文针对嵌入式系统设计一种AES加密IP核、实现低资源占用、高性能要求、32位数据位宽、且能方便进行并行连接,实现数据位宽扩展。 2 IP核设计 2.1 系统架构设计 IP系统分为时序控制、密钥处理、数据处理三个主要单元,系统的工作模式分为闲置模式、密钥输入模式、单轮加密模式及连续加密模式。复位后系统处于闲置模式,单轮加密模式可以直接切换为连续加密模式,而连续加密模式需进入到闲置模式至少一个时钟周期后才可切换到单轮加密工作模式。 密钥处理单元在系统进入密钥输入模式后的连续4个时钟周期从数据输入端口读入总共128位密钥数据,在第5个时钟周期到来时完成第一轮密钥的计算,然后系统返回闲置模式。在加密模式中密钥处理单元按算法需求实时计算各轮密钥,并按32位为一组输出,与数据通道中32位数据进行“异或”运算。在系统模式由加密模式转为闲置模式时,完成密钥处理单元的归位动作,使得单元状态与密钥输入后的状态相同,为下一次加密做准备。 数据处理单元在加密模式下对明文数据进行迭代运算。该单元检测到当前是最末轮数据处理时自动跳过列混合运算。在系统进入加密模式后,数据处理单元从输入端口分4次读入128位明文数据,经过接下来的40个时钟周期数据运算过程后,得到密文中的第一个32位数据段。 时序控制单元负责整个系统关键控制信号的生成,控制信号集中由一个单元负责产生,不仅利于软件综合出较高的时钟频率,而且输出的时钟相位也有较优的一致性。 系统正常工作状态为先进行一次密钥载入操作,然后触发进入加密模式进行多次的数据加密。在需要时可以在闲置状态下再次进行密钥模式对密钥进行更新。 在系统闲置状态下,密钥加载信号被检测为有效时,系统进入密钥输入模式,对密钥数据进行读入、保存及生成第一轮密钥待用,而忽略密钥处理单元中是否先前已存在密钥数据。数据加载引脚指示系统由闲置模式输入单轮加密模式,因为128位数据要在4个时钟周期完成读入,加密后数据也需要4个时钟周期时间才能完成输出。因此,从明文数据输入到密文数据输出共需要等待40个时钟周期。如果此时检测到数据加载引脚信号有效则在输出密文的同时进行下一轮明文的读入,系统进入到连续加密模式,否则在接下来的4个时钟周期将密文输出后系统由单轮加密模式切换到闲置模式。连续加密模式适合用于进行批量数据加密处理,系统每40 个时钟周期会从输入端口读入128位明文数据,同时在这40个时钟周期中将提供密文数据。在进行大量数据处理时,载入密钥及载入第一组加密数据的几个时钟周期均可忽略,系统性能为每40个时钟周期处理128位数据。在读入明文时,若检测到载入数据信号无效,则退出连续加密模式,系统回复到闲置状态。 |

微信公众号

微信公众号

手机版

手机版