|

本文以STM32F103为例,将本人所知的关于STM32的时钟系统的知识点展示出来。

先贴上STM32F1系列的时钟树

1、时钟源 由时钟树可以,对于STM32来说,时钟源一共有四个,分别为 LSI 、LSE 、HSE 、HSI。另外一种说法为五个,加上PLL。个人认为,根据上面这个时钟树也可以看出,PLLCLK是HSE或者HSI经过锁相环倍频后的输出时钟信号,并不能说是STM32的时钟源之一,不过可以认为是STM32系统时钟SYSCLK的时钟源之一。 STM32的时钟可分为高速时钟(HSE、HSI、PLL)和低速时钟(LSI、LSE),也可以分为内部时钟(HSI、LSI、PLL)和外部时钟(HSE、LSE)。 根据上图标号顺序来解释各自功能

除了上述的时钟源以外,还涉及一个以太网的时钟信号,如标号12、13。以太网MAC的时钟(TX、RX和RMII)是由外部PHY提供。 2、高速外部时钟信号(HSE) 高速外部时钟信号(HSE)由以下两种时钟源产生:

外部时钟源(External clock) 这个模式下需要外部来提供时钟信号,最大为50MHz。如下图的上半部分所示,外部时钟信号(50%占空比的方波、正弦波或 外部晶体 外部晶体/ 陶瓷谐振器(External crystal/ceramic resonator) 这个模式需要外接晶体来为整个系统提供时钟信号,频率范围为 4MHz~16MHz。需要注意的是:为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚。负载电容值必须根据所选择的振荡器来调整。一般在购买晶振的时候会标注需要多大的起振电容。

3、低速外部时钟信号(LSE) LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器。它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源。 通HSE一样,具备两种时钟输入模式,具体请参考HSE。

系统时钟(SYSCLK)的时钟源有三个

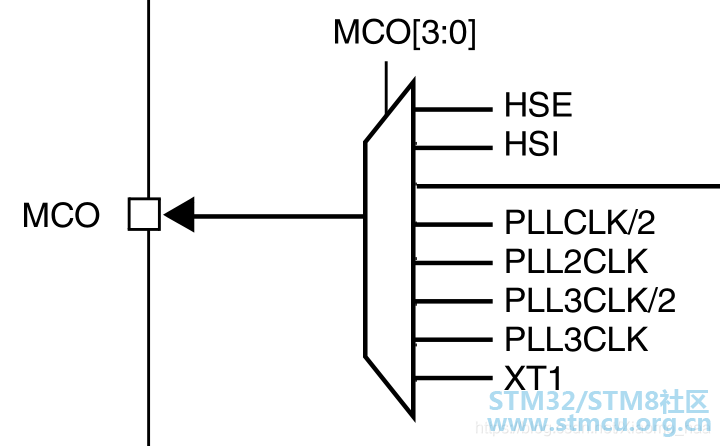

系统时钟(SYSCLK)是供 STM32 中绝大部分部件工作的时钟源。通过多个预分频器配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。AHB和APB2域的最大频率是72MHz。APB1域的最大允许频率是36MHz。 也可以将SYSCLK作为MCO(时钟输出)的时钟源。 注:以下部件的时钟源不来自系统时钟 5、时钟输出(MCO) MCO 是 STM32 的一个时钟输出 IO,它可以选择一个时钟信号输出,如下图所示,可以选择为 HSI、HSE、PLL 输出或者系统时钟。这个时钟可以用来给外部其他系统提供时钟源。

除了上述的几个部件之外,其余所有的外设时钟源均为AHB时钟提供。

RCC通过AHB时钟(HCLK)8分频后作为Cortex系统定时器(SysTick)的外部时钟。通过对SysTick控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick时钟。ADC时钟由高速APB2时钟经2、4、6或8分频后获得等等。 具体各路时钟信号输出为

以上便是STM32F1的时钟树,不同的器件的时钟系统基本上大差不差,可能别的器件功能更加强大,会有更多的外设,其时钟源具体请参阅相关的参考文档。 |

微信公众号

微信公众号

手机版

手机版