|

PCB层叠结构设计对产品成本、产品EMC的好坏都有直接的影响。板层的增加,方便了布线,但也增加了成本。设计的时候需要考虑各方面的需求,以达到最佳的平衡。 在完成元器件的预布局后,一般需要对PCB的布线瓶颈处进行重点分析。结合其他EDA工具分析电路板的布线密度;再综合有特殊布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后根据电源的种类、隔离和抗干扰的要求来确定内电层的数目。 01 层叠选择因素考虑 电路板的层数越多,特殊信号层、地层和电源层的排列组合的种类也就越多。 (1)信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。 (2)内部电源层和地层之间应该紧密耦合,也就是说,内部电源层和地层之间的介质厚度应该取较小的值。 (3)电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间。这样两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。 (4)避免两个信号层直接相邻。相邻的信号层之间容易引入串扰,从而导致电路功能失效。在两信号层之间加入地平面可以有效地避免串扰。 (5)多个接地的内电层可以有效地降低接地阻抗。例如,A信号层和B信号层采用各自单独的地平面,可以有效地降低共模干扰。 (6)兼顾层结构的对称性。

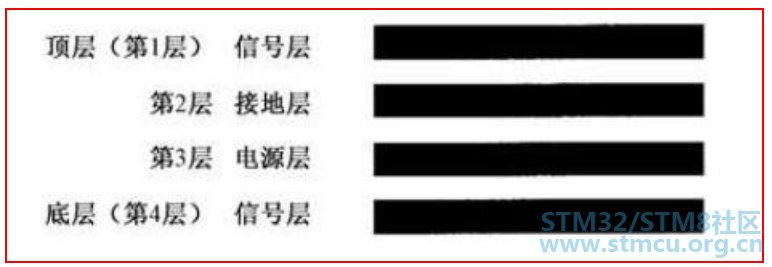

常见的叠层设计: 2.1 四层板叠层结构

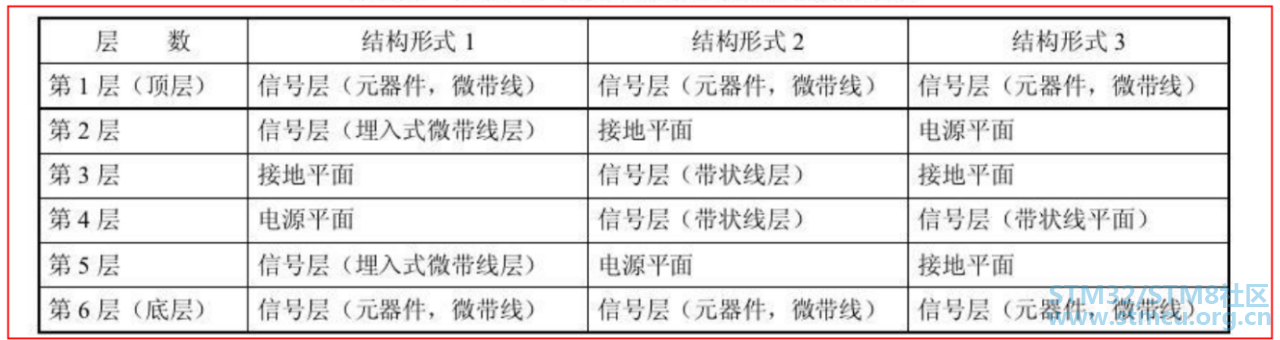

2.2 六层板叠层结构

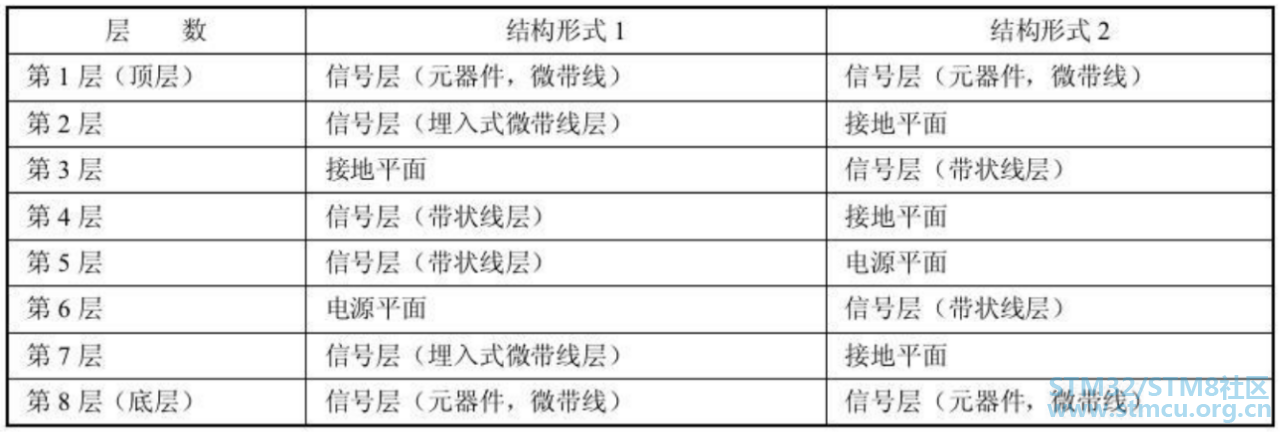

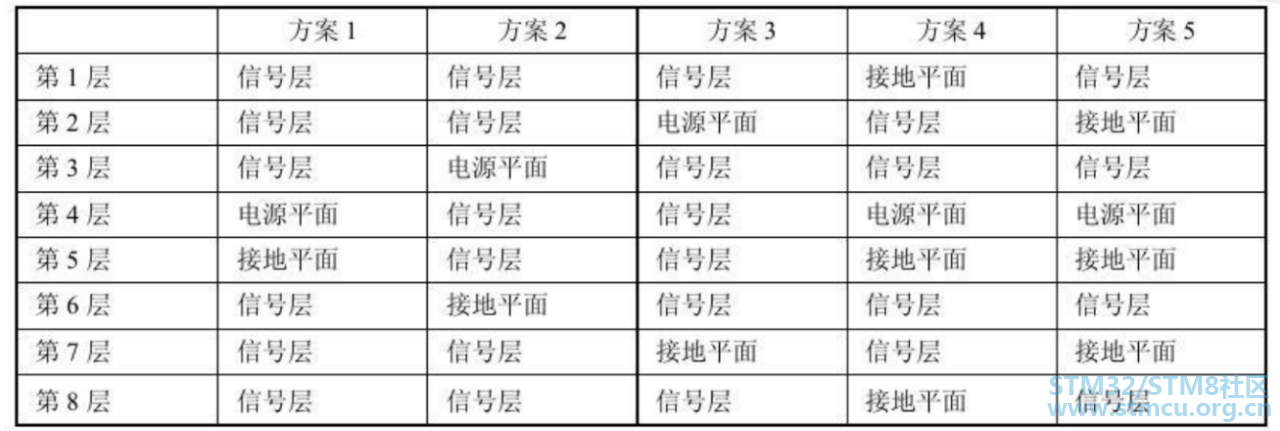

2.3 八层板叠层结构

02 一到八层电路板的叠层设计方式 1)单面板和双面板的叠层 对于两层板来说,由于板层数量少,已经不存在叠层的问题。控制EMI辐射主要从布线和布局来考虑; 单层板和双层板的电磁兼容问题越来越突出。造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。 关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。对干扰敏感的信号是指那些电平较低的模拟信号。 单、双层板通常使用在低于10KHz的低频模拟设计中: 1. 在同一层的电源走线以辐射状走线,并最小化线的长度总和; 2. 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。 3. 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。这样形成的回路面积等于pcb线路板的厚度乘以信号线的长度。 2)四层板的叠层 推荐叠层方式: 2.1 SIG-GND(PWR)-PWR (GND)-SIG; 2.2 GND-SIG(PWR)-SIG(PWR)-GND; 对于以上两种叠层设计,潜在的问题是对于传统的**1.6mm(62mil)**板厚。层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。 对于第一种方案,通常应用于板上芯片较多的情况。这种方案可得到较好的SI性能,对于EMI性能来说并不是很好,主要要通过走线及其他细节来控制。主要注意:地层放在信号最密集的信号层的相连层,有利于吸收和抑制辐射;增大板面积,体现20H规则。 3)六层板的叠层 对于芯片密度较大、时钟频率较高的设计应考虑6层板的设计。 推荐叠层方式: 3.1 SIG-GND-SIG-PWR-GND-SIG; 对于这种方案,这种叠层方案可得到较好的信号完整性,信号层与接地层相邻,电源层和接地层配对,每个走线层的阻抗都可较好控制,且两个地层都是能良好的吸收磁力线。并且在电源、地层完整的情况下能为每个信号层都提供较好的回流路径。 3.2 GND-SIG-GND-PWR-SIG -GND; 对于这种方案,该种方案只适用于器件密度不是很高的情况,这种叠层具有上面叠层的所有优点,并且这样顶层和底层的地平面比较完整,能作为一个较好的屏蔽层来使用。需要注意的是电源层要靠近非主元件面的那一层,因为底层的平面会更完整。因此,EMI性能要比第一种方案好。 小结:对于六层板的方案,**电源层与地层之间的间距应尽量减小,以获得好的电源、地耦合。**但62mil的板厚,层间距虽然得到减小,还是不容易把主电源与地层之间的间距控制得很小。对比第一种方案与第二种方案,第二种方案成本要大大增加。因此,我们叠层时通常选择第一种方案。设计时,遵循20H规则和镜像层规则设计。 4)八层板的叠层 八层板通常使用下面三种叠层方式 4.1 由于差的电磁吸收能力和大的电源阻抗,导致这种不是一种好的叠层方式。它的结构如下: 1 Signal 1 元件面、微带走线层 2 Signal 2 内部微带走线层,较好的走线层(X方向) 3 Ground 4 Signal 3 带状线走线层,较好的走线层(Y方向) 5 Signal 4 带状线走线层 6 Power 7 Signal 5 内部微带走线层 8 Signal 6 微带走线层 4.2 是第三种叠层方式的变种,由于增加了参考层,具有较好的EMI性能,各信号层的特性阻抗可以很好的控制。 1 Signal 1 元件面、微带走线层,好的走线层 2 Ground 地层,较好的电磁波吸收能力 3 Signal 2 带状线走线层,好的走线层 4 Power 电源层,与下面的地层构成优秀的电磁吸收 5 Ground 地层 6 Signal 3 带状线走线层,好的走线层 7 Power 地层,具有较大的电源阻抗 8 Signal 4 微带走线层,好的走线层 4.3 最佳叠层方式,由于多层地参考平面的使用具有非常好的地磁吸收能力。 1 Signal 1 元件面、微带走线层,好的走线层 2 Ground 地层,较好的电磁波吸收能力 3 Signal 2 带状线走线层,好的走线层 4 Power 电源层,与下面的地层构成优秀的电磁吸收 5 Ground 地层 6 Signal 3 带状线走线层,好的走线层 7 Ground 地层,较好的电磁波吸收能力 8 Signal 4 微带走线层,好的走线层 |

微信公众号

微信公众号

手机版

手机版