.png) STMCU小助手

发布时间:2021-7-19 14:55

STMCU小助手

发布时间:2021-7-19 14:55

|

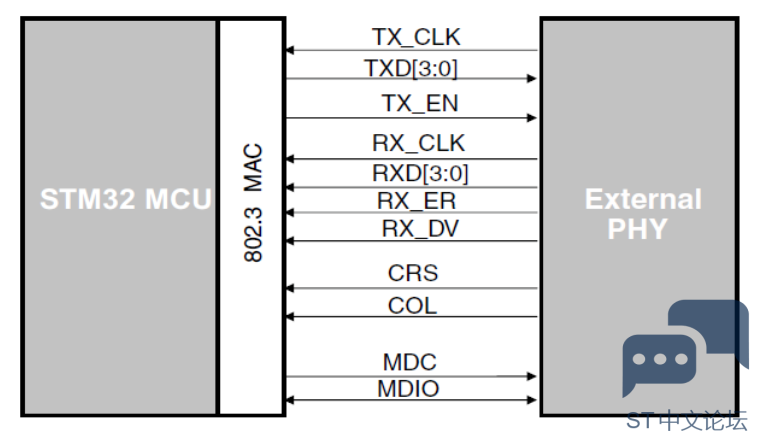

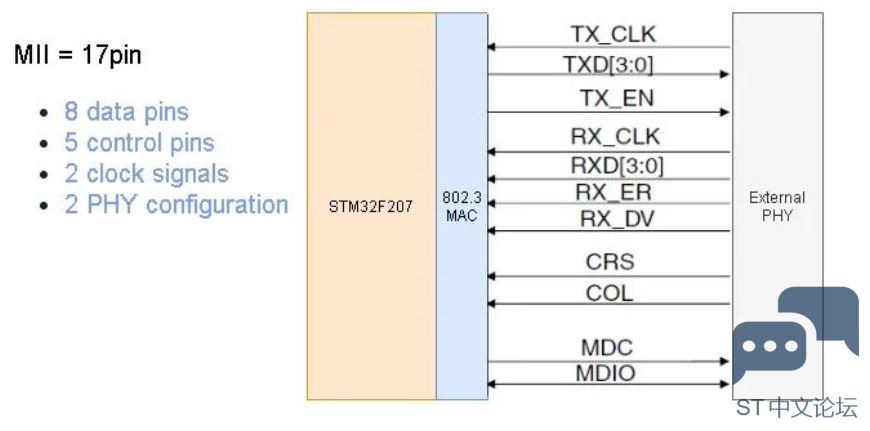

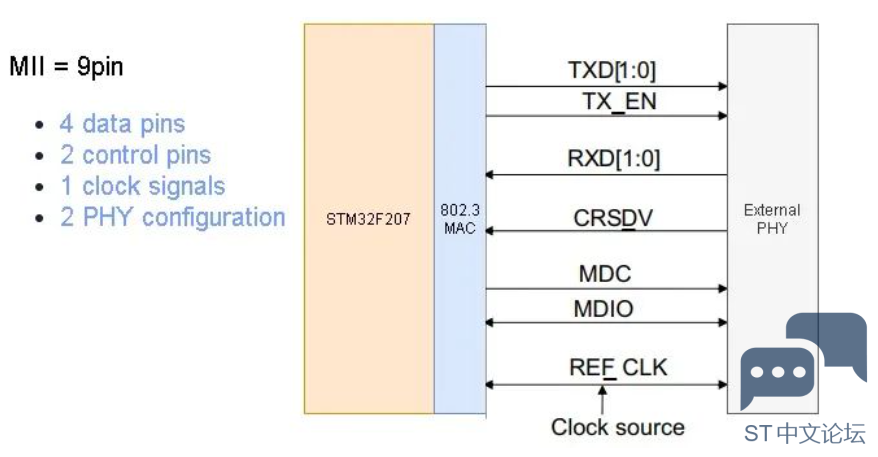

1、MII接口 介质独立接口(MII) 定义了10 Mbit/s 和100 Mbit/s 的数据传输速率下MAC 子层与PHY 之间的互连。

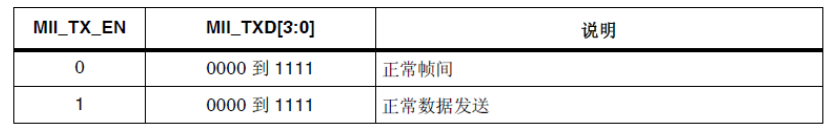

管脚定义介绍: MII_TX_CLK:连续时钟信号。该信号提供进行 TX 数据传输时的参考时序。标称频率为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。 MII_TXD[3:0]:数据发送信号。该信号是 4 个一组的数据信号,由 MAC 子层同步驱动,在MII_TX_EN 信号有效时才为有效信号(有效数据)。MII_TXD[0] 为最低有效位,MII_TXD[3] 为最高有效位。禁止MII_TX_EN 时,发送数据不会对 PHY 产生任何影响。 MII_TX_EN:发送使能信号。该信号表示 MAC 当前正针对 MII 发送半字节。该信号必须与报头的前半字节进行同步 (MII_TX_CLK),并在所有待发送的半字节均发送到 MII时必须保持同步。 MII_RX_CLK:连续时钟信号。该信号提供进行 RX 数据传输时的参考时序。标称频率为:速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。 MII_RXD[3:0]:数据接收信号。该信号是 4 个一组的数据信号,由 PHY 同步驱动,在MII_RX_DV 信号有效时才为有效信号(有效数据)。MII_RXD[0] 为最低有效位,MII_RXD[3] 为最高有效位。当 MII_RX_DV 禁止、MII_RX_ER 使能时,特定的MII_RXD[3:0] 值用于传输来自 PHY 的特定信息。 MII_RX_ER:接收错误信号。该信号必须保持一个或多个周期 (MII_RX_CLK),从而向MAC 子层指示在帧的某处检测到错误。该错误条件必须通过 MII_RX_DV验证。 MII_RX_DV:接收数据有效信号。该信号表示 PHY 当前正针对 MII 接收已恢复并解码的半字节。该信号必须与恢复帧的头半字节进行同步 (MII_RX_CLK),并且一直保持同步到恢复帧的最后半字节。该信号必须在最后半字节随后的第一个时钟周期之前禁止。为了正确地接收帧,MII_RX_DV 信号必须在时间范围上涵盖要接收的帧,其开始时间不得迟于 SFD 字段出现的时间。 MII_CRS:载波侦听信号。当发送或接收介质处于非空闲状态时,由 PHY 使能该信号。发送和接收介质均处于空闲状态时,由 PHY 禁止该信号。PHY 必须确保 MII_CS 信号在冲突条件下保持有效状态。该信号无需与 TX 和 RX 时钟保持同步。在全双工模式下,该信号没意义。 MII_COL:冲突检测信号。检测到介质上存在冲突后,PHY 必须立即使能冲突检测信号,并且只要存在冲突条件,冲突检测信号必须保持有效状态。该信号无需与 TX 和 RX 时钟保持同步。在全双工模式下,该信号没意义。 MDC:MDC信号属于SMI接口,具体请看《STM32网络之SMI接口》。 MDIO:MDIO信号属于SMI接口,具体请看《STM32网络之SMI接口》。 下图TX接口信号编码

下图RX 接口信号编码

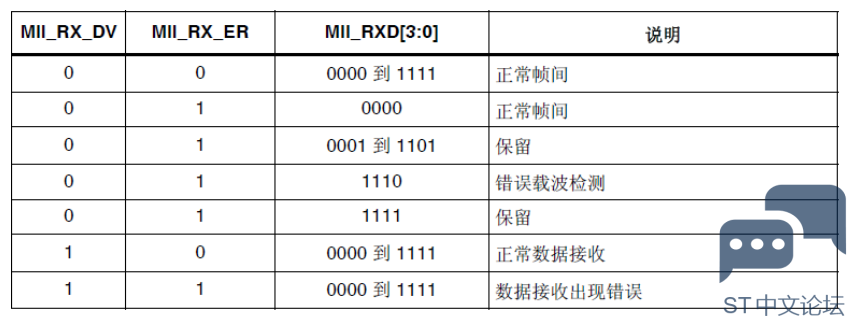

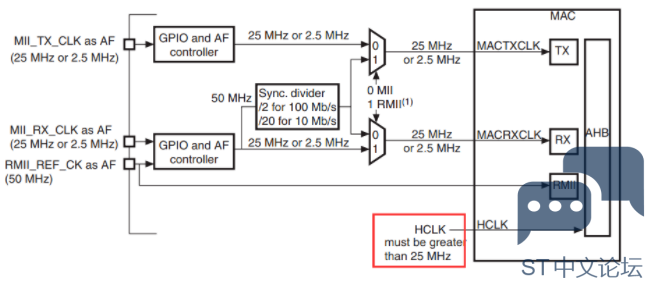

MII接口的时钟源 要生成TX_CLK 和RX_CLK 时钟信号,必须向外部PHY 提供25MHz 时钟,如图所 示。除了使用外部 25 MHz石英晶体提供该时钟,还可以通过STM32F20xx 微控制器的MCO引脚输出该信号。这种情况下,必须对PLL 倍频进行配置,以通过25 MHz 外部石英晶体在MCO 引脚上获得所需频率。

对应的代码

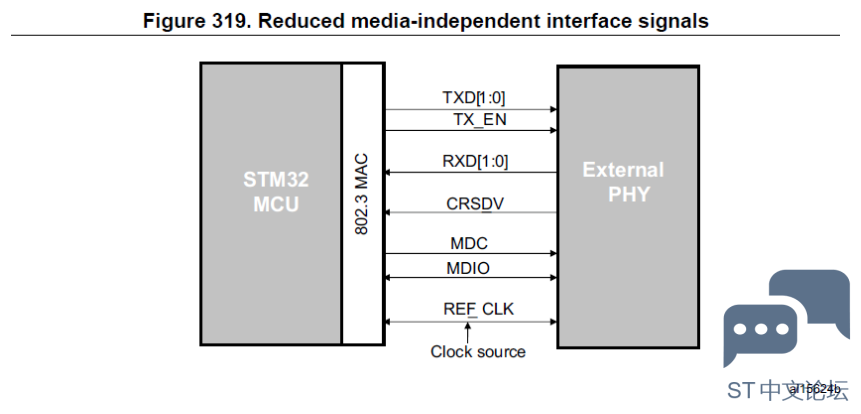

Reduced media-independent interface: RMII(精简介质独立接口)。精简介质独立接口(RMII) 规范降低了10/100 Mbit/s 下微控制器以太网外设与外部PHY 间的引脚数。 根据IEEE 802.3u 标准,MII包括16 个数据和控制信号的引脚。RMII规范将引脚数减少为 7 个(引脚数减少62.5%)。引脚的含义参考MII接口即可。

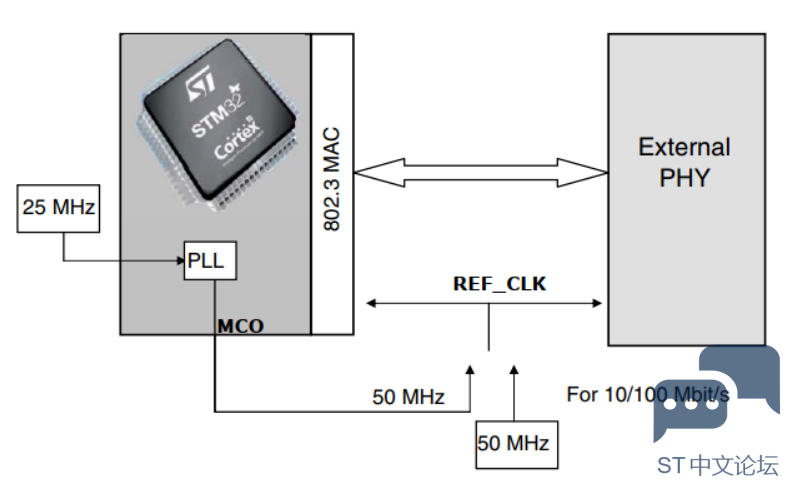

RMII接口是MAC和PHY之间的实例化对象。这些有助于MAC的MII接口转化为RMII接口。RMII接口具有以下特点 10-Mbit/s 和 100-Mbit/s 的运行速率 参考时钟必须是 50 MHz 相同的参考时钟必须从外部提供给 MAC 和外部以太网 PHY 它提供了独立的 2 位宽(双位)的发送和接收数据路径 这里时钟管脚比MII接口少,有一个非常重要的点,那就是RMII接口时钟源必须是50MHZ RMII接口时钟源 STM32F207xx控制器可以从MCO引脚提供50MHz时钟信号,当然用户需要配置PLL来产生这一时钟。

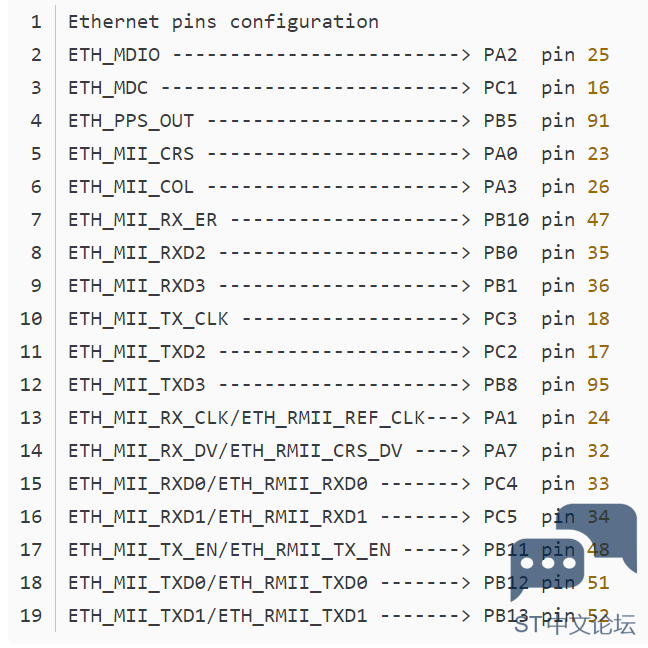

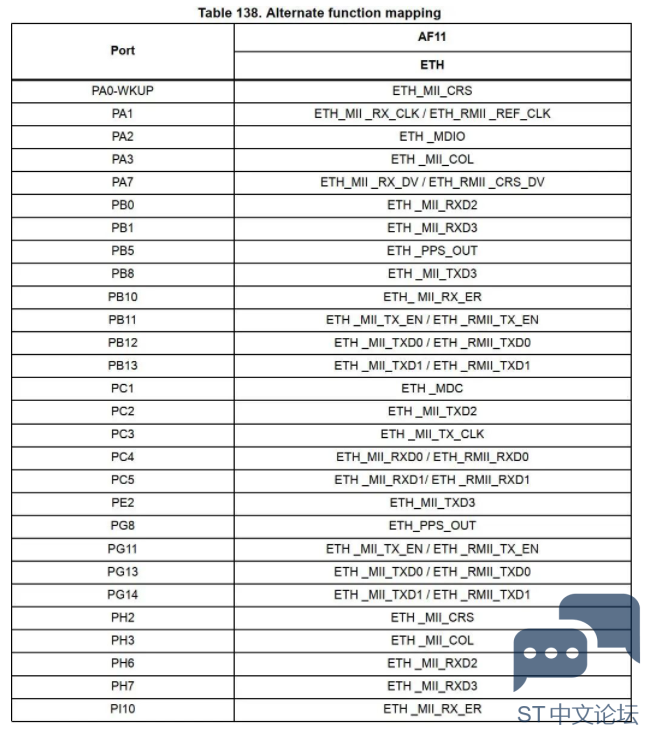

使用外部50 MHz 时钟驱动PHY 或使用嵌入式PLL 生成50 MHz 频率信号来驱动PHY。 3、两种接口对应的引脚 STM32F207VCT6(100pin)的芯片

其中ETH_PPS_OUT这个管脚ST官方demo屏蔽,不属于MII接口也不属于RMII接口。下面不将其统计进入。 MII 共15个接口加上SMI接口,共17个引脚。(没有包含25MHz时钟的引脚)

RMII共7个接口加上SMI接口,共9个引脚。

除了上述我自行统计的MII接口和RMII接口对应的pin之外,ST官方在参考手册也给出了对应图,如下:

4、MII和RMII的选择 使用SYSCFG_PMC 寄存器(注意:这里和F107不同,F107是AFIO_MAPR寄存器)中的23配置位MII_RMII_SEL选择MII 或RMII 模式。以太网控制器处于复位模式或使能时钟前,应用程序必须设置MII/RMII 模式。 对应的ST库函数为

支持MII 和RMII 以及10 和100 Mbit/s 运行所需的时钟方案,如下图所示。

注意上图红框中:HCLK必须大于25MHz,这个问题点,在上一篇文章《STM32网络之SMI接口》中已经提到了,这里再次提到,如果不满足这个条件,可能会出现奇奇怪怪的问题,不好查找。 在官方手册中,还有一句

要节省引脚,需在同一个GPIO 引脚上复用RMII_REF_CK 和MII_RX_CLK 这两个输入时钟信号。 |

微信公众号

微信公众号

手机版

手机版