.png) STMCU小助手

发布时间:2021-7-30 11:17

STMCU小助手

发布时间:2021-7-30 11:17

|

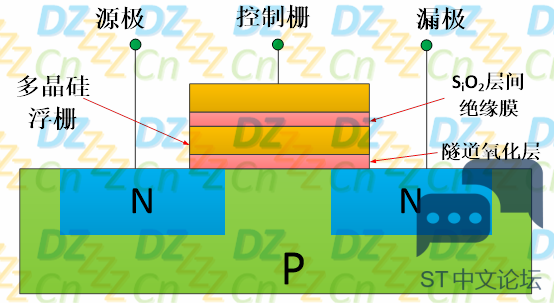

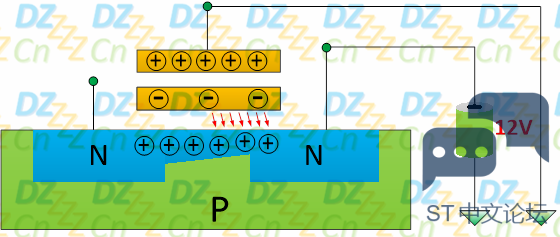

EEPROM(Electrically Erasable Programmable read only memory)即电可擦可编程只读存储器,是一种掉电后数据不丢失(不挥发)存储芯片。 EERPOM的基本结构有几种,这里讲解比较常用的FLOTOX管结构,如下图所示:

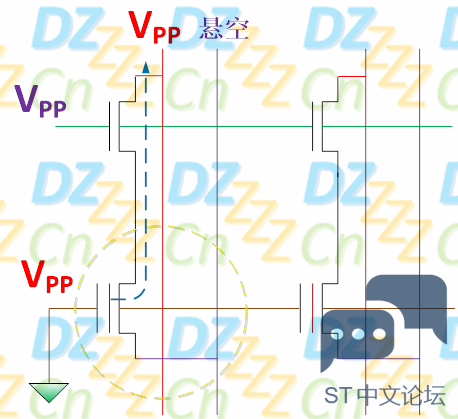

FLOTOX(Floating Gate Tunneling Oxide)MOS管即浮栅隧道氧化层晶体管,它是在标准CMOS工艺的基础上衍生的技术。 如上图所示,在传统的MOS管控制栅下插入一层多晶硅浮栅,浮栅周围的氧化层与绝缘层将其与各电极相互隔离,这些氧化物的电阻非常高,而且电子从浮栅的导带向周围氧化物导带的移动需要克服较高的势叠,因此,浮栅中的电子泄漏速度很慢,在非热平衡的亚稳态下可保持数十年。 浮栅延长区的下方有个薄氧区小窗口,在外加强电场的作用下漏极与浮栅之间可以进行双向电子流动,继而达到对存储单元的“擦除”与“写入”操作。 为强调浮栅周围氧化物的绝缘效果,我们把绝缘层去掉,如下图所示,其中的“电子”就是我们需要存储的数据:

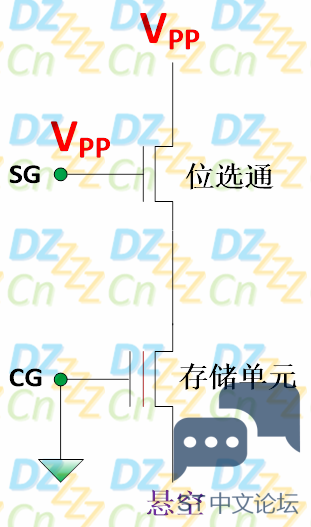

其原理图符号如下所示:

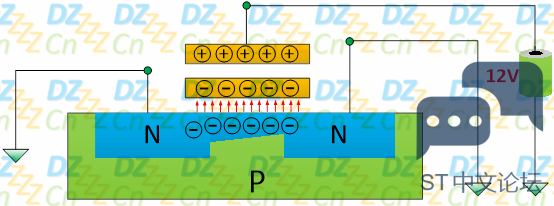

我们通常利用F-N隧道效应(Fowler-Nordheim tunneling)对EEPROM存储单元进行“擦除”或“写入”操作,简单地说,即FLOTOX管的控制栅极与漏极在强电场的作用下(正向或负向),浮栅中的电子获得足够的能量后,穿过二氧化硅层的禁带到达导带,这样电子可自由向衬底移动(具体细节可自行参考相关资料,此处不赘述)。 对EEPROM存储单元进行“擦除”操作,就是将电子注入到浮栅中的过程(不要将此处的“擦除”操作与FLASH存储单元中的“擦除”操作弄反了,具体参考FLASH对应文章),如下图所示:

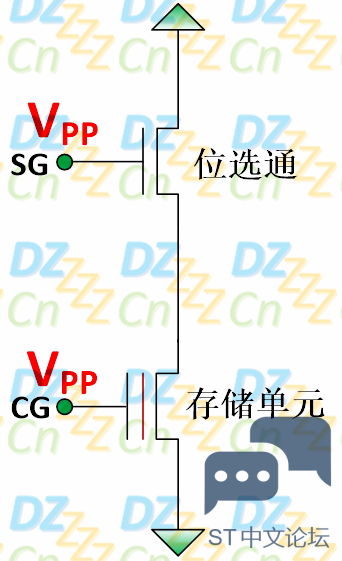

如上图所示,将FLOTOX管的源极与漏极接地,而控制栅极接高压(不小于12V),浮栅与漏极之间形成正向强电场,电子从漏极通过隧道氧化层进入浮栅。 为防止存储单元“擦除”(或“写入”操作)对其它单元产生影响,每个FLOTOX管均与一个选通管配对(按照制造工艺可分为N管与P管,这里我们以N管为例进行讲解,P管是类似的),前者就是存储电子的单元,而后者用来选择相应的存储单元的控制位,这种结构导致单位存储面积比较大,因此,EEPROM存储芯片的容量通常都不会很大。 一个bit位的存储单元电路状态如下图所示:

其中,SG表示选通管的选通栅(Select Gate),CG表示FLOTOX管的控制栅(Control Gate),VPP表示外接高压,此处以12V为例 对EEPROM存储单元进行“写入”操作,就是将浮栅中电子释放的过程(不要把“写入”与“擦除”操作弄反了),如下图所示:

如上图所示,将FLOTOX管的源极悬空,漏极接高压(不小于12V),而控制栅极接地,则浮栅与漏极之间形成负向强电场,电子从浮栅通过隧道氧化层回到漏极放电。 配合对应的选通管,则一个bit位的存储单元电路状态如下图所示:

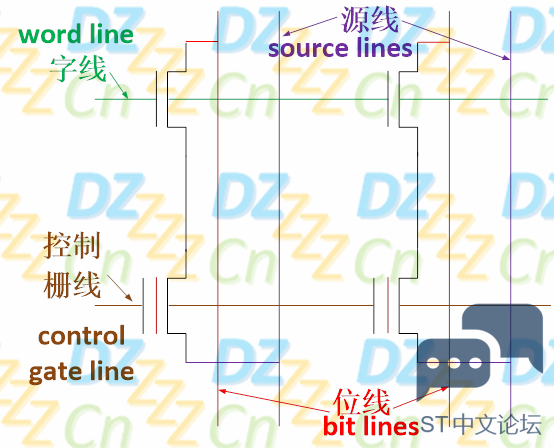

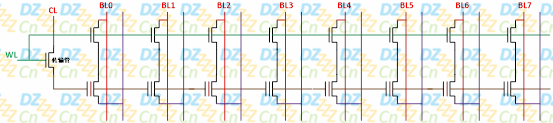

多个bit位组成的存储单元阵列如下图所示:

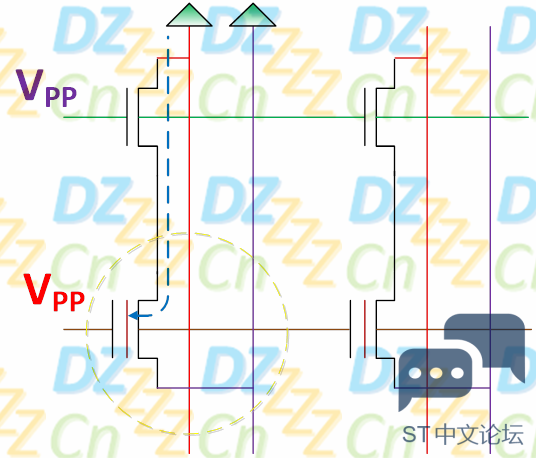

当进行存储单元的“擦除”操作时,源线(Sources Lines, SL)与位线(Bit Lines, BL)均为低电平,而控制栅线(CL)为高电平(不小于12V),当对应存储单元的选通管打开时(Word Line, WL=VPP),如下图所示:

当进行存储单元的“写”操作时,位线为高电平(不小于12V),而源线悬空且比Program Gate Line为低电平,当对应存储单元的选通管打开时(SG=VPP),如下图所示:

每8个存储单元配置一个高压传输管,则一个字节的存储阵列如下图所示:

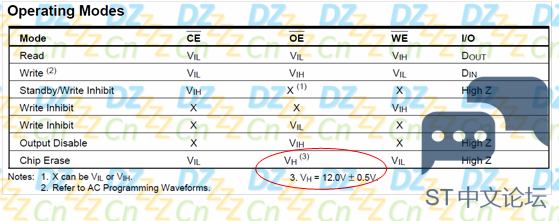

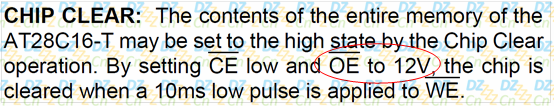

很明显,EEPROM的“擦除”与“写入”操作均需要高压(强电场)进行浮栅电子的注入或释放,而一般的EEPROM芯片为5V供电,那么这些高压从何而来?对于并行EEPROM芯片,有专用的引脚可作为擦除功能的高压供电端,下图来自ATMEL并行EEPROM型号AT28C16数据手册:

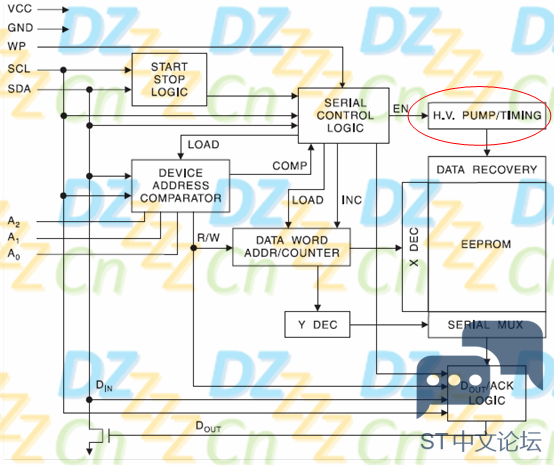

可以看到,在进行“擦除”操作时,需要在OE(Output Enable)引脚接入12V的高压。 但是串行EEPROM就没这么幸运了,比如我们最常用的AT24CXX系列EEPROM芯片,通常是3.3V或5V供电的,而且对外的接口通常是I2C串行总线那样的两根线,那高压从何而来?有人想到了升压电路,没错,下图来自ATMEL串行EEPROM型号AT24C02数据手册:

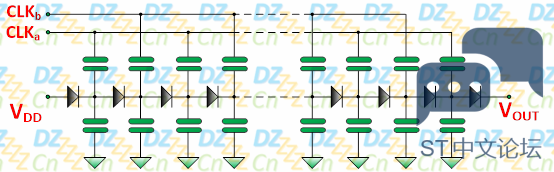

其中,H.V. PUMP(High Voltage Pump)就是高压泵(升压)电路,升压电路有很多种,比如整流倍压、变压器升压、BOOST升压、电荷泵等,但是,在集成电路设计中无法做成大容量电容与电感,因此,只有电荷泵电路比较适合片内升压,它的基本电路如下图所示:

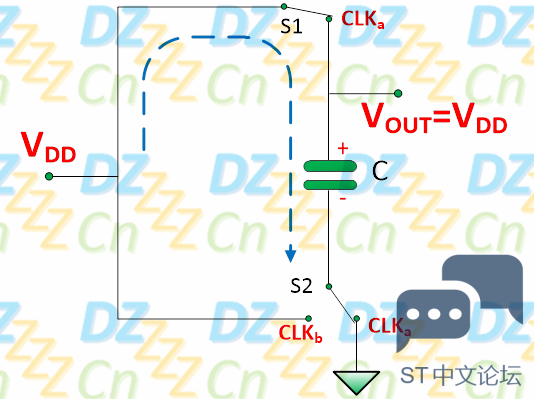

我们分析其中一级就明白其升压原理了,如下图所示(原理与“整流倍压电路”类似,可参考《整流电路》文章):

在时钟周期CLKa期间,开关S1闭合,S2与地相连接,此时电容充电至VDD。

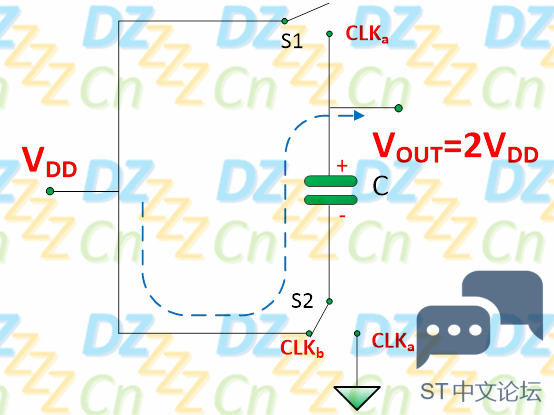

在时钟周期CLKb期间,开关S1打开,S2与电源VDD连接,此时电源VDD与电容C的电压串联起来对外供电,此时VOUT=为时源VDD的两倍,即2×VDD。 在集成电路设计中,可以使用NMOS或PMOS实现开关功能,电容则可使用MOS电容(即栅极作为一个极,而源极与漏极连接作为另一个极板),而二极管则用MOS管代替,如下图所示:

实际的电荷泵电路有很多种结构,如多相时钟电荷泵、CTS电荷泵、栅交叉耦合衬底偏置电荷泵等等,读者可自行参考相关文档,此处不再赘述。 那怎么样实现数据的“读取”操作呢?当浮栅中注入(充电状态)或释放电子(放电状态)时,存储单元的阀值电压会发生改变,如下图所示:

在读取存储单元时,我们可以在控制栅上加一个中间电平,其值介于两个阀值Vth之间,这样浮栅有电子的高开启管不能导通,而浮栅放电后的低开启管能正常导通,由此分辨出单元存储的数据是“1”还是“0”。 |

微信公众号

微信公众号

手机版

手机版