.png) STMCU小助手

发布时间:2021-11-7 15:19

STMCU小助手

发布时间:2021-11-7 15:19

|

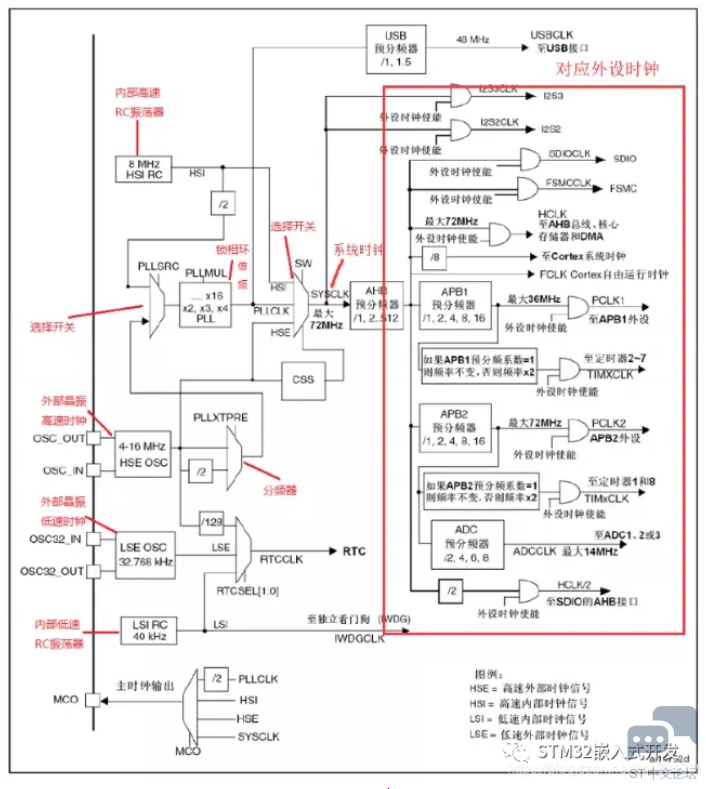

STM32的时钟树 时钟信号推动单片机内各个部分执行相应的指令,时钟就像人的心跳一样。 STM32本身十分复杂,外设非常多,任何外设都需要时钟才能启动,但并不是所有的外设都需要系统时钟那么高的频率,如果都用高速时钟势必造成浪费。同一个电路,时钟越快功耗越大、抗电磁干扰能力越弱。复杂的MCU采用多时钟源的方法来解决这些问题。如下图,是STM32的时钟系统框图。

如上图左边的部分,看到STM32有4个独立时钟源,HSI、HSE、LSI、LSE。

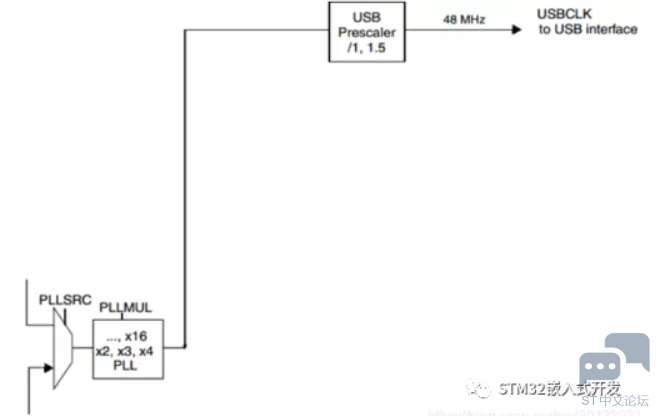

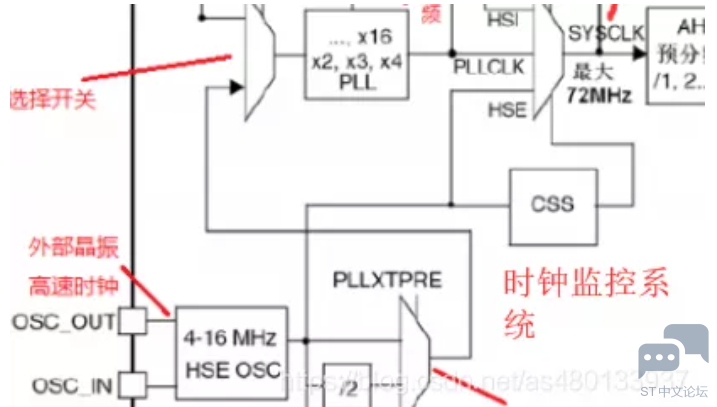

时钟树的右边红色框中,则是系统时钟通过AHB预分频器,给相对应的外设设置相对应的时钟频率。 其中LSI、LSE是作为IWDGCLK(独立看门狗)时钟源和RTC时钟源使用。而HSI、HSE以及PLLCLK经过分频或者倍频作为系统时钟SYSCLK来使用。 PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。通过倍频之后作为系统时钟的时钟源。 配置时钟 默认时钟 Keil编写程序是默认的时钟为72Mhz,其实是这么来的: 外部高速晶振HSE提供的8MHz(大小与电路板上的晶振相关)通过PLLXTPRE分频器后,进入PLLSRC选择开关,进而通过PLLMUL锁相环进行倍频(x9)后,为系统提供72MHz的系统时钟SYSCLK。之后是AHB预分频器对时钟信号进行分频,然后为低速外设提供时钟。相关文章推荐:时钟失效之后,STM32还能运行? 内部RC振荡器HSI为8MHz,2分频后是4MHz,进入PLLSRC选择开关,通过PLLMUL锁相环进行倍频(最大x16)后为64MHz。 USB时钟

如上图,STM32的USB时钟不能超过48MHz,因此如果时钟源为72MHz,就需要进行1.5分频。 如果时钟源为48MHZ,则进行1分频即可。 把时钟信号输出到外部![UGW6W[1`14PX8PV_D`]}J@3.png UGW6W[1`14PX8PV_D`]}J@3.png](data/attachment/forum/202111/07/151813l6mdij6ae5ceik5k.png)

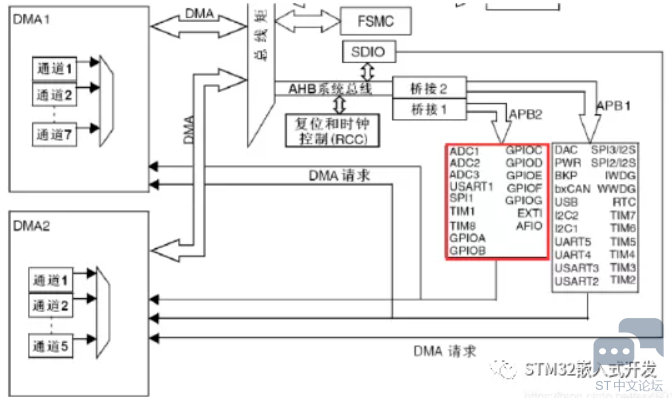

STM32可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟,可以把时钟信号输出供外部使用。 AHB分频器 如时钟树图右边的部分,系统时钟通过AHB分频器给外设提供时钟。从左到右可以简单理解为: 系统时钟->AHB分频器->各个外设分频倍频器->外设时钟的设置。 右边部分为:系统时钟SYSCLK通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

F1系列中,APB1上面连接的是低速外设,包括电源接口、备份接口、CAN、USB、I2C1、I2C2、USART2、USART3、UART4、UART5、SPI2、SP3等。 APB2上面连接的是高速外设,包括UART1、SPI1、Timer1、ADC1、ADC2、ADC3、所有的普通I/O口(PA-PE)、第二功能I/O(AFIO)口等。 具体可以在stm32f10x_rcc.h中查看外设挂在哪个时钟下。 时钟监视系统(CSS)

另外,STM32还提供了一个时钟监视系统(CSS),用于监视高速外部时钟(HSE)的工作状态。倘若HSE失效,会自动切换(高速内部时钟)HSI作为系统时钟的输入,保证系统的正常运行。 |

微信公众号

微信公众号

手机版

手机版