.png) STMCU小助手

发布时间:2021-11-11 22:00

STMCU小助手

发布时间:2021-11-11 22:00

|

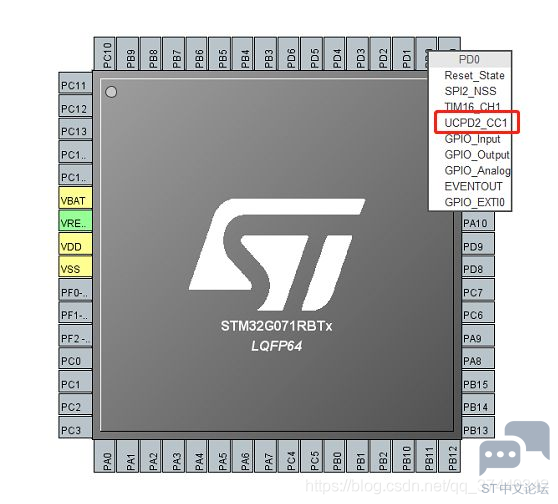

项目场景: STM23G070单片机的PD0引脚作为开漏输出的时候,外部接了一个51K上拉电阻到5V,想让PD0开漏输出高的时候是5V,开漏输出低的时候是0V。 问题描述: STM23G070单片机的PD0引脚作为开漏输出的时候,外部接了一个51K上拉电阻到5V,单独测试PD0的时候是可以正常的,开漏输出高的时候5V,低的时候可以到0V,但是一旦PD1推挽输出输出高之后,情况就变了,在PD1推挽输出高情况下,PD0开漏输出高的时候却始终只有2.4V,输出低的时候是0V,正常的。

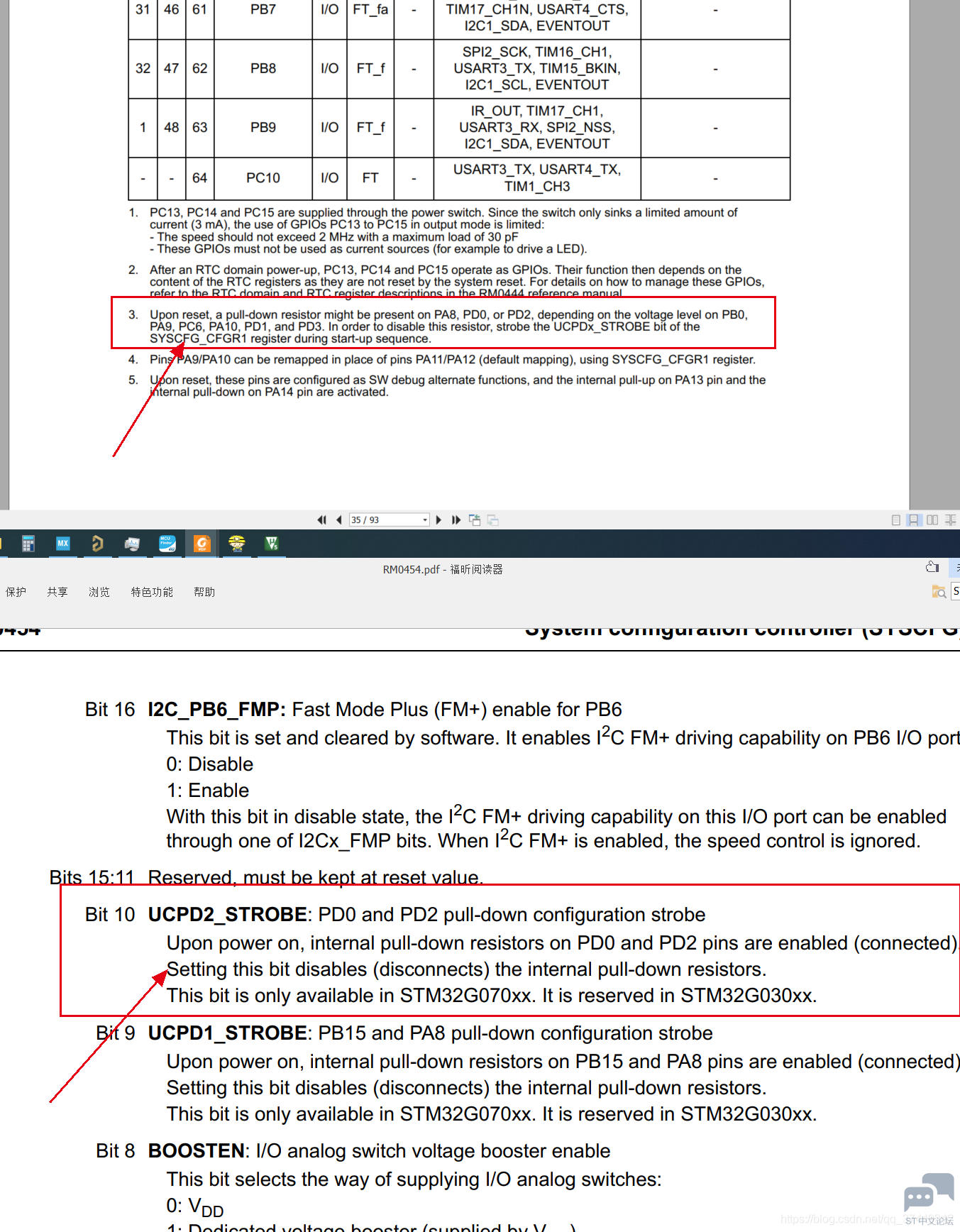

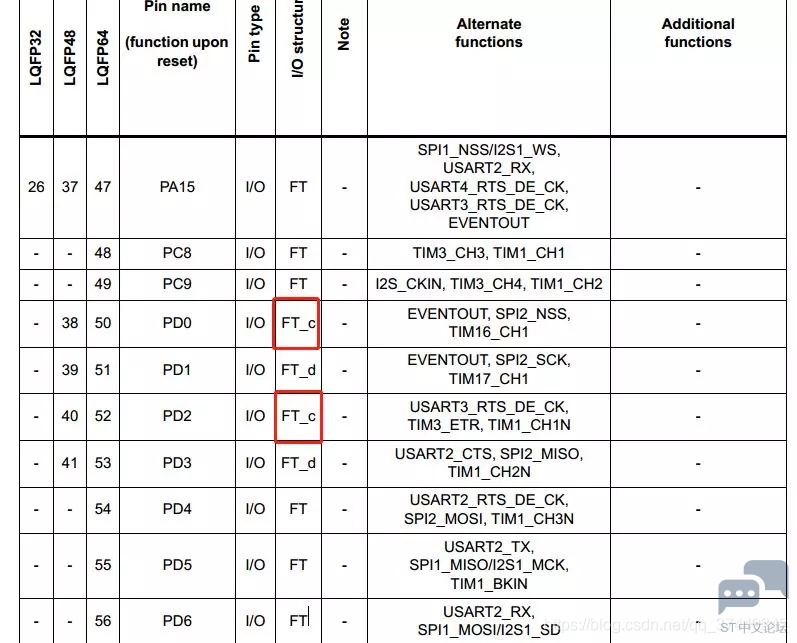

原因分析: 查阅STM32G0数据手册可知

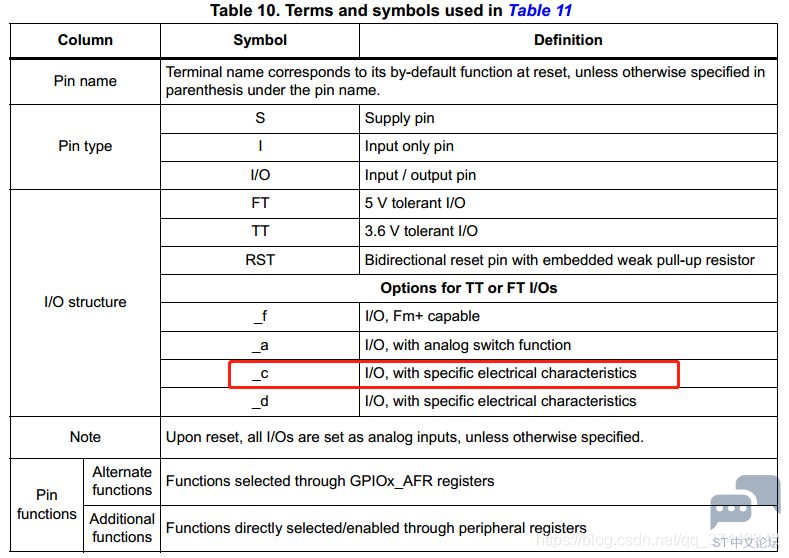

这个引脚的电平类型为FT_c,我们知道FT是容忍5V的意思,那么FT_c是什么意思?不妨看看说明:

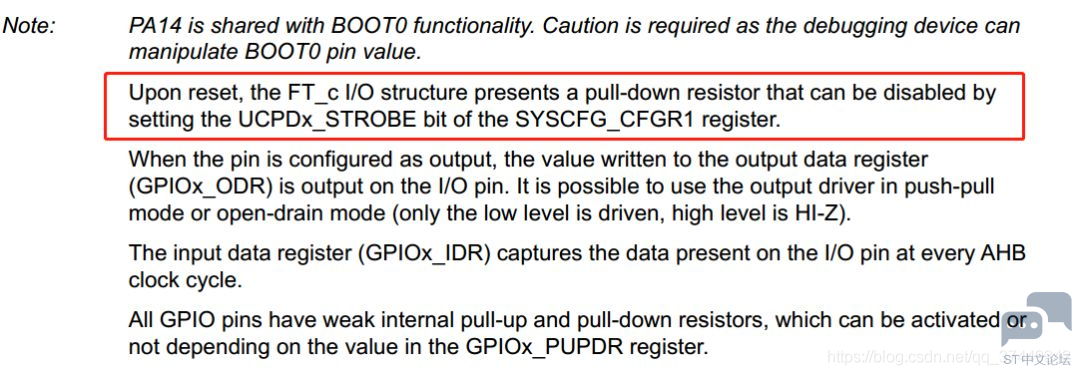

然后去用户手册查看GPIO相关说明,找到以下内容:

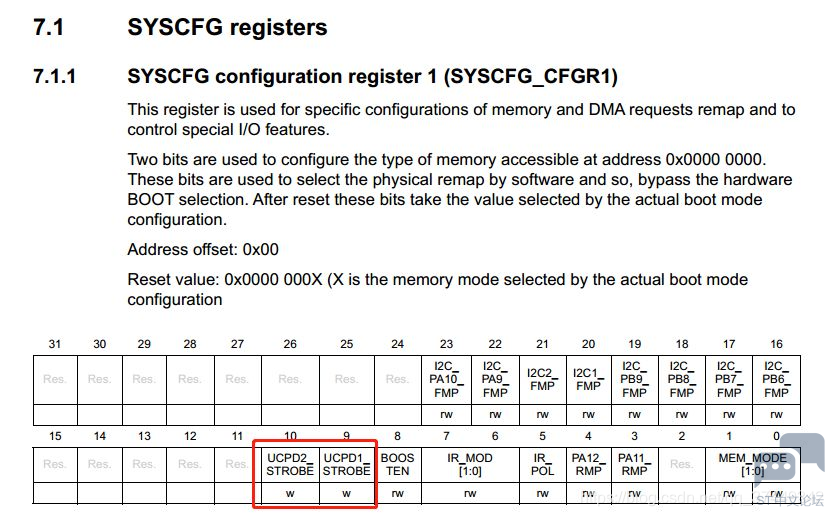

基本上了解状况了,再看一下相关寄存器说明:

解决方案: 看了以上说明,基本明白怎么操作了。在初始化IO的时候,应该把SYSCFG registers的UCPD2_STROBE位设置一下就ok了。

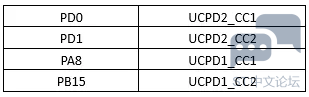

其实PA8和PA15也是这样的。如果我们不需要这个下拉电阻,需要按照上面的操作调整一下。

即TYPE-C充电管理的相关引脚,所以才会有这样的设置。若想进一步了解TYPE-C相关知识,可以自行查找相关资料。 |

微信公众号

微信公众号

手机版

手机版