.png) STMCU小助手

发布时间:2022-1-29 18:28

STMCU小助手

发布时间:2022-1-29 18:28

|

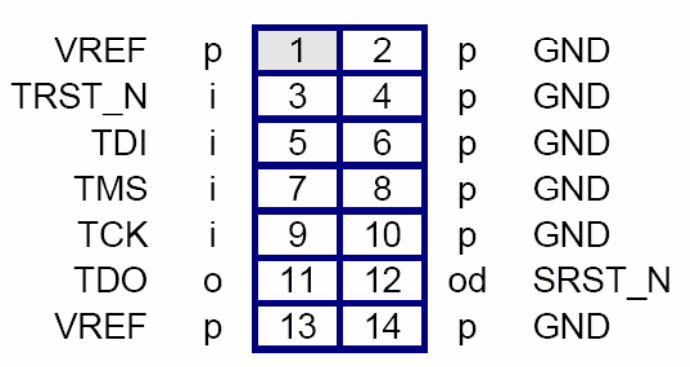

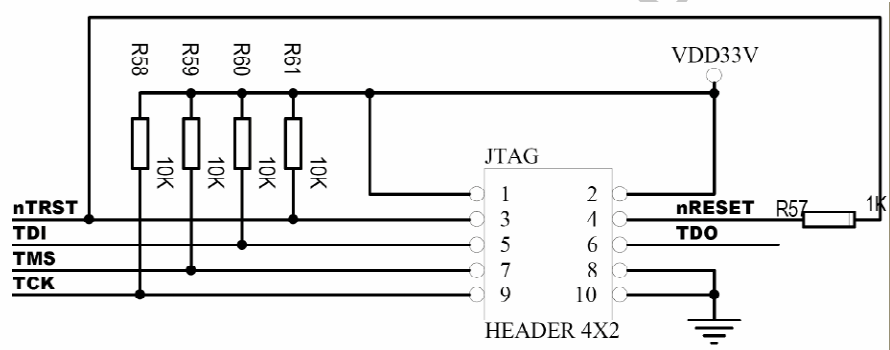

一、JTAG模式 这种模式一般有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的。值得注意的是,不同的IC公司会自己定义自家产品专属的Jtag头,来下载或调试程序。 Test Clock Input (TCK) -----强制要求1:TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 Test Mode Selection Input (TMS) -----强制要求2:TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。 Test Data Input (TDI) -----强制要求3:TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。 Test Data Output (TDO) -----强制要求4:TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。 Test Reset Input (TRST) ----可选项1:这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。 (VTREF) -----强制要求5:接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?) Return Test Clock ( RTCK) ----可选项2:可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。 System Reset ( nSRST)----可选项3:可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。 USER IN:用户自定义输入。可以接到一个IO上,用来接受上位机的控制。 USER OUT:用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态 由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

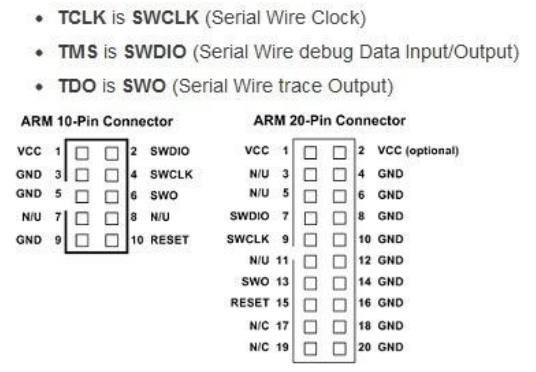

上述Jtag头的管脚名称是对IC而言的。例如TDI脚,表示该脚应该与IC上的TDI脚相连,而不是表示数据从该脚进入download cable。 实际上10针的只需要接4根线。4号是自连回路,不需要接。1和2号接的都是1管脚;而8和10接的是GND,也可以不接。 二、SWD模式 在给STM32烧写程序调试的时候,传统20脚JTAG底座个头大,占用PCB面积多,连接线复杂。 采用SWD模式Jlink,只需要三根线即可与目标板实现通讯,可实现程序下载,单步调试等功能,除了不能检测目标板电压、不能给目标板供电、速度有所降低之外,与完整版JLink的功能是一样的。

20脚JTAG底座, 只需要 SWDIO、SWCLK、GND三根线,即 7号、9号及GND 中的任意一根针。由于固件烧写一次后就不再使用(掉固件的可能性非常低),因此不需要再焊排针上去了,杜邦排针连接即可。 对于全功能JLink,1号针脚的功能有两个:检测目标板电压;为内部的电平转换芯片提供输出端参考电压。也就是说,如果目标板电压为3.3V,那么这里也必须给1号针脚提供3.3V电压,才能保证正常输出。由上图可知,20针JTAG的2号针可以提供VCC供电。打开J-Link Commander输入power on时,发现2号针脚输出的是5V电压,无法通过直接短路1、2号针来解决问题。所以必须给目标板上Jlink连接器的1号管脚提供3.3V的电压,可以在Jlink中获取,也可以在待烧写的板子中获得,这与三线SWD下载模式无关。 烧写程序接线顺序:插杜邦排针,原始JLink上电,待编程、烧写器上电(USB)。断开时步骤相反,切不可颠倒!尤其不能在上电时断开上图中的连接,否则会烧坏器件! |

STM32G0 系列 I2C 通信异常典型案例分析与解决方案总结

经验分享 | LAT1490 两个STM32G0 I2C 通信异常的案例分析

经验分享 | STM32G0 I2C bootloader Go 命令后调试连接失败:DBG_SWEN 位复位修复

经验分享 | STM32G0B1 待机模式意外唤醒深度解析:RTC 结构体未初始化的隐形坑

经验分享 | STM32G0B1 待机模式意外唤醒深度解析:RTC 结构体未初始化的隐形坑

如何在STM32和Arduino上实现卷积神经网络

STM32与51单片机差异一文速览

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

【STM32入门学习路径指南】(四步走)

微信公众号

微信公众号

手机版

手机版