|

应用示例 来自我们的实验室 电源 2025年12月17日 / 阅读时长:5分钟 /

SiP挑战一:可靠焊点 空洞问题

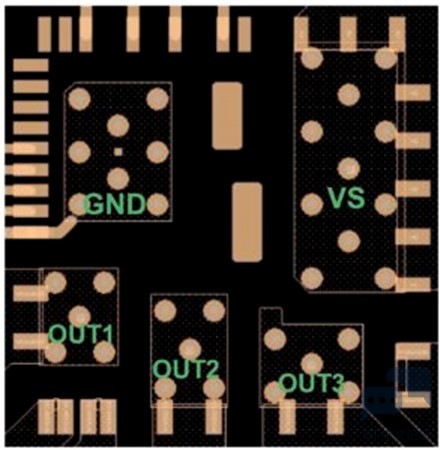

PWD5T60的SiP封装 最常见的关注点在于形成无空洞的可靠焊点。确实,仅简单涂抹焊膏并加热器件并非最优方案,因为SiP极易出现错位、过量的焊膏会造成两个焊盘桥接,或者是在回流焊过程中残留气体形成空洞。这些缝隙会导致散热不良引发过热,并降低良率,成为严重隐患。鉴于SiP器件通常配有大面积裸露焊盘用于散热,会进一步加重该问题。根据IPC(国际印制电路协会)的传统指导标准,空洞面积不应超过裸露焊盘面积的50%,但在缺乏适当工艺支持的情况下,这一标准往往难以实现。梳状开窗

PWD5T60的梳状开窗设计 意法半导体推荐的第一个解决方案是回归基础:将封装件存放于防潮袋中,并确保防静电环境。这听起来或许过于简单,但如果装配线受到潮湿环境的影响,任何补救措施都将无济于事。下一步是选择合适的钢网进行作业。相较于全开窗(模拟裸露焊盘尺寸的大面积方形开窗)或方格阵列(以多个小方格填充区域),采用开口宽度300 µm、间距600 µm的梳状开窗结构能获得最佳效果。根据IPC标准,所有尺寸大于4 mm × 4 mm的裸露焊盘均应采用图形化开窗设计。因此,选择正确的开窗方案至关重要。钻孔导通孔

PWD5T60顶层PCB的导通孔布局

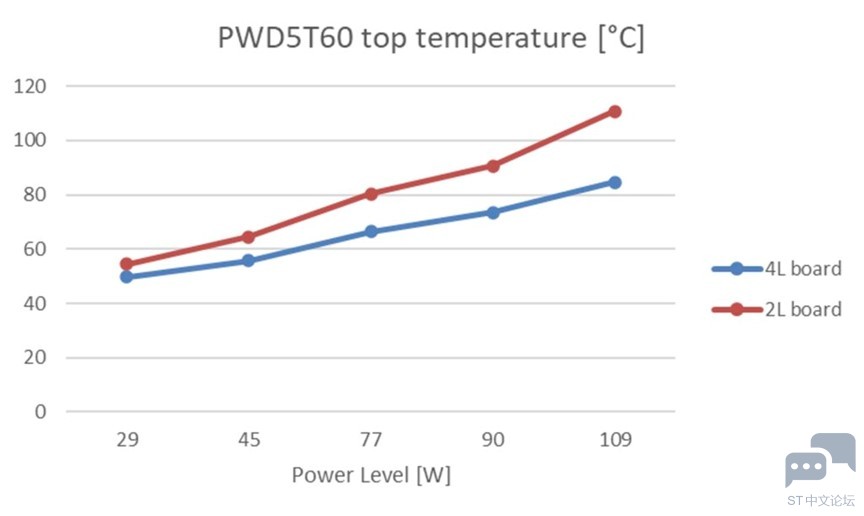

空洞现象与钢网开窗类型的对应关系 传统设计指南的局限 SiP封装的独特之处正是其吸引力所在。它能够在纤薄的封装内容纳多种不同芯片,从而减少PCB上各类器件的整体占用面积并简化设计。为实现这一目标,SiP采用了中介层、重布线层、桥接技术等多种先进工艺。这意味着工程师需要以不同的方式处理它们。这类封装通常不配置散热器(我们的所有器件均如此),热量主要通过底部焊盘进行耗散。因此,其在PCB上的布局方式需与传统封装区别对待。若直接沿用其他封装的设计准则,将易导致过热、短路及可靠性降低等问题。 构建散热岛并采用四层PCB 我们向制造商最常建议的方案之一是构建“散热岛”——即在裸露焊盘下方的PCB层设置厚铜层,以更有效地将热量从源头导出。这实质上是工程师可通过导通孔连接的人造散热结构,能显著增强散热性能。铜层的数量也取决于PCB的总层数。因此,值得考虑从双层结构升级为四层结构。虽然四层PCB的生产成本更高,但它使设计人员能够采用更具性价比的SiP方案,在满足散热目标的同时提高整体元件密度,从而降低总成本。 实际上,我们使用PWD5T60进行了内部基准测试,以展示在设计风扇电机时,从四层PCB转为双层PCB所产生的影响。在29 W功率下,采用四层PCB可使意法半导体器件的表面温度降低8.6%;而在110 W时,温差超过30%。尽管PWD5T60在125 °C的额定结温范围内仍可运行,但双层PCB方案已极其接近其温度极限。事实上,在另一款压缩机电机设计中,双层PCB甚至无法承载90 W的功率。因此,工程师通过增加PCB层数可获得显著优势,而探索更厚的PCB设计也将带来可观的回报。

四层与双层PCB上PWD5T60在不同负载下的表面温度测量表

四层与双层PCB上PWD5T60在不同负载下的表面温度变化曲线图 新的电气设计考量

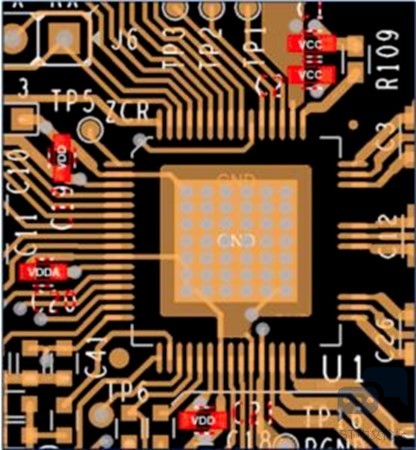

去耦电容布局示例 还需兼顾其他布局因素,例如接地连接。由于微控制器驱动着SiP的功率级,将接地点连接至分流电阻以抑制电压尖峰至关重要。我们同时建议将所有接地焊盘与裸露焊盘连接至电源组件正下方、信号层上方的实心接地层,从而有效屏蔽电磁干扰。将大容量电容尽可能靠近SiP布置,并使去耦电容尽量贴近电源引脚,也能有效降低寄生电感与电阻。总的来说,这些设计要点清晰直观,在设计中充分考量即可显著缩短项目的上市周期。 |

微信公众号

微信公众号

手机版

手机版