|

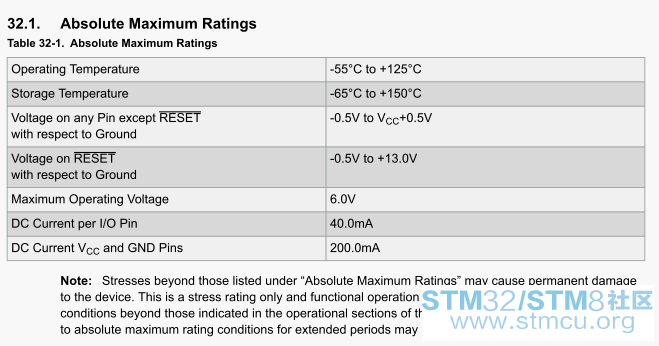

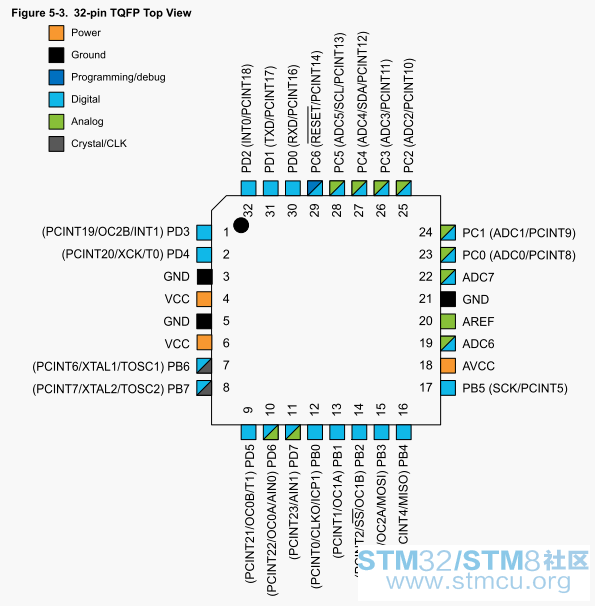

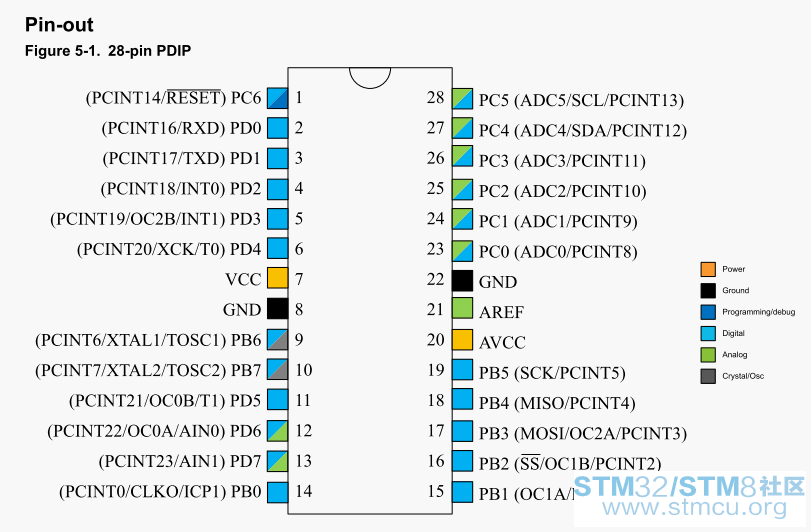

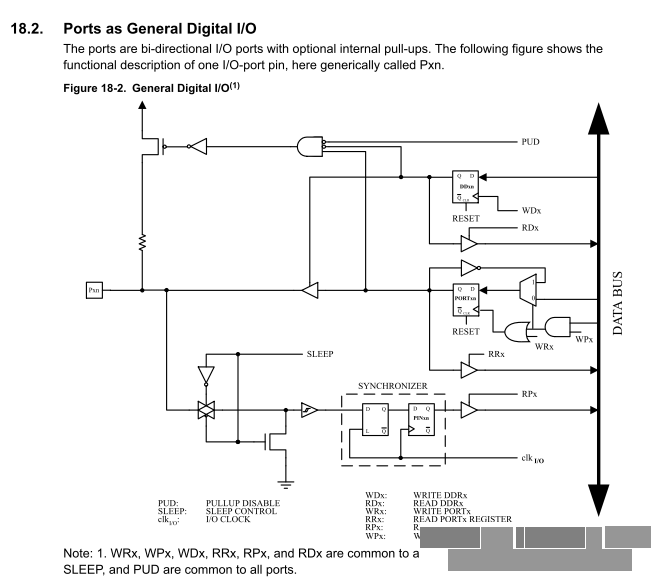

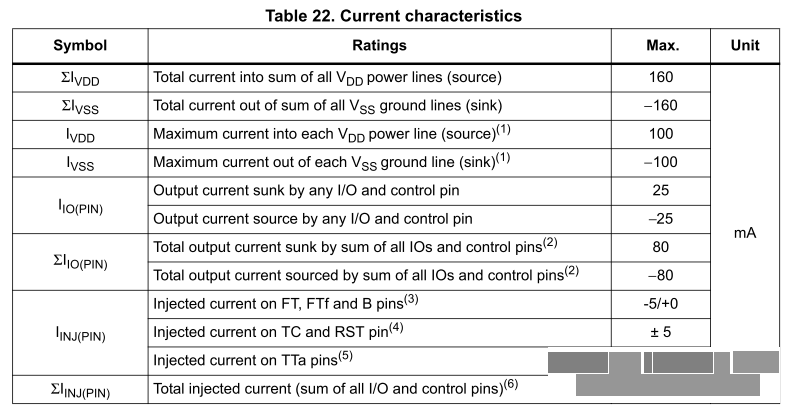

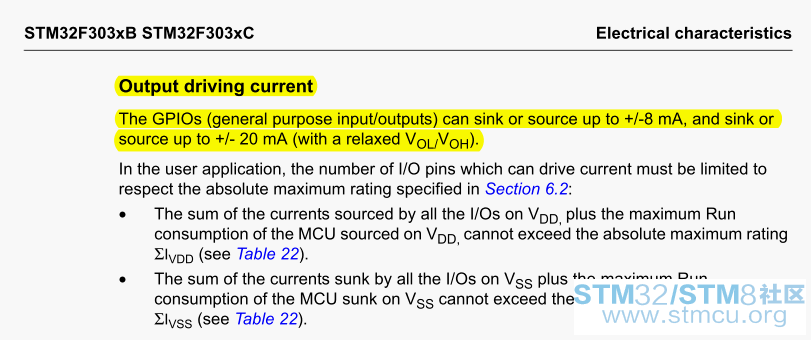

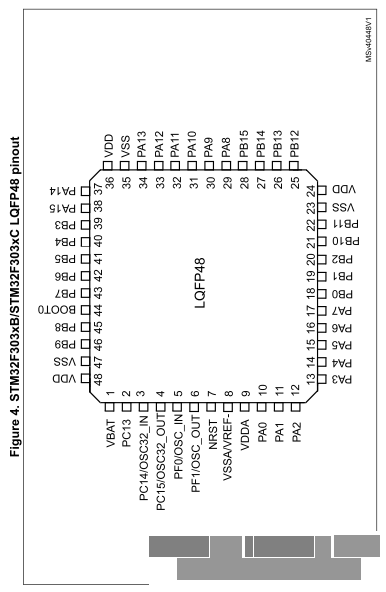

本帖最后由 evanwuuuu 于 2017-11-4 12:03 编辑 大家好,想请教MCU有关sink current,source current方面的问题。以下本人以尽最大的努力来进行排板以及解释清楚我的问题所在,敬请各位前辈帮助小弟一把 首先我本来是在看Arduino uno搭载的ATMEGA328P资料 我对于汇流,源电流方面的理解程度不高,主要知道差别在于电流方向的不同,以及驱动能力的不同 首先我查询了ATMEGA328P datasheet中有关灌电流,拉电流,每I / O引脚MAX。目前等等的资讯 由图1中得知(来源自datasheet,第365页,连结),单一I / O口所能流过的最大电流为40mA,流经VCC与GND的最大电流限制为200mA 首先我针对我理解的部分进行说明(假定晶片电源由AMS1117-5.0提供,且晶片本身运行时自耗耗8mA) Source current: 假设我们使用拉电流的电路配置,并且负载为LED灯,则电流自AMS1117-5.0输出后,由晶片内部的VCC经过假设LED的电流为20mA,则我使用了(20mA + 8A)/ 200mA。在此情况下,电流会同时流过晶片的VCC与GND Sink current: 再来我们将电流换成sink current的电路配置,并且LED与限流电阻的电源由AMS1117-5.0供应,当我将I / O拉低时电流会经由AMS1117-5.0输出端口流经LED,限流电阻,灌入晶片I / O口再从晶片的GND流出去形成回路。针对LED的电流路径而言,20mA没有流过晶片的VCC端口,但VCC端口还是有8mA用做晶片本身运行消耗。 由上述电流路径分析,得知若为拉电流的配置,共有28mA流过晶片的VCC与GND。 问题1:请问以下我的描述是否正确? 若为灌电流的配置,则VCC仅流过8mA,GND则流过28mA。 问题2:据图1中的描述“直流电流VCC和GND引脚= 200mA”,是否将VCC与GND分开来看?也就是VCC有200mA,GND有200mA 在灌电流的电路配置中,VCC使用了8mA / 200mA; GND使用了28mA / 200mA 问题3:请问以下我的描述是否正确? 假设上述中对于VCC,GND流过的电流大小分析无误,则可以知道无论sink or source的配置GND的电流都是相同的。所以在此处的“DC Current VCC and GND Pins”该项参数,可以被延伸解释为“所有I / O口加总的电流限制”(考量晶片运行本身的消耗可小到被忽略) 问题4:请教哪个才是正确的? 由于Arduino UNO早期为DIP的封装形式(图2_1),后来改成TQFP_32pins(图2)。由于两脚脚位配置可以看出,DIP封装在7,8脚位具有一组VCC与GND,而在22脚位也有一个GND(我认为应该写成AGND较合适);而TQFP封装在3,4,5,6脚位具有两个VCC与GND,21脚还有一个GND(AGND)。我认为TQFP封装具有两组VCC与GND的原因就是因为贴片型的脚位较细,所以需要用两组来来让200mA通过(例如一组分担100mA)。但我在此处看到有人具有不同的论点,认为一个VCC(或是GND)就算200mA。以DIP封装举例,则具有“1 VCC引脚:表示这些Arduinos能源总共200 mA”,“2 GND引脚:表示这些Arduinos可以共享400 mA “;若该人论点才是正确的,那TQFP_32pins封装Source current不就可以到400mA,Sink current to 600 mA? 题外话问题5:请教为什么常看到“MCU的Sink电流能力通常大于Source current”? 假设I / O口是推挽输出结构,那无论不是流过内部的MOSFET?若以MOS可承受的功率来思考的话两个配置不都是流过一个MOS吗?还是说这有关PMOS,NMOS本身特性? 题外话问题6:图3为ATMEGA328P的I / O结构图,因为之前有使用过STM32F3,其结构图很明显的可以看到推挽(或OD)输入/输出的结构,但在图3中我就看不出该晶片的I / O是怎样的结构(push-pull?)。 问题7:请教哪个才是正确? 鉴于于这一两天我在网上找这些问题的答案,但都没有找到我认为适合的解答,想起之前曾用过STM32系列但总没关心过sink,source current。所以我去查了查STM32F3根据图4得知“Maximum current into each VDD power line (source)(1) = 100mA”以及“Total current into sum of all VDD power lines (source) = 160mA”,虽然没有到三倍图6为48脚,具有三组VDD和VSS),但这似乎映证了几组VCC和GND就能有几倍电流承受能力的论点,我还是不怎么确定哪个才是正确的。 问题8:接着我看到I / O的部份“Output current source by any I/O and control pin = -25mA”以及“Total output current sourced by sum of all IOs and control pins(2) = -80mA” 。假设上述的数据我都以最大值来进行思考。I / O口弄到极限的80mA,这样是否代表STM打算留下“160mA - 80mA”的余裕用来给晶片运行? [Total current into sum of all VDD power lines (source) 扣 Total output current sourced by sum of all IOs and control pins(2))扣掉 问题9:由(图4)数据可看出接收电流和源电流能力相同,经查询后发现比较近代的MCU多半两个能力都是相同的,而以前的51系列才有接收电流较大的特性存在。但我在(图5)中又看到不同的数据,且也不是25毫安。黄标的部份不知道是本人英文太差还是有某些观念欠缺,搞不懂是在讲什么 |

Fig.1

Fig.2

Fig.2_1

Fig.3

Fig.4

Fig.5

Fig.6

微信公众号

微信公众号

手机版

手机版

评分

查看全部评分

DC Current per I/O Pin :40ma --> 说的是每个引脚能承受的最大电流为40ma;

DC Current VCC and GND pins:200ma --> 应该是说芯片所有的i/o以及外设的驱动电流总和的最大值。

个人想法,仅供参考

评分

查看全部评分

问题1,我觉得是正确的。

问题2,我觉得应该理解为,允许流过芯片的总电流。

问题3,应该是正确的。

问题4,我觉得,应该是利用引脚来分流。

问题5,我觉得灌和拉电流在物理属性上应该是一样大小的。

但是由于拉电流在引脚为L时,容易出现倒灌现像(在上拉电阻的作用下),所以一般不建议设置过大的电流。

问题6,不同厂家对产品的描述方法不一样。具体还得看手册。

问题7,单个VDD(一个VDD引脚)最大可以流过100mA,全部VDD引脚总共可以流过160mA,已经说的很明白了,有什么问题?

问题8,任意I/O引脚允许流经 25mA,所有IO累加不能超过80mA。可能也考虑到散热问题吧。

问题9,虽然I/O能轻松流过20mA,但是,推荐使用8mA左右的电流。

一般情况下,推荐使用外加三极管控制相对大电流的负载,

如果驱动小量LED,我一般用5~8mA电流直接控制,如果嫌不够亮,可以买高亮的LED。

如果量大,还是推荐使用三极管,或者其它开关类芯片驱动。

评分

查看全部评分