|

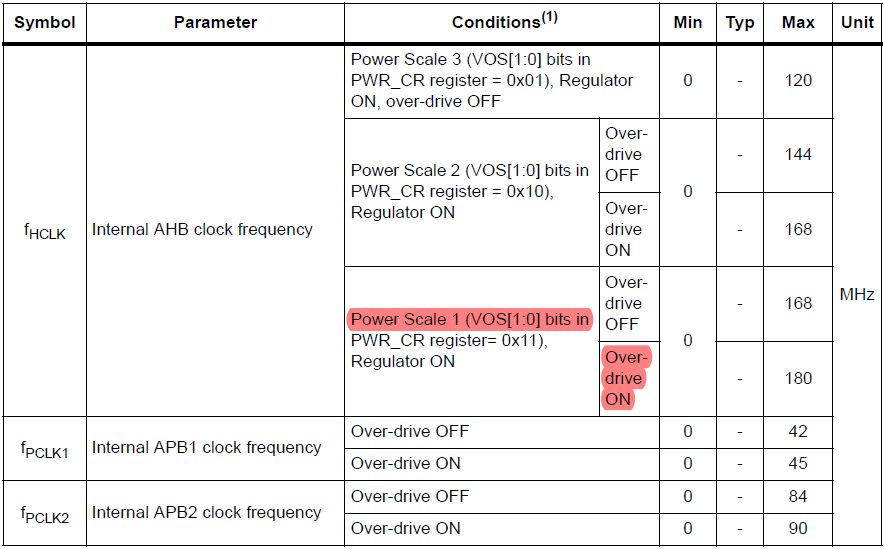

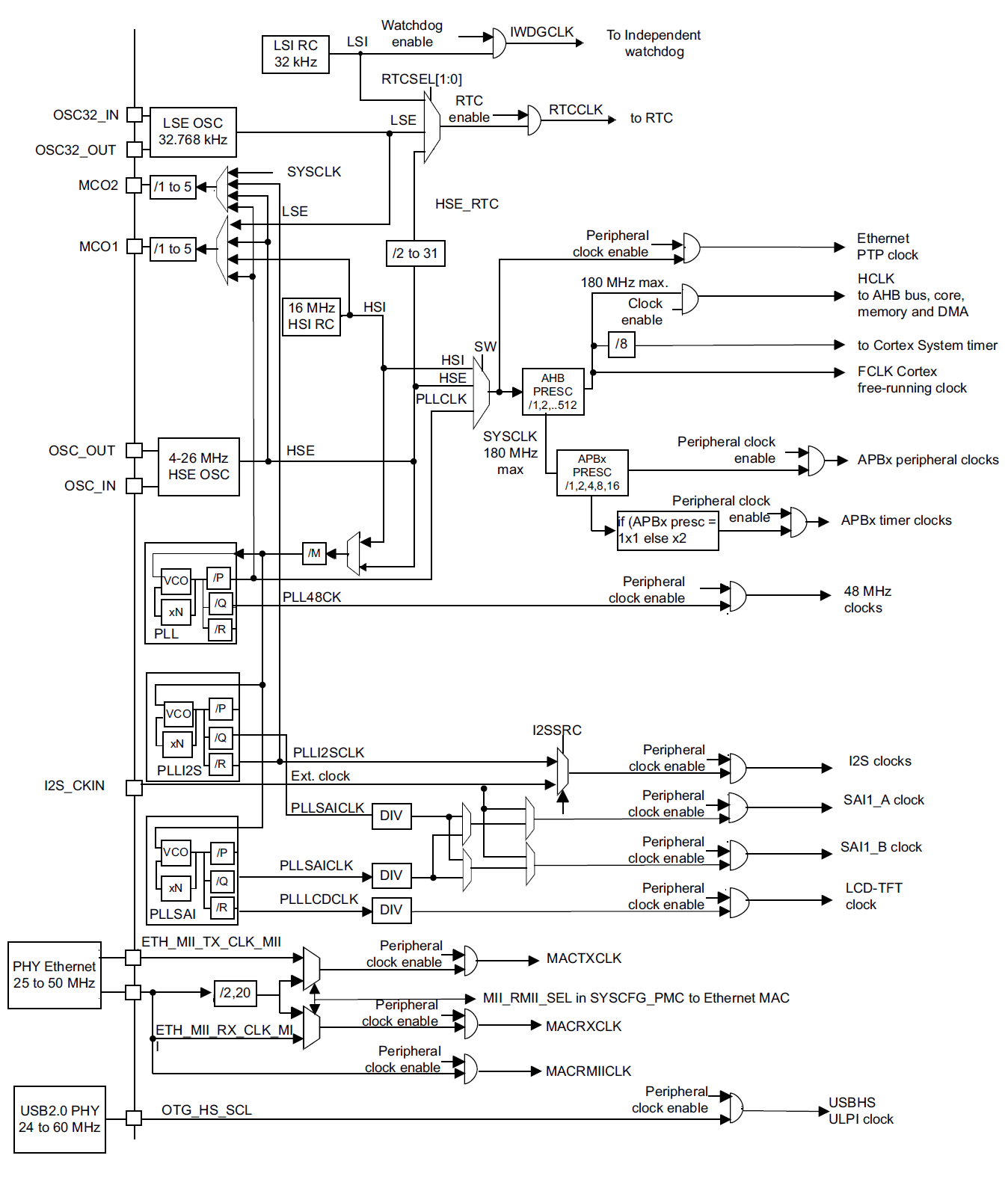

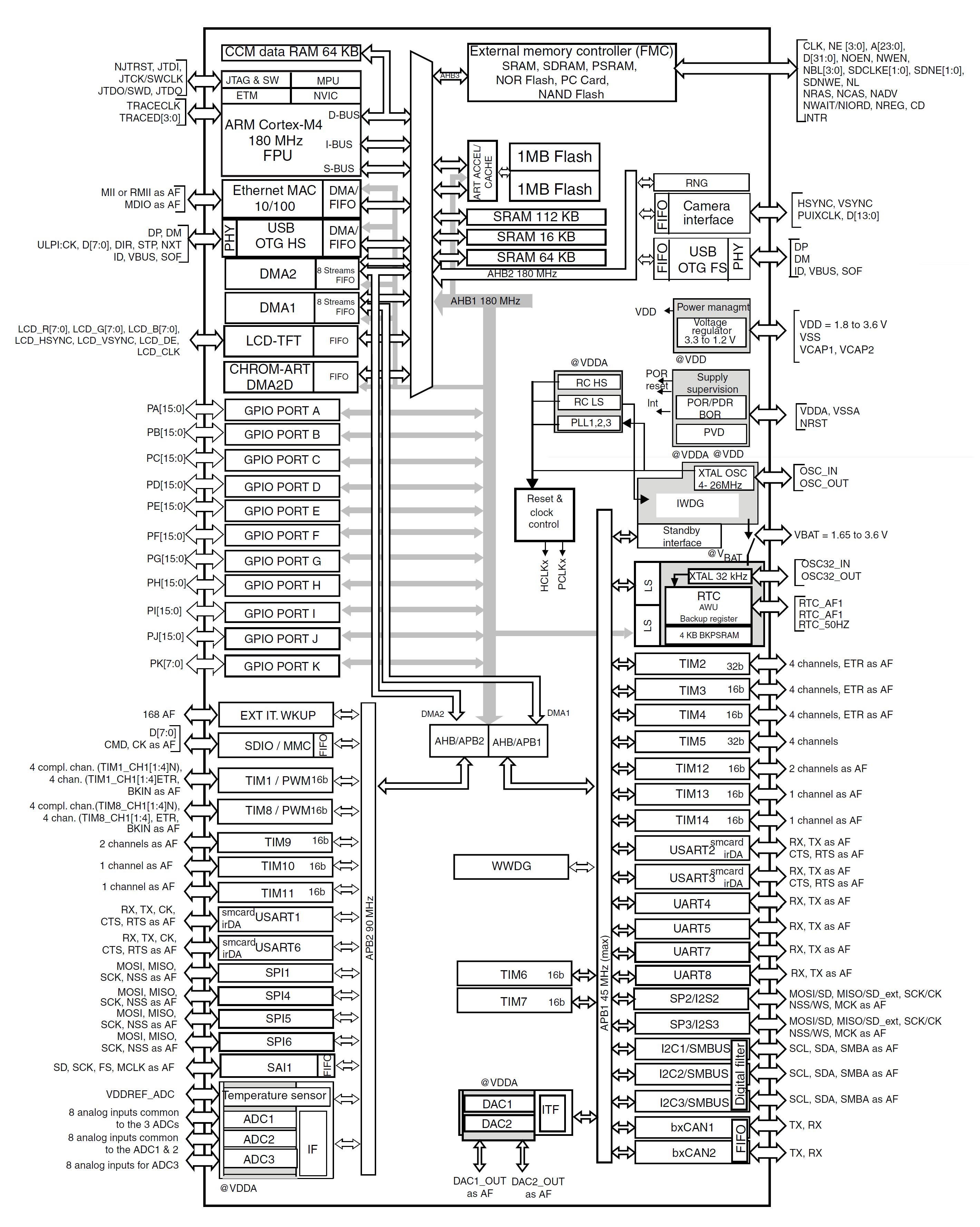

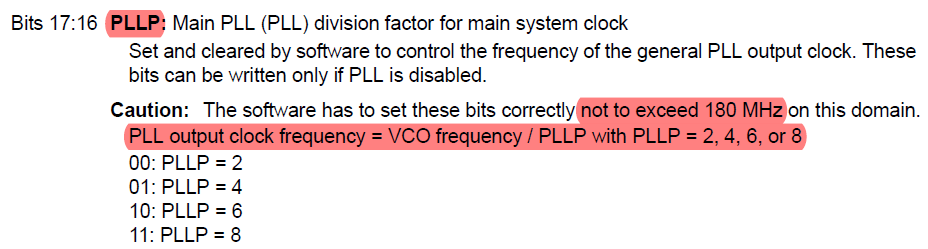

时钟,也就是给芯片提供节拍的东西,芯片各个组件根据时钟节拍执行着各自的工作,并且根据时钟节拍进行相互合作。其实说白了就像干活时喊的号子一样,“一二一二......”大家根据号子声一起使劲,相互合作。 STM32的时钟不像8051的那么简单,但是也不像飞思卡尔芯片的那么复杂。总体来说STM32的时钟树走向清晰。 接下来我将按照从前到后的顺序进行讲解: l 首先我们追根溯源,看看STM32的时钟源,STM32一共有4个时钟源,分别是: Ø LSI内部低速时钟 Ø HSI内部高速时钟 Ø LSE外部低速时钟 Ø HSE外部高速时钟 但是只有HSE和HSI能够用来作为内核时钟源,另外两个时钟源只能够用来给实时时钟和看门狗提供时钟。 在本例程中选用外部高速时钟作为时钟源,因此需要置位RCC_CR[HSEON]来打开HSE时钟,除此之外还有一个标志位RCC_CR[HSERDY]用来指示HSE是否准备好。 RCC->CR |= ((uint32_t)RCC_CR_HSEON); /* 使能 HSE */ do { HSEStatus = RCC->CR & RCC_CR_HSERDY; }while (HSEStatus==0); /* 等待外部时钟稳定 */ l 接下来我们可以看到一个多路选择器,它的作用是用来选择内核时钟源,STM32一共有3个时钟可以用来驱动内核(SYSCLK): Ø HSI内部高速时钟 Ø HSE外部高速时钟 Ø PLL时钟 它们通过RCC_CFGR[SW]位进行选择,除此之外同样还有一个标志位RCC_CFGR[SWS]用于标志选择成功与否。 很显然,使用HIS和HSE直接作为内核时钟源是不切实际的,频率太低,因此需要选用PLL时钟。 RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW)); RCC->CFGR |= RCC_CFGR_SW_PLL; /* 选择PLL时钟作为系统时钟 */ while ((RCC->CFGR & RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL); /* 等待PLL作为系统时钟完成 */ l 上面我们提到直接使用晶体时钟作为内核时钟源是不太切合实际的,需要使用PLL时钟作为时钟源。那么PLL时钟是怎么来的呢?我们看时钟树图,PLL时钟是从一个叫PLL的模块中得到的。 PLL的时钟又是哪里来的呢?我们接着往前看,可以看到PLL的时钟是由HSE和HIS时钟分频得到的(分频因子为M),HSE和HIS通过一个多路选择器进行选择,多路选择器通过RCC_PLLCFGR[PLLSRC]进行选择的。 说了这么长时间的PLL,PLL到底是啥呢,PLL中文名叫锁相环,英文名叫Phase Locking Loop。其实我们在使用中并不用关心其原理,只需要知道它是将频率倍频、分频至我们需要的频率的一个东西。 接下来我们剖析一下PLL模块,可以看到有VCO、xN、/P、/Q、/R等标志。VCO的全称是电压控制振荡器,xN就是VCO的倍频因子,/P、/Q、/R分别是输出的分频因子。其中/P的输出就是PLLCLK,也就是我们需要的时钟。 在本例程中倍频、分频因子的数值分别是: Ø /M = 4 Ø xN = 360 Ø /P = 4 Ø /Q = 15 HSE时钟,也就是外部晶振时钟,STM32F429 Discovery board板载晶振为8MHz。 经过/M分频,8/4=2MHz 经过xN倍频,2*360 = 720MHz 经过/P分频,720/4 = 180MHz 经过/Q分频,720/15 = 48MHz RCC->  LLCFGR = 0; LLCFGR = 0;RCC->  LLCFGR |= ( PLL_M) | LLCFGR |= ( PLL_M) | ( PLL_N > 1) -1) CR & RCC_CR_PLLRDY) == 0); /* 等待PLL稳定 */ 在这里想提醒注意一下“((PLL_P >> 1) -1) APB1ENR |= RCC_APB1ENR_PWREN; </strong> PWR->CR |= PWR_CR_VOS; while((PWR->CSR & PWR_CSR_VOSRDY) == 0); PWR->CR |= PWR_CR_ODEN; /* 超级驱动使能 */ while((PWR->CSR & PWR_CSR_ODRDY) == 0); /* 等待稳定 */ PWR->CR |= PWR_CR_ODSWEN; /* 超级驱动切换使能 */ while((PWR->CSR & PWR_CSR_ODSWRDY) == 0); /* 等待稳定 */

Flash的访问速度较内核运算速度要低很多,因此需要设置一个等待周期以保证Flash与内核的同步。 FLASH->ACR = FLASH_ACR_PRFTEN | /* 预取指使能 */ FLASH_ACR_ICEN | /* 指令高速缓冲使能 */ FLASH_ACR_DCEN | /* 数据高速缓冲使能 */ FLASH_ACR_LATENCY_5WS; /* 等待5个CPU时钟 */ 设置AHB、APB1、APB2的分频因子,以匹配外设访问速度: RCC->CFGR |= RCC_CFGR_HPRE_DIV1; /* AHB =SYSCLK */ RCC->CFGR |= RCC_CFGR_PPRE2_DIV2; /* APB2=SYSCLK 2分频 */ RCC->CFGR |= RCC_CFGR_PPRE1_DIV4; /* APB1=SYSCLK 4分频 */ 到此,STM32F429的基础时钟配置基本上是完成了,有了以上配置,单片机的基础外设都能够运行,高级外设时钟需要另行配置。 最后曝两张高清照片,请诸君品鉴:

|

STM32F429 Discovery Kit Demo.rar

下载123.66 KB, 下载次数: 368

微信公众号

微信公众号

手机版

手机版

回复:【STM32F429开发日志】(二):STM32F429之时钟配置(另曝高清照片)

我也想知道,找了好久