|

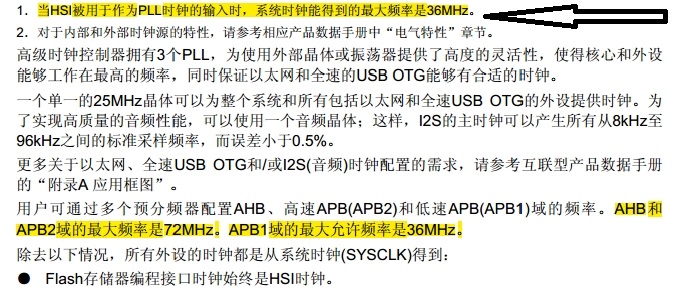

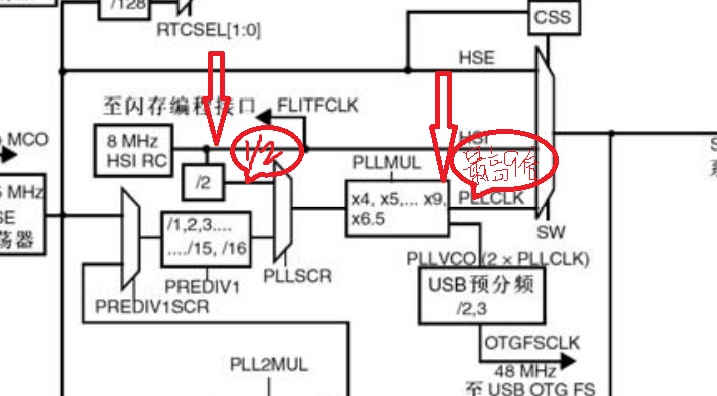

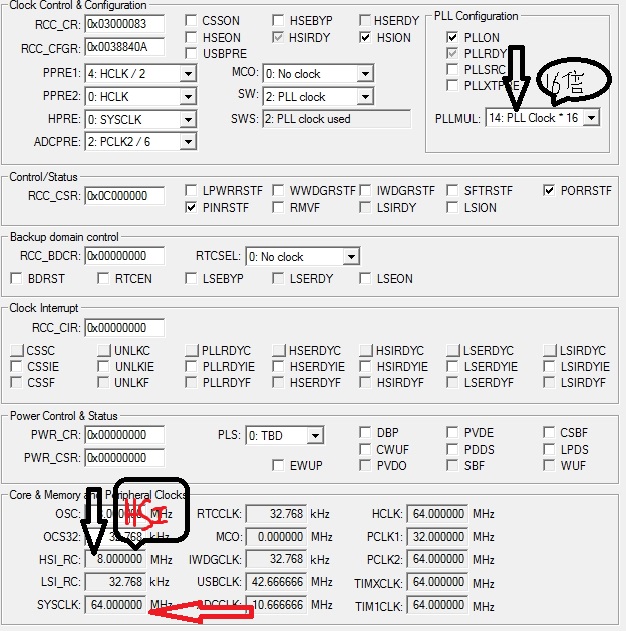

stm32的技术手册上说选用HSI(内部高速时钟)作为PLL输入,生成的系统时钟频率最高位36M,见图1.先对其原因做分析如下:HSI最高频率是8M,经过一个二分之一分频(这是必须的)后输入到PLL之,然后再由PLL经过一个倍频,输出即是系统时钟树,倍频系数最高为9,故:8*9/2=36M,详见图2.但是我比较迷茫的是:技术手册上写的最高倍频为9,但是库函数里的最高倍频为16,若是我们选择了16倍频,那么就可以输出频率为8*16/2=64M的系统时钟,而且我经过如此配置,也确实产生了64M的系统时钟,见图3. 求大神解释一下这是为什么?暂考虑的是:是不是因为内部时钟采取RC震荡电路,精度低,不宜产生太高的超频,不然精度无法保证,所以限制在36M,不知道对不对,能不能这样理解? |

å¾1

å¾2

å¾3

微信公众号

微信公众号

手机版

手机版

系统时钟没配好,还谈什么外设?

16倍,64m

好吧,看来我的文档有问题啊。

这个有问题吗?