|

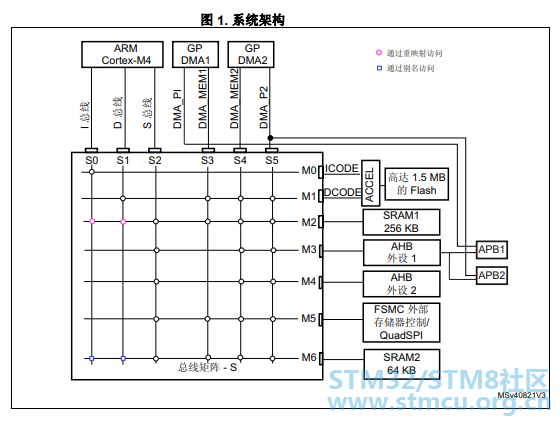

前言 本参考手册面向应用开发人员, 提供有关使用 STM32F413/423 微控制器存储器与外设的完整信息。 STM32F413/423 构成一个微控制器系列,各产品具有不同的存储器大小、封装和外设。 有关订购信息以及器件的机械与电气特性,请参见数据手册。 有关 Arm® 带 FPU 的 Cortex®-M4 内核的信息,请参见Cortex®-M4 技术参考手册。 相关文档 意法半导体网站提供以下文档: - STM32F413/423xG/xH 数据手册 - STM32F3 和 STM32F4 系列带 FPU 的 Cortex®-M4 编程手册 (PM0214),提供关于 Arm带 FPU 的 Cortex®-M4 的信息。 1 文档约定 1.1 一般信息 STM32F413/423 器件具有 Arm®(a) Cortex®-M4 with FPU 内核 1.2 寄存器相关缩写词列表 寄存器说明中使用以下缩写词 2 系统和存储器概述 2.1 系统架构 STM32F413/423 的主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连: 六条主控总线: – 带 FPU 的 Cortex®-M4内核 I 总线、D 总线和 S 总线 – DMA1 存储器总线 – DMA2 存储器总线 – DMA2 外设总线 七条被控总线: – 内部 Flash ICode 总线 – 内部 Flash DCode 总线 – 主内部 SRAM1 (256 KB) – 辅助内部 SRAM2 (64 KB) – AHB1 外设(包括 AHB-APB 总线桥和 APB 外设) – AHB2 外设 – FSMC/QuadSPI 借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期 间,系统也可以实现并发访问和高效运行。此架构如图 1 所示。

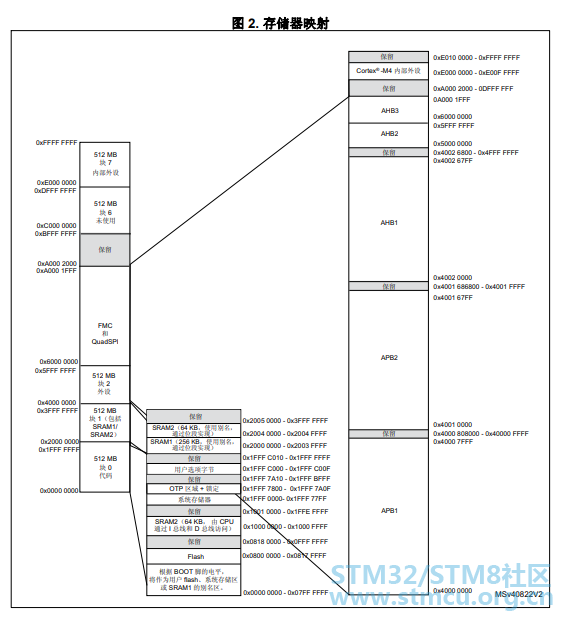

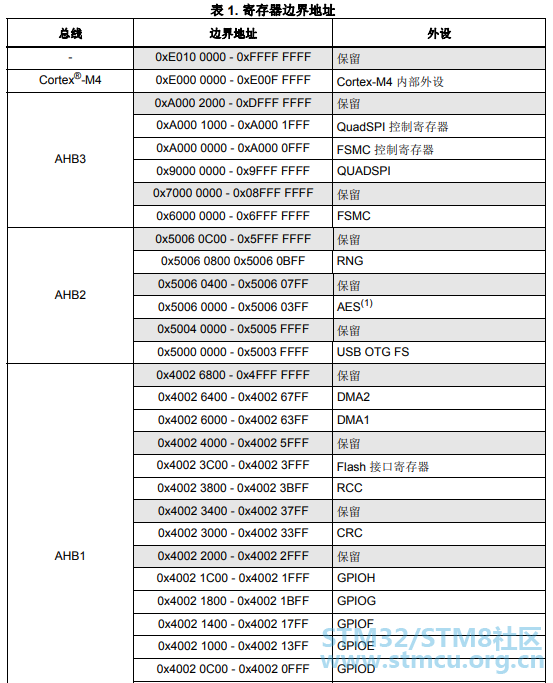

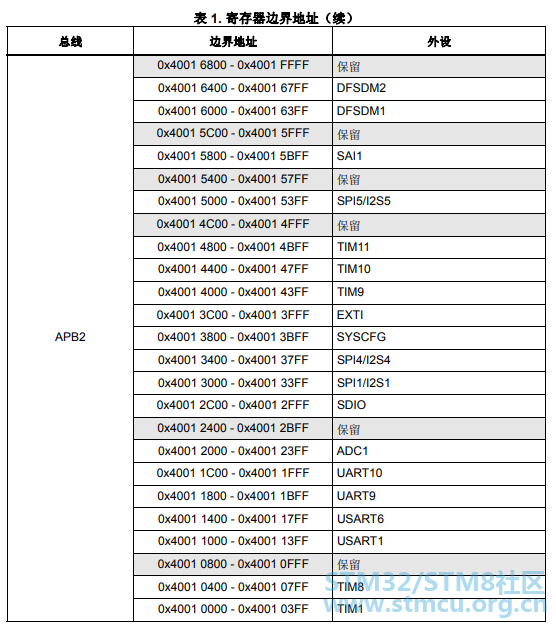

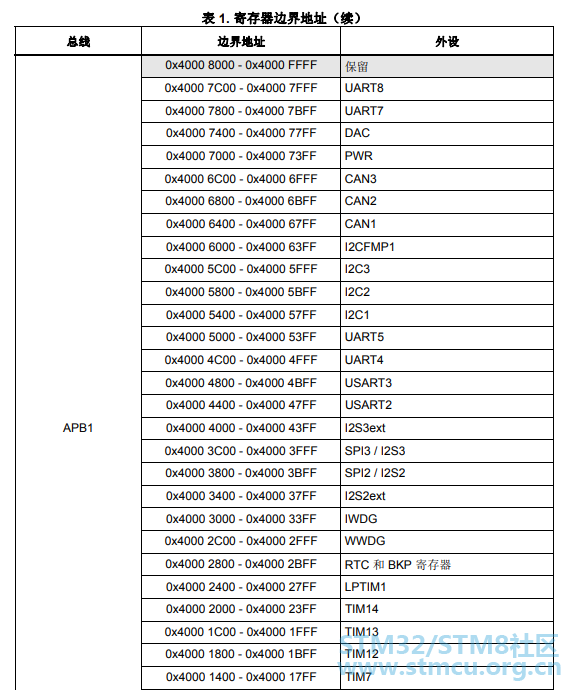

2.1.1 I 总线 此总线用于将带 FPU 的 Cortex®-M4 内核的指令总线连接到总线矩阵。内核通过此总线获取 指令。此总线访问的对象是包含代码的存储器(内部 Flash/SRAM1/SRAM2)。 2.1.2 D 总线 此总线用于将带 FPU 的 Cortex®-M4 的数据总线连接到总线矩阵。内核通过此总线进行立 即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部 Flash/SRAM1/ SRAM2)。 2.1.3 S 总线 此总线用于将带 FPU 的 Cortex®-M4 内核的系统总线连接到总线矩阵。此总线用于访问位 于外设、SRAM1 或 SRAM2 中的数据。也可通过此总线获取指令(效率低于 ICode)。此 总线访问的对象是内部 SRAM1/SRAM2、包括 APB 外设在内的 AHB1 外设、AHB2 外设和 外部存储器(通过外设接口 FSMC 和 QUADSPI)。 2.1.4 DMA 存储器总线 此总线用于将 DMA 存储器总线主接口连接到总线矩阵。DMA 通过此总线来执行存储器数据 的传入和传出。此总线访问的对象是数据存储器:内部 Flash、内部 SRAM1/SRAM2 以及 S4 中包括 APB 外设在内的 AHB1/AHB2 外设。 2.1.5 DMA 外设总线 此总线用于将 DMA 外设主总线接口连接到总线矩阵。DMA 通过此总线访问 AHB 外设或执 行存储器间的数据传输。此总线的访问对象是 AHB 和 APB 外设以及数据存储器:Flash 和 内部 SRAM1/SRAM2。 2.1.6 总线矩阵 总线矩阵用于主控总线之间的访问仲裁管理。仲裁采用循环调度算法。 2.1.7 AHB/APB 总线桥 (APB) 借助两个 AHB/APB 总线桥 APB1 和 APB2,可在 AHB 总线与两个 APB 总线之间实现完全同步的连接,从而灵活选择外设频率。 有关 APB1 和 APB2 最大频率的详细信息,请参见器件数据手册;有关 AHB 和 APB 外设地址映射的信息,请参见表 1。 每次芯片复位后,所有外设时钟都被关闭(SRAM 和 Flash 接口除外)。使用外设前,必须在 RCC_AHBxENR 或 RCC_APBxENR 寄存器中使能其时钟。 注: 对 APB 寄存器执行 16 位或 8 位访问时,该访问将转换为 32 位访问:总线桥将 16 位或 8 位数据复制后提供给 32 位向量。 2.2 存储器组织结构 2.2.1 简介 程序存储器、数据存储器、寄存器和 I/O 端口排列在同一个线性(即地址连续)的 4 GB 地址空间内。 各字节按小端格式在存储器中编码。一个存储字单元中编号最低的字节被视为该字的最低有效字节,而编号最高的字节被视为最高有效字节。 可寻址的存储空间分为 8 个主要块,每个块为 512 MB。 可访问的地址空间取决于主控总线,有关详细信息,请参见第 2 部分:存储器和总线架构。 2.2.2 存储器映射和寄存器边界地址

未分配给片上存储器和外设的所有存储器映射区域均视为“保留区”。有关可用存储器和寄存器区域的详细映射,请参见下表。下表给出了器件中可用外设的边界地址。

2.3 嵌入式 SRAM STM32F413/423 器件具有 320 KB 的系统 SRAM。 嵌入式 SRAM 可按字节、半字(16 位)或全字(32 位)访问。读写操作以 CPU 速度执行,且等待周期为 0。 嵌入式 SRAM 可分为两个块: - 映射到地址 0x2000 0000 的 SRAM1,可供所有 AHB 主控总线访问。 - 映射到地址 0x2004 0000 的 SRAM2,可供所有 AHB 主控总线访问。 如果选择从 SRAM1 自举或选择物理重映射(请参见第 8.2.1 节:SYSCFG 存储器重映射寄存器 (SYSCFG_MEMRMP)),则 CPU 可通过系统总线或 I-Code/D-Code 总线访问嵌入式SRAM1。 为了保证程序在 SRAM1 执行时实现最佳性能,应选择物理重映射(通过自举管脚及软件配置来选择)。 ... 下载文档,阅读完整资料 下载地址1>> 下载地址2>> 更多实战经验>> |

F429I-DISC1体验报告(5) 滚动菜单、语言切换的实现丨国庆开发板测评活动

F429I-DISC1体验报告(4) 温度可视化动态图表的实现丨国庆开发板测评活动

STM32串口自动识别波特率的原理

STM32应用过程中与电源相关的案例分享

【经验分享】STM32F4 CAN2只能发送无法接收问题解决

F429I-DISC1体验报告(3) 画板线条绘制和调色功能的实现丨国庆开发板测评活动

F429I-DISC1体验报告(2) 按钮和弹窗GUI的简单交互设计丨国庆开发板测评活动

STM32固件库分享,超全系列整理

STM32系列芯片之间相互移植注意事项

使用 U 盘更新 STM32F4DISCOVERY 板固件

微信公众号

微信公众号

手机版

手机版