.png) STMCU小助手

发布时间:2022-6-10 19:52

STMCU小助手

发布时间:2022-6-10 19:52

|

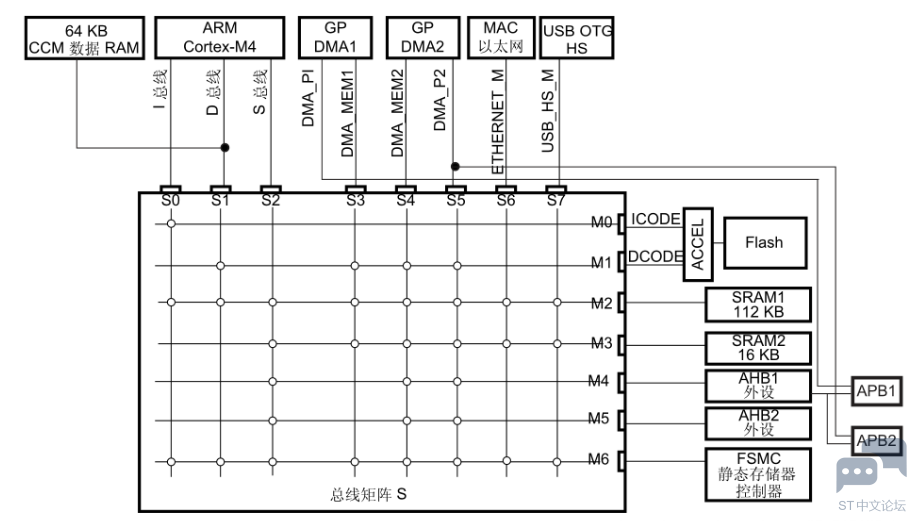

01. 系统架构 主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连: ● 八条主控总线:4 X; C6 M* v* J& W& N6 k, ` — Cortex™-M4F 内核 I 总线、D 总线和 S 总线# c7 j! b' s/ d: j: s — DMA1 存储器总线 — DMA2 存储器总线/ f" d2 }8 i1 N2 }# h6 t/ U — DMA2 外设总线% s1 C) r8 X L — 以太网 DMA 总线; Z' |% P3 Z. z: A — USB OTG HS DMA 总线1 |# f: h4 T1 Q' ]3 _ ● 七条被控总线:7 N& |0 L8 a' Z+ Z, R) a, ? — 内部 Flash ICode 总线 — 内部 Flash DCode 总线 — 主要内部 SRAM1 (112 KB) — 辅助内部 SRAM2 (16 KB) — 辅助内部 SRAM3 (64 KB)(仅适用于 STM32F42xxx 和 STM32F43xxx 器件) — AHB1 外设(包括 AHB-APB 总线桥和 APB 外设) — AHB2 外设 — FSMC6 i$ Y& J6 z0 N% f# `6 k& f- { 借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。% l" C s# ]# F/ D 5 e7 C H) Z5 v: D! @8 ` 注意:$ m" [$ Q5 F, i. E* c5 r& L4 `) C 64 KB CCM (内核耦合存储器)数据 RAM 不属于总线矩阵(请参见图 1 : STM32F405xx/07xx和 STM32F415xx/17xx 器件的系统架构和图 2 : STM32F42xxx 和 STM32F43xxx 器件的系统架构)。只能通过 CPU 对其进行访问。- F* }! V% x6 }& u5 s) O a6 b+ t! D* x; t9 A( s. I" L" [ 02. 总线架构图

: M( T$ W$ N3 B. A' y 03. 总线详解 3.1 S0 :I 总线此总线用于将 Cortex™-M4F 内核的指令总线连接到总线矩阵。内核通过此总线获取指令。此总线访问的对象是包含代码的存储器(内部 Flash/SRAM 或通过 FSMC 的外部存储器)。0 Z+ }- p3 U% J6 C/ m6 S / O4 c3 } L8 H' p- X6 H 3.2 S1 :D 总线1 C6 }+ O8 N; \0 v/ c8 c 此总线用于将 Cortex™-M4F 数据总线和 64 KB CCM 数据 RAM 连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部Flash 或通过 FSMC 的外部存储器)。, ~* `% q; U. a ! U* R0 [& C7 H' Z 3.3 S2 :S 总线* b5 n: u4 d; z5 Y, b 此总线用于将 Cortex™-M4F 内核的系统总线连接到总线矩阵。此总线用于访问位于外设或 SRAM 中的数据。也可通过此总线获取指令(效率低于 ICode)。此总线访问的对象是112 KB、64 KB 和 16 KB 的内部 SRAM、包括 APB 外设在内的 AHB1 外设、AHB2 外设以及通过 FSMC 的外部存储器。 ; W* d$ U" N3 z, ]$ u) U 3.4 S3 、S4 :DMA 存储器总线 此总线用于将 DMA 存储器总线主接口连接到总线矩阵。DMA 通过此总线来执行存储器数据的传入和传出。此总线访问的对象是数据存储器:内部 SRAM(112 KB、64 KB、16 KB)以及通过 FSMC 的外部存储器。 3.5 S5 :DMA 外设总线 此总线用于将 DMA 外设主总线接口连接到总线矩阵。DMA 通过此总线访问 AHB 外设或执行存储器间的数据传输。此总线访问的对象是 AHB 和 APB 外设以及数据存储器:内部SRAM 以及通过 FSMC 的外部存储器。& _$ h$ Y5 C/ H ; l; ^9 e$ \6 l9 _6 @ l+ m( J& N* l% y* w2 z* G8 H 3.6 S6 :以太网 DMA 总线0 d, l0 ~. o4 r, m4 ^ 此总线用于将以太网 DMA 主接口连接到总线矩阵。以太网 DMA 通过此总线向存储器存取数据。此总线访问的对象是数据存储器:内部 SRAM(112 KB、64 KB 和 16 KB)以及通过FSMC 的外部存储器。1 Q8 }8 z% I: V0 ~) ^+ R1 k + \" E* f; N) \" w 3.7 S7 :USB OTG HS DMA 总线 此总线用于将 USB OTG HS DMA 主接口连接到总线矩阵。USB OTG DMA 通过此总线向存储器加载/存储数据。此总线访问的对象是数据存储器:内部 SRAM(112 KB、64 KB 和 16 KB)以及通过 FSMC 的外部存储器。 / u }/ w- j% [; r 3.8 AHB/APB 总线桥 (APB) 借助两个 AHB/APB 总线桥 APB1 和 APB2,可在 AHB 总线与两个 APB 总线之间实现完全同步的连接,从而灵活选择外设频率。 每次芯片复位后,所有外设时钟都被关闭(SRAM 和 Flash 接口除外)。使用外设前,必须在 RCC_AHBxENR 或 RCC_APBxENR 寄存器中使能其时钟。* n; V0 P9 [* q$ |1 n2 Q 总线矩阵用于主控总线之间的访问仲裁管理。仲裁采用循环调度算法。* S4 b& l0 P( ^! r8 k & W; ^' z9 O$ z5 B |

微信公众号

微信公众号

手机版

手机版