.png) STMCU小助手

发布时间:2022-7-11 22:26

STMCU小助手

发布时间:2022-7-11 22:26

|

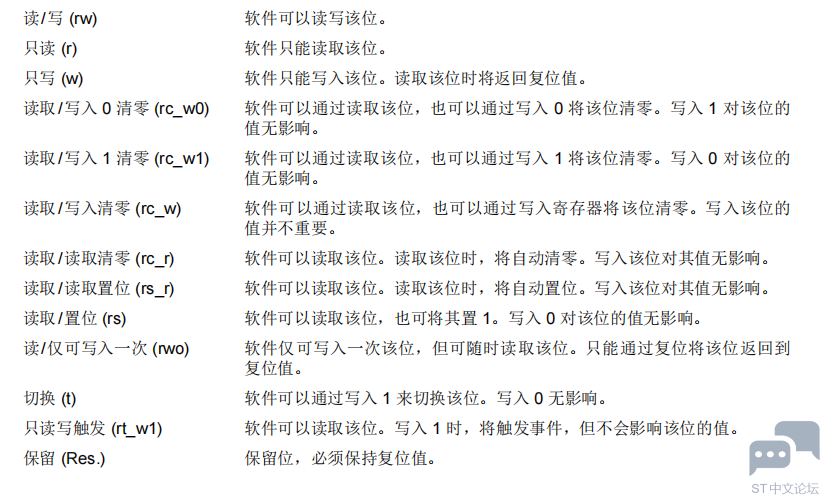

前言 本参考手册面向应用开发人员, 提供有关使用 STM32F413/423 微控制器存储器与外设的完 整信息。 STM32F413/423 构成一个微控制器系列,各产品具有不同的存储器大小、封装和外设。 有关订购信息以及器件的机械与电气特性,请参见数据手册。 有关 Arm® 带 FPU 的 Cortex®-M4 内核的信息,请参见Cortex®-M4 技术参考手册。 1 文档约定 1.1 一般信息 STM32F413/423 器件具有 Arm®(a) Cortex®-M4 with FPU 内核 1.2 寄存器相关缩写词列表 寄存器说明中使用以下缩写词(b):

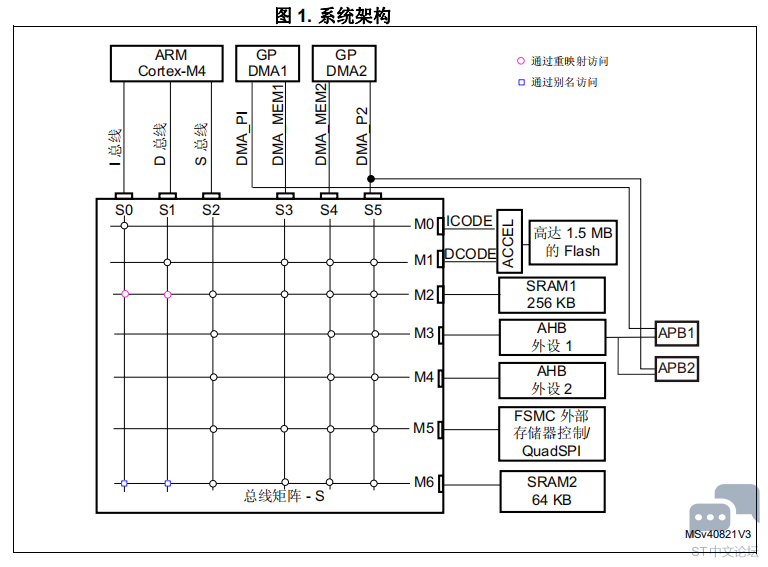

1.3 词汇表 本节简要介绍本文档中所用首字母缩略词和缩写词的定义: 字:32 位数据。 半字:16 位数据。 字节:8 位数据。 IAP(在应用中编程):IAP 是指可以在用户程序运行期间对微控制器的 Flash 进行重新编程。 ICP(在线编程):ICP 是指可以在器件安装于用户应用电路板上时使用 JTAG 协议、SWD 协议或自举程序对微控制器的 Flash 进行编程。 选项字节:存储于 Flash 中的产品配置位。 AHB:高级高性能总线。 1.4 外设可用性 有关各型号产品的外设可用性及数量的信息,请参见特殊器件数据手册。 2 系统和存储器概述 2.1 系统架构 STM32F413/423 的主系统由 32 位多层 AHB 总线矩阵构成,可实现以下部分的互连: 六条主控总线: – 带 FPU 的 Cortex®-M4内核 I 总线、D 总线和 S 总线 – DMA1 存储器总线 – DMA2 存储器总线 – DMA2 外设总线 七条被控总线: – 内部 Flash ICode 总线 – 内部 Flash DCode 总线 – 主内部 SRAM1 (256 KB) – 辅助内部 SRAM2 (64 KB) – AHB1 外设(包括 AHB-APB 总线桥和 APB 外设) – AHB2 外设 – FSMC/QuadSPI 借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。此架构如图 1 所示。

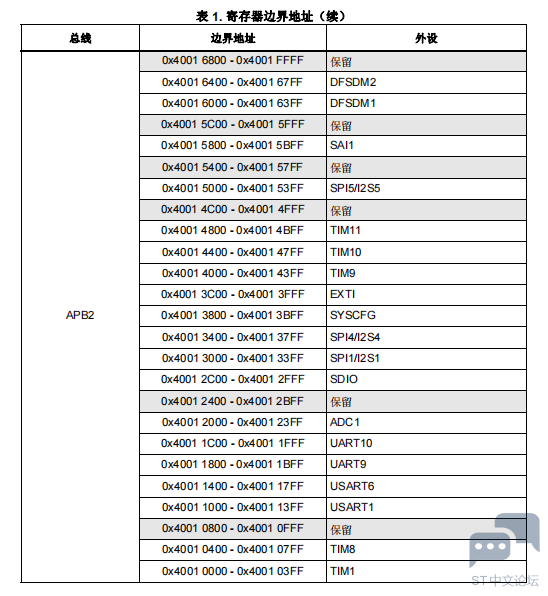

2.1.1 I 总线 此总线用于将带 FPU 的 Cortex®-M4 内核的指令总线连接到总线矩阵。内核通过此总线获取指令。此总线访问的对象是包含代码的存储器(内部 Flash/SRAM1/SRAM2)。 2.1.2 D 总线 此总线用于将带 FPU 的 Cortex®-M4 的数据总线连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部 Flash/SRAM1/SRAM2)。 2.1.3 S 总线 此总线用于将带 FPU 的 Cortex®-M4 内核的系统总线连接到总线矩阵。此总线用于访问位于外设、SRAM1 或 SRAM2 中的数据。也可通过此总线获取指令(效率低于 ICode)。此总线访问的对象是内部 SRAM1/SRAM2、包括 APB 外设在内的 AHB1 外设、AHB2 外设和外部存储器(通过外设接口 FSMC 和 QUADSPI)。 2.1.4 DMA 存储器总线 此总线用于将 DMA 存储器总线主接口连接到总线矩阵。DMA 通过此总线来执行存储器数据的传入和传出。此总线访问的对象是数据存储器:内部 Flash、内部 SRAM1/SRAM2 以及S4 中包括 APB 外设在内的 AHB1/AHB2 外设。 2.1.5 DMA 外设总线 此总线用于将 DMA 外设主总线接口连接到总线矩阵。DMA 通过此总线访问 AHB 外设或执行存储器间的数据传输。此总线的访问对象是 AHB 和 APB 外设以及数据存储器:Flash 和内部 SRAM1/SRAM2。 2.1.6 总线矩阵 总线矩阵用于主控总线之间的访问仲裁管理。仲裁采用循环调度算法。 2.1.7 AHB/APB 总线桥 (APB) 借助两个 AHB/APB 总线桥 APB1 和 APB2,可在 AHB 总线与两个 APB 总线之间实现完全同步的连接,从而灵活选择外设频率。 有关 APB1 和 APB2 最大频率的详细信息,请参见器件数据手册;有关 AHB 和 APB 外设地址映射的信息,请参见表 1。 每次芯片复位后,所有外设时钟都被关闭(SRAM 和 Flash 接口除外)。使用外设前,必须在 RCC_AHBxENR 或 RCC_APBxENR 寄存器中使能其时钟。 注: 对 APB 寄存器执行 16 位或 8 位访问时,该访问将转换为 32 位访问:总线桥将 16 位或 8 位 数据复制后提供给 32 位向量。 2.2 存储器组织结构 2.2.1 简介 程序存储器、数据存储器、寄存器和 I/O 端口排列在同一个线性(即地址连续)的 4 GB 地址空间内。 各字节按小端格式在存储器中编码。一个存储字单元中编号最低的字节被视为该字的最低有效字节,而编号最高的字节被视为最高有效字节。 可寻址的存储空间分为 8 个主要块,每个块为 512 MB。 可访问的地址空间取决于主控总线,有关详细信息,请参见第 2 部分:存储器和总线架构。 2.2.2 存储器映射和寄存器边界地址

未分配给片上存储器和外设的所有存储器映射区域均视为“保留区”。有关可用存储器和寄存器区域的详细映射,请参见下表。 下表给出了器件中可用外设的边界地址。 ![[ZB5B]L@53HY07Z(TWEXEYA.png [ZB5B]L@53HY07Z(TWEXEYA.png](data/attachment/forum/202207/11/222741ne9geq8f8g9u1484.png)

![66XI26XCK$%0TQND1[]WO$E.png 66XI26XCK$%0TQND1[]WO$E.png](data/attachment/forum/202207/11/222740d55hwrr8xmugruur.png)

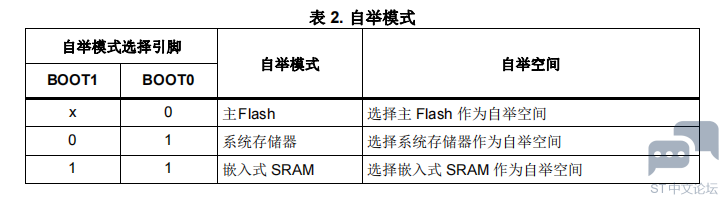

2.3 嵌入式 SRAM STM32F413/423 器件具有 320 KB 的系统 SRAM。 嵌入式 SRAM 可按字节、半字(16 位)或全字(32 位)访问。读写操作以 CPU 速度执 行,且等待周期为 0。 嵌入式 SRAM 可分为两个块: 映射到地址 0x2000 0000 的 SRAM1,可供所有 AHB 主控总线访问。 映射到地址 0x2004 0000 的 SRAM2,可供所有 AHB 主控总线访问。 如果选择从 SRAM1 自举或选择物理重映射(请参见第 8.2.1 节:SYSCFG 存储器重映射寄 存器 (SYSCFG_MEMRMP)),则 CPU 可通过系统总线或 I-Code/D-Code 总线访问嵌入式SRAM1。 为了保证程序在 SRAM1 执行时实现最佳性能,应选择物理重映射(通过自举管脚及软件配置来选择)。 当 SRAM2 映射到地址 0x1000 0000 - 0x1000 FFFF 范围内时,CPU 可通过系统总线或I-Code/D-Code 总线访问嵌入式 SRAM2。为了保证程序在 SRAM2 执行时实现最佳性能, 应选择映射到地址 0x1000 0000。 要想利用内置 SRAM 获得最佳性能,应将代码放在 SRAM1/SRAM2 中,通过 I-CODE 总线执行代码,并将数据保存在 SRAM1/SRAM2 中 2.4 Flash 概述 Flash 接口可管理 CPU 通过 AHB I-Code 和 D-Code 对 Flash 进行的访问。该接口可针对Flash 执行擦除和编程操作,并实施读写保护机制。Flash 接口通过指令领取和缓存机制加速代码执行。 flash 存储器结构如下: 主存储器块分为多个扇区。 系统存储区,器件在系统存储区自举模式下从该存储区启动 512 OTP(一次性可编程)字节,用于存储用户数据。 选项字节,用于配置读写保护、BOR 级别、软件/硬件看门狗以及器件处于待机或停止模式下的复位。 更多详细信息,请参见第 3 节:嵌入式 Flash 接口。 2.5 位段 带 FPU 的 Cortex®-M4 存储器映射包括两个位段区域。这些区域将存储器别名区域中的每个 字映射到存储器位段区域中的相应位。在别名区域写入字时,相当于对位段区域的目标位执行读-修改-写操作。 在 STM32F4x3xx 器件中,外设寄存器和 SRAM1 均映射到一个位段区域,这样可实现单个位段的读写操作。这些操作仅适用于带 FPU 的 Cortex®-M4 内核访问,对于其他总线主接口(如 DMA)无效。 可通过一个映射公式说明别名区域中的每个字与位段区域中各个位之间的对应关系。映射公式为: bit_word_addr = bit_band_base + (byte_offset x 32) + (bit_number × 4) 其中: – bit_word_addr 代表别名区域中将映射到目标位的字的地址 – bit_band_base 代表别名区域的起始地址 – byte_offset 代表目标位所在位段区域中的字节编号 – bit_number 代表目标位的位位置 (0-7) 示例 下例说明如何将 SRAM1 地址 0x20000300 处字节的位 2 映射到别名区域: 0x22006008 = 0x22000000 + (0x300*32) + (2*4) 对地址 0x22006008 执行写操作相当于在 SRAM1 地址 0x20000300 处字节的位 2 执行读-修改-写操作。 对地址 0x22006008 执行读操作将返回 SRAM1 地址 0x20000300 处字节的位 2 的值(0x01表示位置 1,0x00 表示位复位)。 有关位段的详细信息,请参见带 FPU 的 Cortex®-M4 编程手册(请参见第 1 页的相关文档 )。 2.6 自举配置 存储器采用固定的存储器映射,代码区域起始地址为 0x0000 0000(通过 ICode/DCode 总 线访问),而数据区域 (SRAM) 起始地址为 0x2000 0000(通过系统总线访问)。带 FPU的 Cortex®-M4 CPU 始终通过 ICode 总线获取复位向量,这意味着只有代码区域(通常为Flash)可以提供自举空间。STM32F4xx 微控制器实施一种特殊机制,可以从其他存储器(如内部 SRAM)进行自举。 在 STM32F4x3xx 中,可通过 BOOT[1:0] 引脚选择三种不同的自举模式,如表 2 所示。

复位后,在 SYSCLK 的第四个上升沿锁存 BOOT 引脚的值。复位后,用户可以通过设置BOOT1 和 BOOT0 引脚来选择需要的自举模式。 BOOT0 为专用引脚,而 BOOT1 则与 GPIO 引脚共用。一旦完成对 BOOT1 的采样,相应GPIO 引脚即进入空闲状态,可用于其他用途。 器件退出待机模式时,还会对 BOOT 引脚重新采样。因此,当器件处于待机模式时,这些引脚必须保持所需的自举模式配置。这样的启动延迟结束后,CPU 将从地址 0x0000 0000 获取栈顶值,然后从始于 0x0000 0004 的自举存储器开始执行代码。 注: 如果器件从 SRAM 自举,在应用程序初始化代码中,需要使用 NVIC 异常及中断向量表和偏 移寄存器来重新分配 SRAM 中的向量表。 内部自举程序 嵌入式自举程序模式用于通过表 32 中所列的任一接口来重新编程 Flash。接口可用性取决于封装。 ![RW9Z@V7T9VDGLXOZT5]B9DS.png RW9Z@V7T9VDGLXOZT5]B9DS.png](data/attachment/forum/202207/11/222740i86djwjm8m0j180m.png)

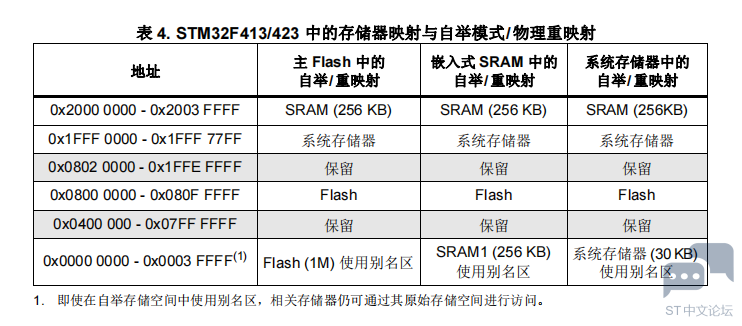

USART 外设以内部 16 MHz 振荡器 (HSI) 频率运行,而 CAN 和 USB OTG FS 则需要相当 于 1 MHz 数倍(4 MHz 到 26 MHz 之间)的外部时钟 (HSE) 频率。 内部自举程序代码位于系统存储器中, 在芯片生产期间由 ST 编程。有关详细信息,请参见应用笔记 AN2606。 STM32F413/423 中的物理重映射 选择自举引脚后,应用程序软件可以将某些存储器设定为从代码空间进行访问(这样,可通过ICode 总线而非系统总线执行代码)。这样的修改通过在 SYSCFG 控制器中编程第 8.2.1 节: SYSCFG 存储器重映射寄存器 (SYSCFG_MEMRMP) 来实现。 因此可重映射以下存储器: 主 Flash 系统存储器 嵌入式 SRAM

完整版请查看:附件 |

DM00305666_ZHV8.pdf

下载15.46 MB, 下载次数: 2

微信公众号

微信公众号

手机版

手机版