.png) STMCU小助手

发布时间:2022-7-13 15:44

STMCU小助手

发布时间:2022-7-13 15:44

|

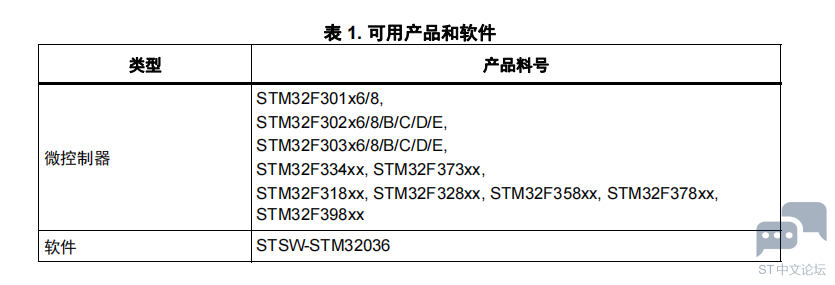

前言 本应用笔记描述了如何优化基于 STM32F3xx 微控制器的应用的功耗。减少功耗同时执行复杂的实时应用对于当前嵌入式应用提出了重大挑战。 本应用笔记主要分为两部分: • 第一部分给出了低功耗设计集成特性和降低功耗技术的概述。 • 第二部分描述了一个用例 (智能电机控制应用),此用例针对嵌入式系统市场有竞争力的应用,重点突出了 STM32F3xx 微控制器的功率效率。 本应用笔记提供了 STSW-STM32036 软件包,此软件包含有 STM32F3xx 微控制器低功耗应用的示例。本应用笔记基于 USART、 DMA、定时器、比较器、 RTC 外设,应用STM32F3xx 微控制器低功耗模式和特性。

1 STM32F3xx 微控制器低功耗概览 STM32F3xx 微控制器基于运行速率达 72 MHz 的 ARM® Cortex®-M4 内核,集成了多种高级 模拟外设。它们集成了高效的电源结构和多种功耗模式,从而降低了应用级功耗并简化了应用设计。 1.1 电源 STM32F3xxxx 器件具有优化的电源结构,集实时功能、数字信号处理和低电压操作、高度集成的模拟外设于一身。 根据 STM32F3xx 微控制器中内部调压器的可用性,存在两种不同的电源结构: 1.1.1 具有内部调压器的 STM32F3xxxx 器件电源 嵌入的调压器用来为 1.8 V 数字电源区域供电,该区域包括内核、存储器和数字外设,如图 1所示。 ![BSL5U)RT@1OK]]_T(WVY)N3.png BSL5U)RT@1OK]]_T(WVY)N3.png](data/attachment/forum/202207/13/154604w8mt68htuldddif8.png)

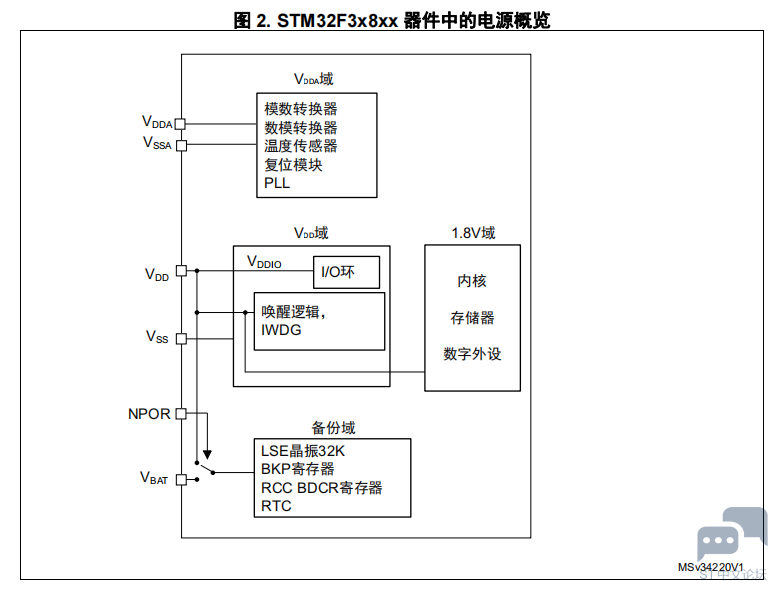

1.1.2 STM32F3x8xx 器件电源 这些器件不具有调压器。 VDD 直接为调压器输出供电,如图 2 中所述。

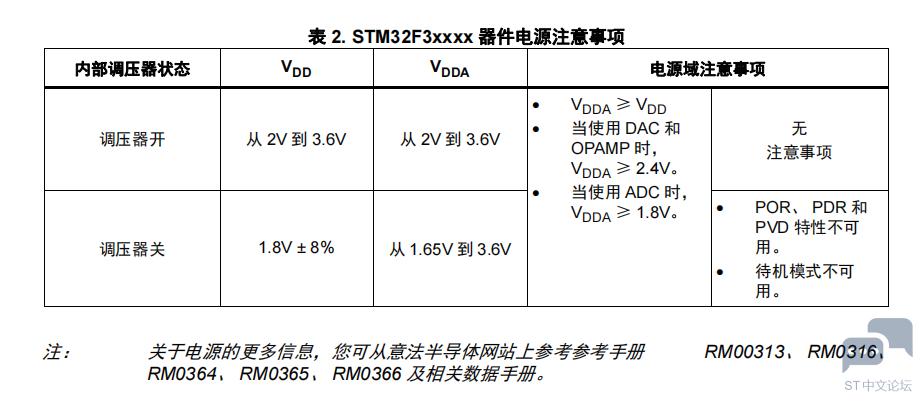

STM32F3x8 微控制器需要 1.8 V +/- 8% 工作供电电压 (VDD)和 1.65 V - 3.6 V 模拟供电电 压 (VDDA)。不支持待机模式。 1.1.3 电源总结 两种电源结构中,当主电源 VDD 断开时,可通过 VBAT 电压为实时时钟 (RTC)和备份寄存器供电。 表 2 总结了两种结构中的电源供电范围,并给出了需考虑的供电条件。

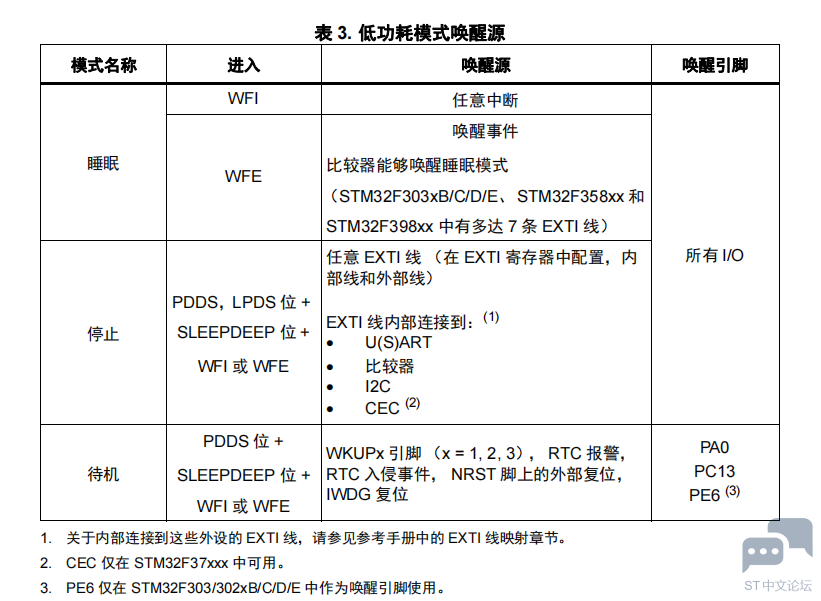

1.2 功耗模式特性 默认情况下,上电或系统复位后,STM32F3xx 微控制器处于运行模式。这是完全激活模式,即便执行微小任务时,也会消耗大量功率。 集成了高度优化的低功耗模式,使 CPU 在不需要保持运行时能够节省功率,因此在应用设计中实现了低功耗、短启动时间与可用唤醒源之间的最佳折中。 本部分描述 STM32F3xxxx 器件支持的不同低功耗模式及相关特性。 STM32F3xxxx 器件具有 4 种主要的低功耗模式: • 睡眠模式: – 只有 CPU 时钟停止。 – Cortex®-M4 时钟停止,而外设保持运行。电流消耗随着时钟频率而增加。如在运行模式下,用户需要知道系统时钟配置规则。 • 停止模式 – 在保持所有 SRAM 和寄存器内容的情况下的最低功耗。 – 禁用 PLL, HSI, HSE。 – 1.8 V 域的所有时钟均断开。 – 调压器工作于正常模式或低功耗模式。 停止模式在保持 SRAM 和寄存器内容的同时,实现最低功耗。此时, 1.8 V 域中的所有时钟都会停止, PLL、 HSI 和 HSE 被禁止。还可以将调压器置于正常模式或低功耗模式 (当内部调压器断开时不可用)。 • 待机模式 – 最低功耗。 – 1.8V 域断电 (调压器禁用)。 – 除备份域之外, SRAM 和寄存器的内容都将丢失。 Cortex®-M4 内核停止,且时钟关闭。内部调压器禁用,1.8 V 域断电。除备份域(RTC 寄存 器、RTC 备份寄存器和备份 SRAM)和待机电路中的寄存器外,SRAM 和寄存器内容都将丢失。 注: 内部调压器为 OFF 的器件,其待机模式不可用。 • Vbat 模式: – 主数字供电 (VDD)关断。 – 电路通过 VBAT 脚供电,该脚应当连接一个外部电源电压 (电池或其他任意源)。 该模式仅用于主数字供电 (VDD)关断且 VBAT 脚连接到外部供电电压时。 VBAT 脚为备份域(RTC 寄存器、 RTC 备份寄存器和备份 SRAM)供电。 注: 关于STM32F3xxxx器件这些低功耗模式特性和低功耗技术的更多描述,您可从意法半导体网站上参考 RM00313、 RM0316、 RM0364、 RM0365、 RM0366 参考手册及相关数据手册。 1.3 低功耗模式唤醒 STM32F3xxxx 器件集成了很多唤醒源,为低功耗应用开发提供了灵活的电源管理,并简化了应用设计。大量的 I/O 引脚支持使用这些不同的唤醒源。 表 3 描述了 STM32F3xxxx 器件中可用的不同唤醒源和引脚。DocID026505 Rev 1 [English Rev 1] 9/25

低功耗模式唤醒时间对功率优化和应用灵活性的影响很大。必须在低功耗模式的功耗和相应唤醒时间之间实现平衡。 表 4 给出了 STM32F3xx 微控制器中低功耗模式唤醒时间的示例 ![]XJ69@__IV0}576A~Z02K[W.png ]XJ69@__IV0}576A~Z02K[W.png](data/attachment/forum/202207/13/154603ejnnhzh7x6gy7hxb.png)

1.4 STM32F3xx 微控制器节能技术 1.4.1 通用技术 本章节简要描述了主要的节能特性,它们有助于降低电流消耗,并在处理性能和功率效率之间实现最佳平衡。 • 系统时钟配置 可通过多个预分频器配置 AHB 频率、高速 APB (APB2) 和低速 APB (APB1)。在运行模式下,可通过将寄存器预分频器编程为最大值来降低系统时钟的速率,以便仅为外设提供其所需时钟,并避免超频引起功耗过大。 当 APBx 和 AHBx 外设不用时,通过对其时钟进行门控,可进一步降低功耗。 • I/O 配置为避免有额外的 I/O 电流,所有闲置引脚都应当配置为模拟输入,这种模式下施密特触发器输入被禁用,可使每个 I/O 引脚均为零消耗。 对于输出,建议将 I/O 速率频率配置为尽可能最低的速率。如不使用上拉和下拉,则用户须避免上拉和下拉激活,并建议不作上拉 / 下拉配置。如不用时钟输出的 MCO 脚,则用户还须将其禁用。 • 使用直接存储器访问 (DMA) 可通过 DMA 访问 STM32F3xxxx 器件外设。此特性不仅有助于提高性能,还能降低功耗。为了避免仅有一个缓冲寄存器的外设上发生溢出, CPU 必须保持运行。但是,利用 DMA, CPU 可进入睡眠模式,直至 DMA 传输完成。 这使得器件在应用寿命内的平均电流消耗更少。 • 采用低功耗模式 在应用处理中切换功耗模式,使器件尽可能处于低功耗模式,可降低总平均功耗。 最佳功率管理方案包括在不同功耗模式之间进行切换,并同时从功耗、唤醒源 / 时间和外设角度考虑应用的要求。 • 外设时钟门控 同时激活的外设块越多,功耗越高。通过对不用的外设时钟进行门控,能够实现明显的节能。 • 利用外设的低功耗特性 STM32F3xxxx 器件的外设具有独特的功耗特性,允许设计和开发低功耗应用,同时保持高度的灵活性和与外界简单的交互性。例如,利用 USART、比较器、 I2C 和 CEC,器件能够从低功耗模式唤醒。 1.4.2 低功耗特性 一些 STM32F3xxxx 外设具有低功耗特性,能够很容易地使用低功耗模式,同时保持高处理能力。这些特性的可用性对于不同 STM32F3xx 微控制器是不同的。 • COMP STM32F3xxxxb 比较器独立于 PCLK2 时钟而工作。由于存在该时钟,比较器甚至能够在停止模式下运行。每个比较器具有其各自的 EXTI 线,能够产生中断或事件,可将器件从睡眠和停止模式中唤醒。 睡眠模式下,输出可连接到 I/O 或多个定时器输入,以触发控制和监测模拟信号。 对于给定的应用,可调节比较器功耗与速率以获得最佳平衡 (此特性仅在STM32F303/302xB/C、 STM32F358xx、 STM32F373xx 和 STM32F378xx 器件中可用。)。 • U(S)ART 睡眠模式下,所有 U(S)ART 均可使用 DMA 控制器。 USART 支持双时钟域 (支持所述功能和停止模式唤醒)。 USART 可通过地址匹配、起始位,或在时钟源为 HSI 或 LSE时通过 RXNE 从停止模式唤醒。 此特性方便了应用设计和开发,同时能够保持功率效率。 注意,用户可将 IrDA SIR ENDEC 置于低功耗模式来节省更多功率。 • I2C DMA 可用来降低 CPU 负荷,并因而降低功耗。 I2C 的时钟由独立时钟源提供,这使得I2C 能够独立于 PCLK 频率工作。当 I2C 时钟源为 HSI 时, I2C 可在地址匹配时从停止模式唤醒。 • CEC 消费电子控制 (Consumer Electronics Control)协议可在低速下工作,具有极低的处理和存储开销。它有一个独立于 CPU 时钟的时钟域,可在收到数据时从停止模式唤醒MCU。 HDMI_CEC 控制器仅嵌入 STM32F37xxx 器件中。 • ADC STM32F3xxxx 器件 (除了 STM32F373/378xx 器件外)嵌入了一个低功耗 ADC,其功耗与速率成比例。速率最低时,功耗最低。 此 ADC 具有两个时钟源,分别来自 AHB 和 PLLCLK 时钟。因此,可达到最大速率5MSPS,与低速 AHB 总线频率一致。这种情况下,为避免 ADC 过载,可用 ADC 自动延时特性。 完整版请查看:附件 |

DM00121474_ZHV1.pdf

下载796.35 KB, 下载次数: 1

微信公众号

微信公众号

手机版

手机版