|

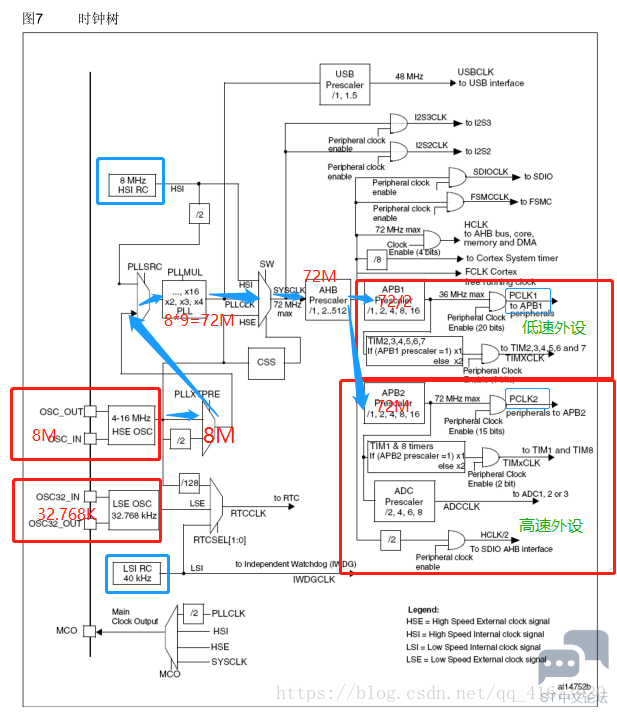

刚入STM32 用了也有一段时间了,先做了中断,CAN,SPI。都是跟着网上的例子直接粘贴外设的初始化代码,看的大概能懂,但是时钟一直迷迷糊糊,不清不楚。 STM32为了实现低功耗,而设计的功能完善构成复杂的时钟系统,称之时钟树。使外设功能的时钟可自配置。因为STM32外设众多,而不同的项目用到的外设参差不齐,所以可控的时钟可以实现降低产品功耗。 所有的外设在使用之前都必须设置时钟信号,才可以正常工作。以STM32F103C8T6时钟树为例,如下图所示: 图7和图8道理一样的,大家觉得那个容易理解就看那个图

图8

STM32的四个时钟源 外部时钟 <1>高速外部时钟(HSE):外部时钟源,晶振频率可取范围为4~16MHz,我们一般采用8MHz的晶振。 <2>低速外部时钟(LSE):外部时钟源,主要提供给实时时钟模块,所以一般采用32.768KHz。 内部时钟 <3>高速内部时钟(HSI):由内部RC振荡器产生,频率为8MHz,但不稳定。 <4>低速内部时钟(LSI):由内部RC振荡器产生,也主要提供给实时时钟模块,频率大约为40KHz。 以最常用的高速外部时钟(HSE)为例 <1>左边红色框框1 两个外部引脚接8M晶振的两端。 <2>8M时钟遇到第一个分频器PLLXTPRE,也就是HSE后面的第一个节点,我们不分频。 <3>时钟来到PLL Source Mux,可选输入的时钟信号有外部高速时钟(HSE)和内部高速时钟(HSI),选择HSE。 <4>接着信号走到锁相环PLL,具有倍频作用,我们选择倍频因子(PLL Mul),可取值2,3,...14,15,16,我们选择9倍频。现在时钟信号为8*9=72M。 <5>来到系统时钟源输入选择,可选时钟有HSE(8M)、HSI(8M)和经过倍频的PLL CLK(72M),选择PLL CLK作为系统时钟,此时系统时钟为72M。 <6>系统时钟(SYSCLK)来到AHB预分频器,可选分频系数:1,2,4,8,16,32,64,128,256。选择不分频,直接来到挂载低速外设的(APB1)PCLK1和挂载高速外设的(APB2)PCLK2。 <7>PCLK1低速外设时钟的最大频率为36M,所以最低进行2分频。PCLK2高速外设时钟的最大频率是72M,可选择不分频。 选择使用HSE也是因为外部时钟更稳定精准,经过倍频给STYCLK提供最大的时钟频率,发挥CPU的最优性能。了解了时钟树,在使用各个外设的时候就明白时钟信号的来源了。记得初始化外设一定要使能相应的时钟。 ———————————————— 版权声明:我是唐 |

OpenBLT移植到STM32F103战舰开发板上适用于所有STM32F103系列的Bootloader

TFT LCD 与 FSMC 的硬件连接大容量 STM32F10xxx FSMC 接口

单片机:初学者该了解的STM32F103基础知识

2025软件工具兔哥知道

STM32之继电器模块

STM32固件库分享,超全系列整理

【MCU实战经验】基于STM32F103的二轮平衡车(6轴上位机 源代...

10张图带你完全掌握STM32 GPIO,从入门到精通,收藏就够了!

如果你解决了这些问题,就可以直接学STM32

STM32的分类和选型

微信公众号

微信公众号

手机版

手机版