.png) STMCU小助手

发布时间:2022-12-2 13:43

STMCU小助手

发布时间:2022-12-2 13:43

|

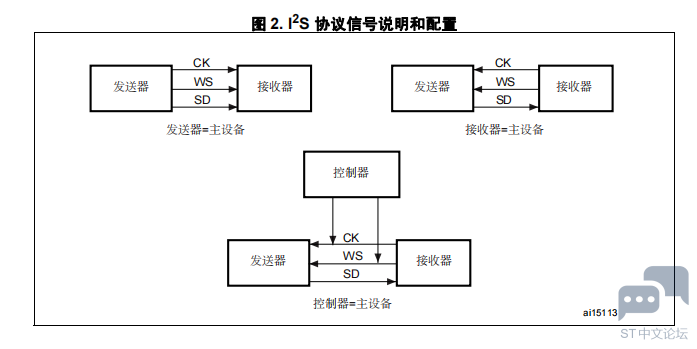

前言 本应用笔记说明了如何利用外部编解码器(参考 STSW-STM32135),使用 STM32L1xx I2S 接口播放音频文件。 I2S 协议广泛用于从微控制器 /DSP 到音频编解码器传输音频数据,以播放(储存于存储器中的)音乐,或者 (从麦克风)捕获模拟声音。 STM32L1xx 可使用 SPI 外设进行 I2S 音频通信,并为此通信模式实现了特定的功能。高级用户可跳过本应用笔记前面的部分。 注 : 在本文中,除非特别说明, I2S 一词指 STM32L1xx 微控制器中实现的 SPI 外设的 I2S 特性 1 I2S 一般说明 1.1 I2S 协议 I2S(集成电路内置音频总线)是音频数据传输标准,它使用三线总线进行串行和同步数据传输。 数据在 SD (串行数据)线上传输,格式为小端序 (先传 MSB)。数据长度不受限制 (通常为 16/20/24/32 位)。发送器数据通过 SCK (串行时钟)的上升沿或下降沿同步,接收器用SCK 的下降沿。请参见图 1。 数据表示的是立体声数字音频,所以每个采样包含两个字 —— 右声道采样和左声道采样。它并不使用两个数据通道,而是执行复用,在半个采样周期传输一个字,这样就将采样率加倍,可在每周期传输两个字。 它使用控制信号 WS (字选择)确定正在发送的字是右声道还是左声道。此信号还决定了数据的开始和结束:因此无需固定数据长度。因此,接收器和发送器数据长度可以不同,右声道和左声道数据长度也可以不同。 WS 同步到 SCK 的上升沿或下降沿,比 MSB 早一个 SCK 周期,以便有足够时间做储存和移位运算。 与大多数通信协议一样,必须有主设备和从设备。主设备提供并控制 SCK 时钟和 WS 信号,从设备仅发送或接收数据。主设备可以是接收器、发送器或第三设备(控制器)。请参见图 2。 ![MUKL[I0H%W9(]4DNK0[CWRC.png MUKL[I0H%W9(]4DNK0[CWRC.png](data/attachment/forum/202212/02/134438iyz66iq7dyi3plyh.png)

1.2 STM32L1xx I2S 特性讲解 STM32L1xx 将 I2S 特性实现为 SPI 外设的一个模式。用户必须选择 SPI 模式或 I2S 模式(软件配置)。 STM32L1xx I2S 仅有单工模式 (仅接收或仅发送),通信方向由软件配置。 I2S 外设支持四种音频协议 (可由软件配置): • I2S 飞利浦协议 • MSB 协议 • LSB 协议 • PCM 协议 (包括 PCM 短帧和 PCM 长帧) 它还支持大多数音频频率 (8 kHz、 16 kHz、 22.05 kHz、 32 kHz、 44.1 kHz、 48 kHz 等)数据格式可编程为 16、 24 或 32 位数据长度 (每通道), MSB 在前,以及 16 或 32 位包长度 (每通道)。 WS 信号的分配由硬件管理,并有一个相应的标志位 (CHSIDE)监控通道侧 (仅飞利浦、MSB 和 LSB 标准)。 I2S 外设可配置为音频通信中的主设备或从设备。I2S 使用 9 位预分频生成其自身时钟(独立于寄存器与 APB 总线接口所使用的 SPI 时钟),其设计可达到精确音频频率 (8 kHz、 16 kHz、22.05 kHz、44.1 kHz、32 kHz、48 kHz 等)(a)。当配置为主模式时,外设能以固定速 率输出额外的主时钟 (MCLK):256 × FS (其中 FS 为音频频率)。 若需决定是否生成 MCLK,应考虑下述因素: • 外部 I2S 器件的需要 (编解码器 /DAC)。 一般来说,这些器件需要主时钟 (一般速率为 256 × FS)以执行内部和采样工作。 • 在某些情况下,音频频率精度会因为启用 MCLK 输出而下降。 可使用下述方式中的一种控制音频通信: – 通过轮询 TXE/RXNE 标志 (SPI_CR2 寄存器中的位 1/0):等待 TXE/RXNE 标志置位,然后向 / 从 SPI_DR 寄存器写 / 读通道波形数据。(适合测试 / 小型应用等) – TXE/RXNE 上的中断:配置并启用发送 / 接收中断。在中断子程序中,向 / 从SPI_DR 寄存器写 / 读通道波形数据。(适合大多数应用 /RT 软件等) – DMA 传输:配置 DMA,在每个 Rx/Tx 请求时从 / 向 SPI_DR 寄存器加载 / 卸载。(适合高性能需求。) 注 : 在 I2S 模式中,DMA 的用法与 SPI 模式完全相同(对于所支持的音频传输协议,I2S 模式中 无法用 CRC 特性)。 SYSCLK 频率的选择直接影响 I2S 的传输质量(在主模式中):采样时钟(CK)和 WS 时钟直接由 SYSCLK 用 9 位分频器得到,以获取最精确的 FS 频率。为得到最大精度,预分频器允许奇数次除二 (使用 SPI_I2SPR 寄存器中的 ODD 位)。 因为 SYSCLK 的低频率 (最大 32 MHz),低精度因子时的分频值会导致音频质量下降。当 STM32L1xx I2S 外设在主模式中生成主时钟时,精度因子会降低。请查阅参考手册 (RM0038:STM32L100xx、 STM32L151xx、 STM32L152xx 和 STM32L162xx 基于 ARM®的高级 32 位 MCU)根据目标采样频率确定音频频率精度。 完整版请查看:附件 |

使用 STM32L1xx 微控制器与外部 I2S 音频编解码器播放音频文件.pdf

下载416.21 KB, 下载次数: 5

微信公众号

微信公众号

手机版

手机版