.png) STMCU小助手

发布时间:2021-12-12 21:00

STMCU小助手

发布时间:2021-12-12 21:00

|

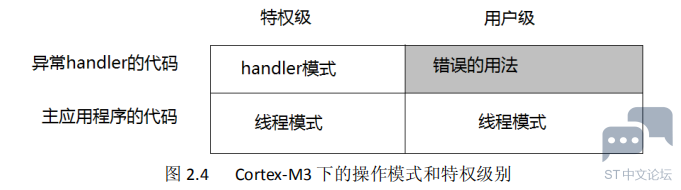

MPU(内存保护单元) 1. 前言 在跟项目过程中,使用的F7和H7两个芯片,在用FSMC和FPGA通信时,由于其CACHE的原因,导致数据一直出错,后来通过加入MPU顺利解决此问题。因此,去学习了一下MPU,在此记录下学习的笔记,可能有理解错误的地方,欢迎指出。 参考: STM32F7中文参考手册.pdf STM32F7编程手册.pdf STM32 MPU说明.pdf Cortex M3权威指南(中文).pdf STM32F7开发指南-寄存器版本_V1.0.pdf 2. 操作模式和特权级别 详情------Cortex M3权威指南(中文).pdf-----chpt02 2.1操作模式 Handler模式:异常服务相关的代码 线程模式:普通应用相关的代码 个人理解是如中断服务程序的代码与正常执行的代码。 2.2 特权级别 分:a.特权级 b.用户级 区别在于对存储器的访问权限不同,特权级相当于管理员权限,除了MPU限制的区域外其他都可以访问,而并不是所有区域都对用户级开放。 2.3 联系

正常执行的应用程序代码,对特权级和用户级开放;但是异常代码如中断服务程序,仅能对特权级开放。

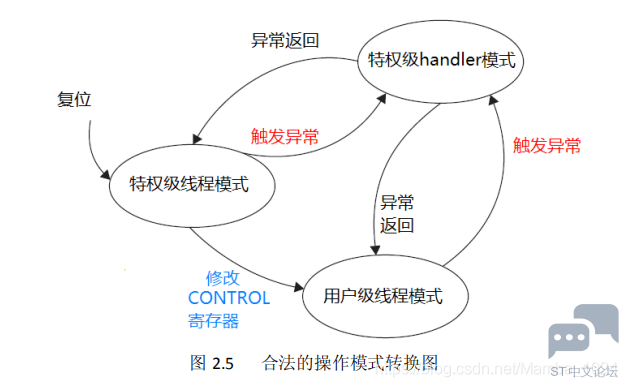

如图:当产生异常时要去执行异常代码,执行完成返回到断点。而无论在用户级还是特权级线程模式下,即使是用户级,在进入handler代码时也会暂时被提升到特权级模式,因为handler模式不能被用户级访问。 特权级可任意访问,包括切换到用户级,仅需要修改CONTROL寄存器即可。 但是用户级切换到特权级不同,需要先申诉(执行SVC指令,触发该异常,进入异常服务代码),由于异常服务代码中是特权级模式,因此可以任意修改CONTROL寄存器,这样才能将用户级----转换---->特权级。 3. MPU Memory Protect Uint-----内存保护单元 3.1 作用 参考了以上的PDF,大致说了以下的作用。

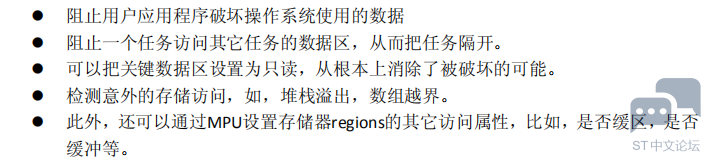

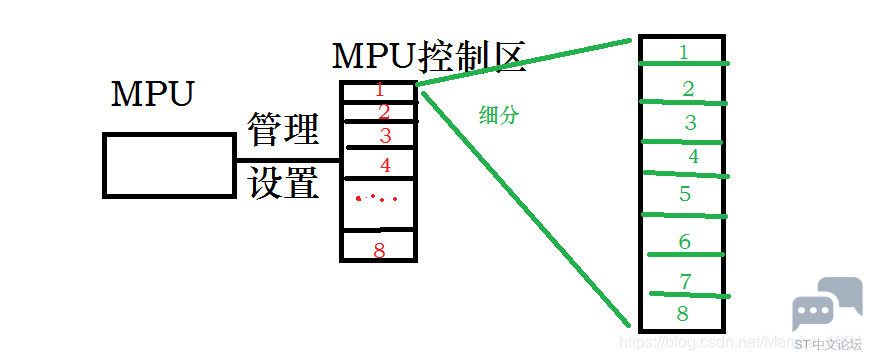

其实更多给我的理解是:通过MPU对存储器的某些区域进行属性设置,设置其对特权级/用户级开放,可读可写/只读/只写、禁止访问、全访问、支持/禁止CACHE、缓冲等等的属性,通过MPU管理存储器,不至于某块内存被非法访问、数据破坏、CACHE等等。 3.2 REGION(区) STM32F7支持8个区,也就是说,MPU控制器通过8个区来管理存储器。 如果8个区不够,每个区都可以再细分为8个子区。大概理解图如下

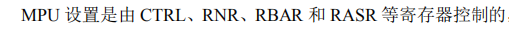

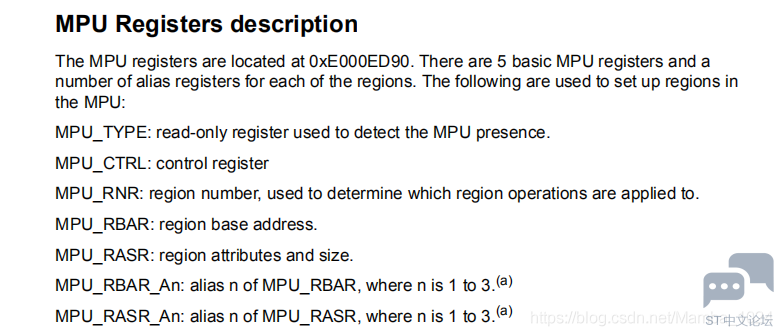

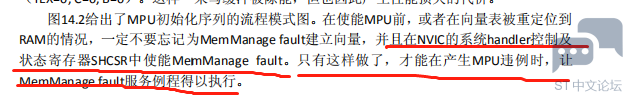

背景区 背景区,即没有被设置到MPU管理区的其他所有地址,背景区只能被特权级访问。否则出现MemManage异常,如果开了MemManage,会进入MemManage中断服务程序。 3.3 MPU寄存器 M3权威指南中的MPU寄存器

原子教程中的寄存器

M7 MPU手册

MDK工程中MPU控制器的寄存器

其中

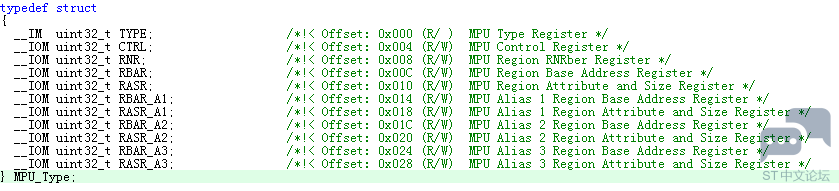

可以看出MPU指向0xE000ED90,并结合MPU_Type类型,可以推算出,其每个寄存器的地址,都和M3权威手册中的寄存器对得上,因此放心操作。 MPU 控制寄存器(CTRL)

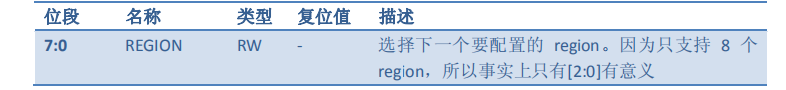

仅三个位有效 PRIVDEFENA:配置为1,特权级能访问背景区,用户级不行,而配置为0,仅能访问REGION区,其他都会出错,包括属于背景区的区域。 HFNMIENA:用于在NM1或者FAULT中断关闭MPU ENABLE:使能 编号寄存器(RNR)

配置每个区时要先写该寄存器,MPU控制器就知道在配置哪个区。比如要配置REGION 1,需要向RNR寄存器写入一个1;配置好后需要配置REGION5,仍向RNR写入5。 MPU 基地址寄存器(RBAR)

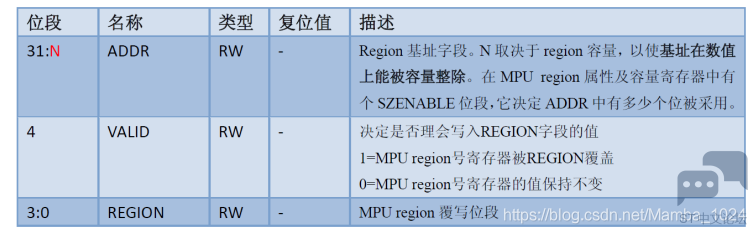

一般不适用VALID位和REGION位,这两位的意思是覆盖RNR里面的值,也就是这两个的值才是我们正在配置的REGION,RNR不生效。 ADDR:配置MPU某个REGION管理的存储器的基地址,要求是----需要该地址需要是REGION大小的整数倍,比如REGION1设置为64K,那么ADDR的值需要如0X0001 0000、0X0002 0000等,0X0001000065536/102464K刚刚好 MPU 区域属性和容量寄存器(RASR)

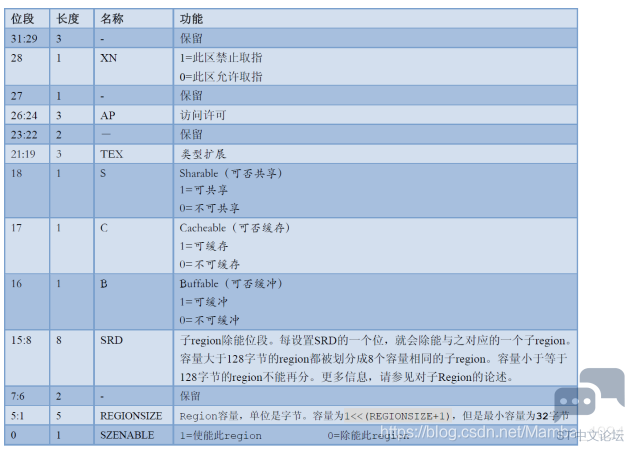

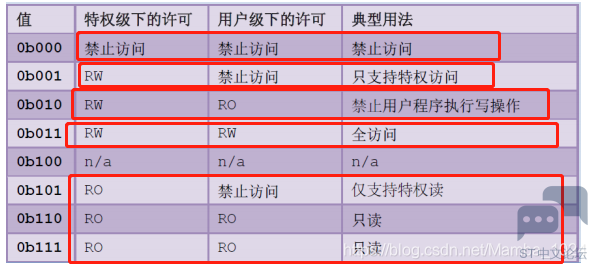

XN:设置的REGION区管理范围是否允许取指 AP:基本是6种形式。

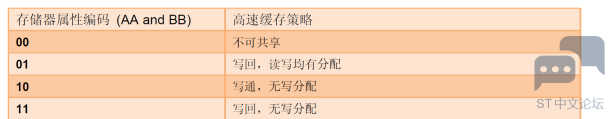

分别是:全禁止(任何级别不可读写),只特权可读可写,用户级不可写,任何级别可读可写,只特权只读,只读。 TXE,C,B,S

其中: 强序-------------按照程序一条指令一条指令顺序执行。 共享------------一块内存可同时被多个设备访问,比如两个DMA同时访问某个区域。 缓冲------------类似有个缓冲器,但是要考虑是否有数据缓冲的阈值,未验证。 缓存-----------CACHE,有命中和MISS,可能造成数据不一致,但是效率较快。 写回-----------CPU更新到CACHE,仅当需要丢弃时CPU将数据更新到主存,期间数据不一致。 写通-----------CPU更新数据时,CACHE和主存都更新。 注意 M3权威指南中,P195,需要SHCSR使能MEM中断。

3.3 相关代码 初始化,将SRAM 0X20002000设置为128字节,不可共享/缓冲/CACHE,且只能特权级读

测试,写入一个值,即进入MEM中断

|

STM32F745 USART1 Bootloader启动失败排查与解决的流程分析

STM32芯片命名规则

STM32 引脚到底有多少?为什么一个引脚能当好几个用?

入门嵌入式,为什么STM32是“优选起步”?

嵌入式-单片机-STM32 EXTI中断

STM32单片机进行除零运算,为何程序不崩溃?

STM32 LL为什么比HAL高效?

STM32时钟详解

2025国庆中秋活动体验报告2——TouchGFX的UI设计

2025国庆中秋活动体验报告1——TouchGFX环境配置

微信公众号

微信公众号

手机版

手机版