|

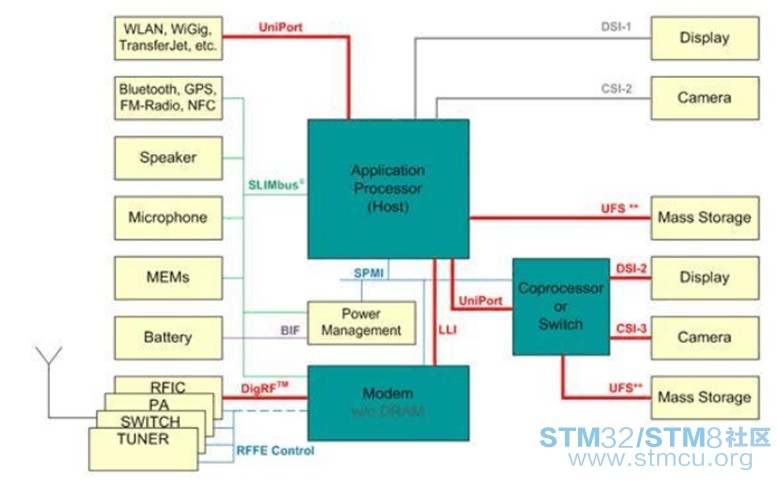

本帖最后由 wolfgang2015 于 2018-7-21 12:07 编辑 $ }' S) q7 d. p* V4 D6 q& p- v/ [* Y 按计算机单片机学习惯例,先来点理论的东西~~ " N0 ]) q# J% |, H) Y( Z ( A/ T6 e# w7 a2 ]0 G) {* K! n 一、初识硬件 在16年ST官方就推出了STM32F769-DISCO开发板,功能搭配可算得上眼前为之一亮,无论是POE、是SPDIF输入输出、是MEMS麦克风、是音频编解码器、还是TFT电容触摸LCD显示屏,各种器件与STM32F769NI这块芯片恰到好处搭配。这块开发板的厚重底蕴难以形容,搭配恰如其分,相得益彰,完美的与STM32F769NI这可主控芯片融合。 根据“芯片诚可贵,内存价根高,若为显示器,二者皆可抛”的原则,首先映入眼帘的就是这800*400MIPI DSI屏幕了。于是乎5W1H顿升腾,什么是MIPI ?什么又是MIPI DSI? 怎么操控?与传统的8080控制又有什么区别呢?转baidu去也,在横、纵浏览各种资料后,MIPI庞大的知识体系跃入眼帘: 2 O7 `/ Y# c# a! x8 c: I6 O 1、 MIPI MIPI联盟,即移动产业处理器接口(MobileIndustry Processor Interface 简称MIPI)联盟。MIPI(移动产业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准和一个规范。 MIPI联盟是2003年由ARM、诺基亚、意法半导体和德州仪器这四家发起公司成立的一个联盟目的是把搜集内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。 MIPI联盟下面有不同的组分别定义一系列的手机内部接口标准,如: 摄像头接口CSI; 射频接口DigRF; 显示接口DBI、DPI、DSI、DCS; 高速同步接口HIS; 低速多点连接(麦克风/喇叭接口)LIMbus; 物理层D-PHY、M-PHY; 系统电源管理 SPMI; 统一协议UniPro 1 Point-to-point、PIE; 7 b8 y1 G9 L. `0 d- [7 C- M, o$ kMIPI规划的下一代智能手机的内部架构:- _3 M8 _* G' l+ ?' p# |' P9 n

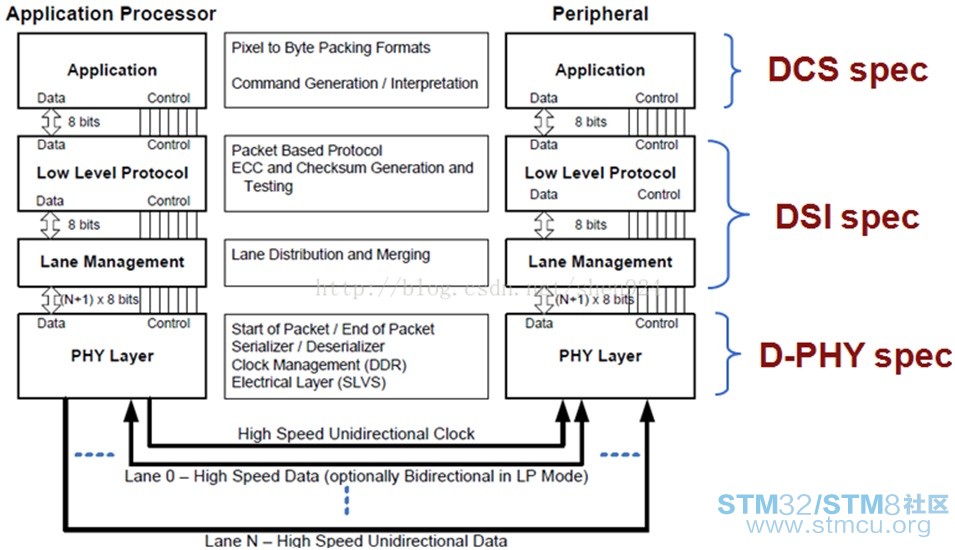

除了发起成员外MIPI联盟目前还包括:安捷伦科技、ATI科技、Atsana、奥地利微电子、Cambridge Silicon Radio、Dice、Emblaze Semiconductor、爱立信移动平台、FASL LLC、Icera Semiconductor、Imagination Technologies、IMEC、Infineon Technologies、Marvell International、明导、M-Systems、美国国家半导体、NeoMagic、Nvidia、Omnivision、飞利浦电子、Renesas Technologies、三星电子、精工爱普生、Sendo、西门子、索尼爱立信、Symbian、Synaptics、东芝、Transchip Israel Research、TTPCom和中星微电子公司等这些新成员。(难怪当初第一眼看见STM32F769IDISCO会有手机的感觉,你说是不是呢?) 6 I& h4 T/ l( ?+ _: E1 P/ K' I联盟成员几乎遍及每一个移动领域,包括主要的移动电话贴牌生产厂商、外围设备制造商、应用处理器生产商、存储器供应商、软件开发商和知识产权持有者。 5 w1 L! m* Z b9 K" G6 R' Z- E原来MIPI是这么有庞大组织的一个联盟成员,话说当初说苹果手机重新定义了手机,能触动进行手机重新定义的其中一个功臣非MIPI不可。 1 ?$ y; Y, @/ i; J1 V& O6 e, _4 H0 u6 k+ h. C2 [: L$ f 2、 MIPIDSI a) DSI相关规范名词解释: •DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。 •DSI(DisplaySerialInterface)定义了一个位于处理器和显示模组之间的高速串行接口。 •CSI (CameraSerialInterface)定义了一个位于处理器和摄像模组之间的高速串行接口。 •D-PHY:提供DSI和CSI的物理层定义 b) DSI分层结构: 分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:

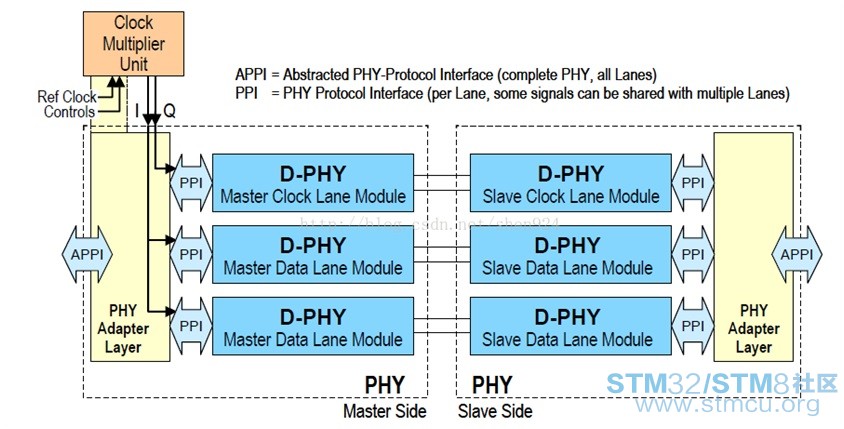

• PHY定义了传输媒介,输入/输出电路和和时钟和信号机制。' M5 ~& [* o# N' {* q7 f& } • Lane Management层:发送和收集数据流到每条lane。8 I3 z" I! f. H% ` ) z& p; f: P/ C- n• Low Level Protocol层:定义了如何组帧和解析以及错误检测等。* l' @& z& a& b0 Z, ^5 Z' n0 } • Application层:描述高层编码和解析数据流。 c) Command和Video模式 • DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定& X2 c) P8 J& m% } : s; k1 i* f: Q+ {• Command模式是指采用发送命令和数据到具有显示缓存的控制器。主机通过命令间接的控制外设。Command模式采用双向接口 • Video模式是指从主机传输到外设采用时实象素流。这种模式只能以高速传输。为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径 3、 D-PHY介绍 a) D-PHY描述了一同步、高速、低功耗、低代价的PHY。 • 一个 PHY配置包括 • 一个时钟lane • 一个或多个数据lane 两个Lane的 PHY配置如下图

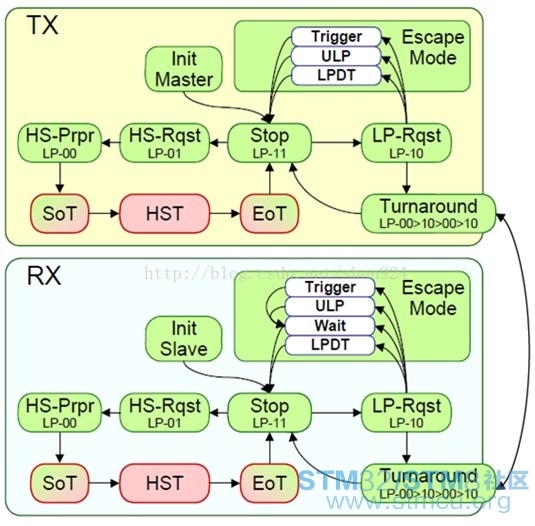

& v1 [' t/ a; \ 三个主要的lane的类型 • 单向时钟Lane • 单向数据Lane • 双向数据Lane D-PHY的传输模式 • 低功耗(Low-Power)信号模式(用于控制):10MHz (max) • 高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane D-PHY低层协议规定最小数据单位是一个字节 • 发送数据时必须低位在前,高位在后 . G$ e2 \5 c+ G; a; I1 B; hD-PHY适用于移动应用 • DSI:显示串行接口 • 一个时钟lane,一个或多个数据lane • CSI:摄像串行接口 , g. v0 E2 f5 f+ J* I8 Mb) Lane模块 PHY由D-PHY(Lane模块)组成 • D-PHY可能包含: • 低功耗发送器(LP-TX) • 低功耗接收器(LP-RX) • 高速发送器(HS-TX) • 高速接收器(HS-RX) • 低功耗竞争检测器(LP-CD) 三个主要lane类型 • 单向时钟Lane • Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX • 单向数据Lane • Master:HS-TX, LP-TX • Slave:HS-RX, LP-RX • 双向数据Lane • Master, Slave:HS-TX, LP-TX, HS-RX,LP-RX, LP-CD c) Lane状态和电压 Lane状态 • LP-00, LP-01,LP-10, LP-11 (单端) • HS-0, HS-1 (差分) Lane电压(典型) • LP:0-1.2V HS:100-300mV (200mV) d) 操作模式 数据Lane的三种操作模式 • Escape mode, High-Speed(Burst) mode,Control mode 从控制模式的停止状态开始的可能事件有: •Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00) •High-Speed mode request (LP-11→LP-01→LP-00) •Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00) Escape mode是数据Lane在LP状态下的一种特殊操作 •在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger •数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00 •一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作 •Escapemode 使用Spaced-One-HotEncoding 超低功耗状态(Ultra-Low PowerState) •这个状态下,lines处于空状态 (LP-00) •时钟Lane的超低功耗状态 •时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态 •通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms 7 ~# c+ w7 x4 o) W& d0 Q. O高速数据传输 •发送高速串行数据的行为称为高速数据传输或触发(burst) •全部Lanes门同步开始,结束的时间可能不同。 •时钟应该处于高速模式 各模操作式下的传输过程 •进入Escape模式的过程 :LP-11→LP-10→LP-00→LP-01→LP-00→EntryCode → LPD (10MHz) •退出Escape模式的过程:LP-10→LP-11 •进入高速模式的过程:LP-11→LP-01→LP-00→SoT(00011101) → HSD (80Mbps ~ 1Gbps) •退出高速模式的过程:EoT→LP-11 •控制模式 - BTA 传输过程:LP-11→LP-10→LP-00→LP-10→LP-00 •控制模式 - BTA 接收过程:LP-00→LP-10→LP-11 - n" G) B+ O* n$ T% {状态转换关系图

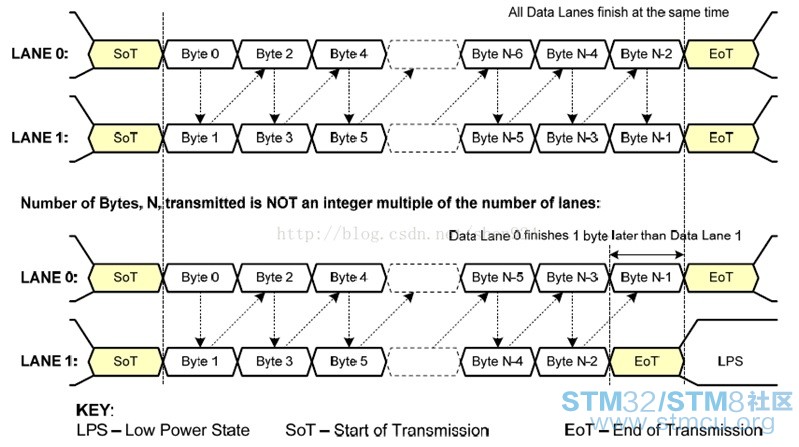

4、 DSI介绍 a) DSI是一种Lane可扩展的接口,1个时钟Lane/1-4个数据Lane • DSI兼容的外设支持1个或2个基本的操作模式: • Command Mode(类似于MPU接口) • Video Mode(类似于RGB接口)- 必须用高速模式传输数据,支持3种格式的数据传输 • Non-Burst 同步脉冲模式 • Non-Burst 同步事件模式 • Burst模式 传输模式: • 高速信号模式(High-Speed signaling mode) • 低功耗信号模式(Low-Power signaling mode) - 只使用数据lane 0(时钟是由DP,DN异或而来)。 帧类型 • 短帧:4 bytes (固定) • 长帧:6~65541 bytes (可变) • 两个数据Lane高速传输示例

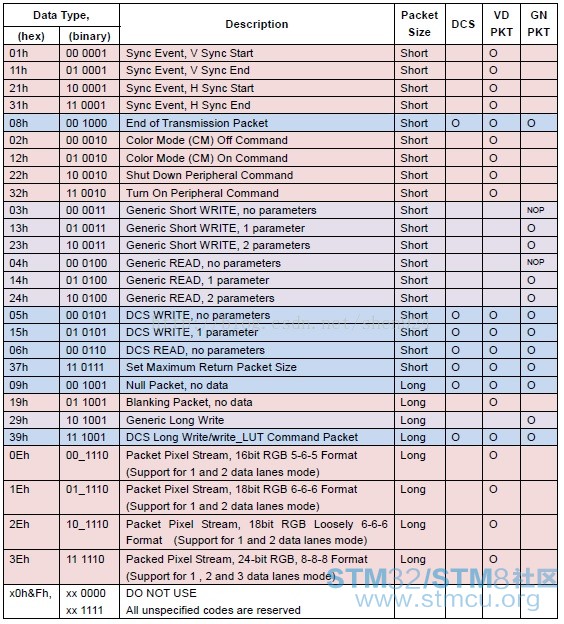

b) 短帧结构 帧头部(4个字节) • 数据标识(DI) 1个字节 • 帧数据- 2个字节 (长度固定为2个字节) • 错误检测(ECC) 1个字节 帧大小 • 长度固定为4个字节 c) 长帧结构 帧头部(4个字节) • 数据标识(DI) 1个字节 • 数据计数- 2个字节 (数据填充的个数) • 错误检测(ECC) 1个字节 数据填充(0~65535 字节) • 长度=WC*字节 帧尾:校验和(2个字节) 帧大小: • 4 + (0~65535) + 2 = 6 ~ 65541 字节 d) 帧数据类型

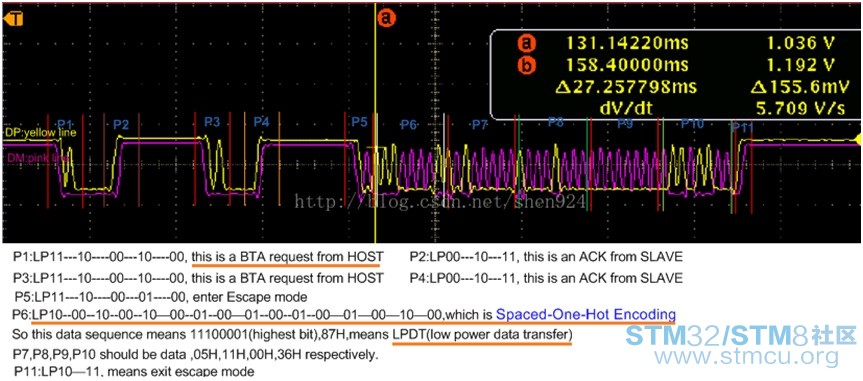

5、 MIPI DSI信号测量实例 a) MIPIDSI在Low Power模式下的信号测量图

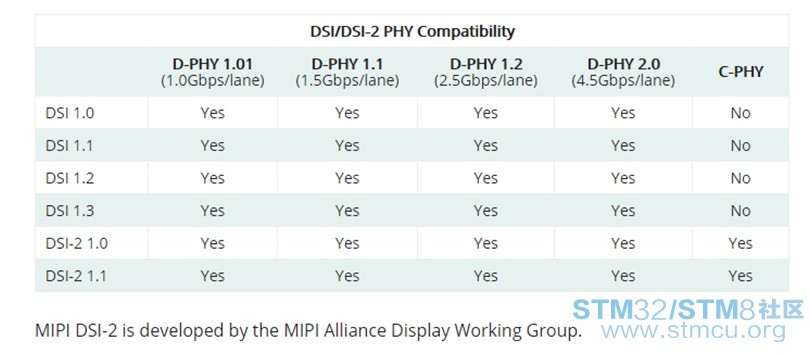

b) MIPI的D-PHY和DSI的传输方式和操作模式 D-PHY和DSI的传输模式 • 低功耗(Low-Power)信号模式(用于控制):10MHz (max) • 高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~1Gbps/Lane D-PHY的操作模式 • Escape mode, High-Speed(Burst) mode,Control mode DSI的操作模式 • Command Mode(类似于MPU接口) • Video Mode(类似于RGB接口)- 必须用高速模式传输数据 & U$ }4 B" S. v) \+ e4 @; pc) 小结论 • 传输模式和操作模式是不同的概念 • Video Mode操作模式下必须使用High-Speed的传输模式 • Command Mode操作模式并没有规定使用High-Speed或Low Power的传输模式,或者说 • 即使外部LCD模组为Video Mode,但通常在LCD模组初始化时还是使用Command Mode模式来读写寄存器,因为在低速下数据不容易出错并且容易测量。 • Video Mode当然也可以用High-Speed的方式来发送指令,Command Mode操作模式也可以使用High-Speed,只是没有必要这么做。 另外DSI的协议版本也在不断增添新的成员,如下图: 最新的MIPI DIS-2协议也在2016年1月发布:

; B) ?+ Z3 Z% b; j* p STM32F769I-DISCO开发板GUI学习内容(二)_课前硬件基础6 _/ a+ O0 C. n* L( f) K: E: I5 t j& b STM32F769I-DISCO开发板GUI学习内容(三)_课前预习之CubeMX篇(上)4 q9 Y, x1 `3 `% b, R STM32F769I-DISCO开发板GUI学习内容(三)_课前预习之CubeMX篇(下)4 E7 L5 S \( B1 j STM32F769I-DISCO开发板GUI学习内容(四)_课后动手实验 |

| 前排,学习下 |

| 谢谢楼主的分享! |

| 学习学习 |

| 好资料 |

| 学习学习 |

【实战经验】基于STM32F7的网络时间同步例程

STM32硬件结构学习

STM32中BOOT的作用

【STM32F769I-DISC1】开发板刷入Micropython并完成点灯、读取内部温度测试

【STM32L562E-DK】健康手环基础界面开发(一)—— 准备工作

【STM32F769I-DISC1】测评01:创建STM32cube IDE 工程,点个灯

【STM32F769】创建deepseek本地服务,并实现http请求

汇编浮点库qfplib移植STM32F769I-DISCO开发板与硬件浮点运算性能测试对比

coremark移植到STM32F769I-DISCO开发板的两种方法

【GUI板免费申请活动】【圣诞GUI】使用F746-DISO基于TouchGFX的圣诞树

微信公众号

微信公众号

手机版

手机版