|

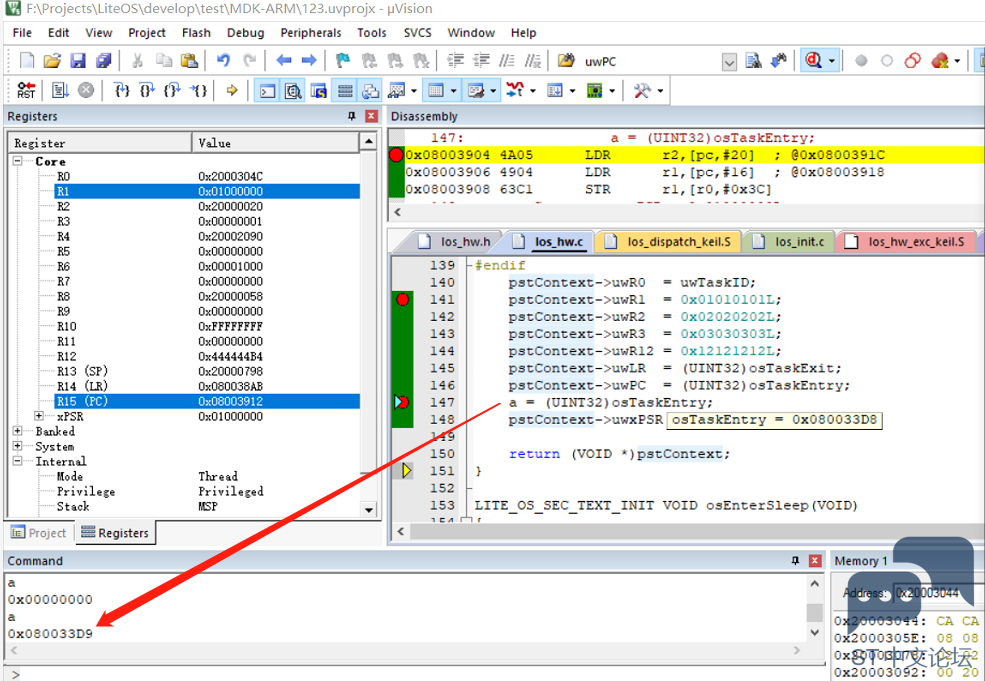

最近在做LiteOS系统的移植,需要将任务地址(函数地址)赋值给任务堆栈,但是在过程中发现,被赋值的变量会比实际的函数地址多1。比如有函数地址为0x080033D8,将其赋值给变量a后,则变量a的结果会变成0x080033D9,并且将a和该函数地址做比较结果也是相等的,具体现象如下图:

*pxTopOfStack = ( ( StackType_t ) pxCode ) & portSTART_ADDRESS_MASK; /* PC */ 即它特地使用了portSTART_ADDRESS_MASK在任务地址赋值的时候根据用户设置,决定最低位是否清零。 因此个人推断: ARM会根据T标志,在对PC寄存器的数据操作时,会相应地操作LSB,如果T标志为1则将PC的值复制到目标寄存器后同时将保障结果的LSB为1. 不知道这种推断是否正确,哪位朋友知道相关的权威资料? |

|

对于cortex M核的芯片,任何跳转相关地址的最低位,即BIT0都应是1。该位表示将用到的的指令集为Thumb指令。这点在ARM公司提供的各内核的Generic User Guide里 有提及:Bit[0] of any address you write to thePC with a BX, BLX, LDM,LDR, or POPinstruction must be 1for correctexecution, because this bit indicates the required instruction set, and theCortex-M4 processoronly supports Thumb instructions |

微信公众号

微信公众号

手机版

手机版