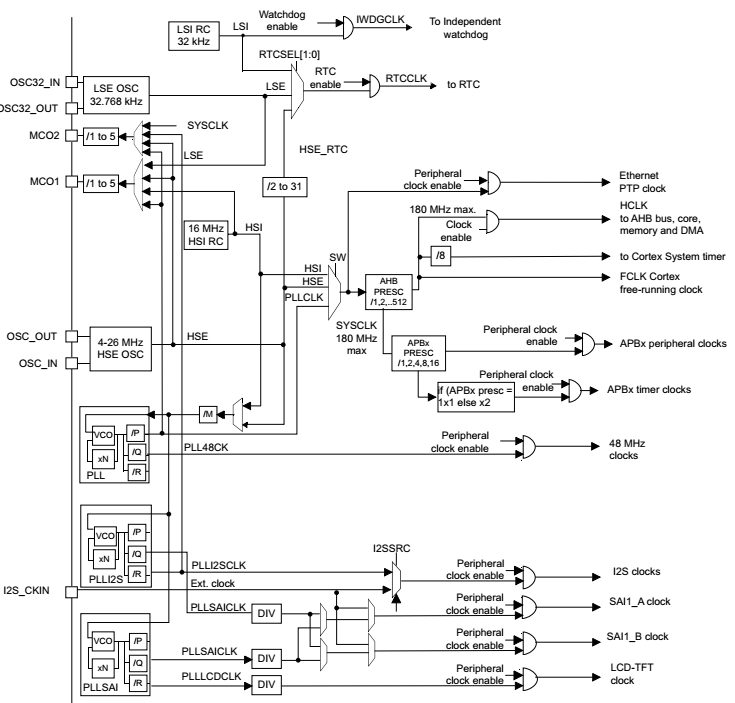

今天来分析一下STM32F429的时钟系统,首先上一个时钟树的图吧

从上面的图可以看出STM32F429拥有3个PLL,其中主PLL主要用于Cortex-M4核心和片上的大部分外设,PLLI2S主要用于I2S音频系统模块,而PLLSAI则用于SAI音频模块和LCD模块。并且这三个PLL的时钟源一样,都是取自HSI或HSE经过/M分频得到的。每个PLL的输出频率可有以下公式得到CLK = ( (输入频率 / M分频) * N) / 输出分频(/P,/Q,/R)。时钟系统的操作方式这和以前的STM32F1差不多。 |

微信公众号

微信公众号

手机版

手机版

RE:【STM32F429开发日志】应用笔记(二)时钟系统

回复:【STM32F429开发日志】应用笔记(二)时钟系统