|

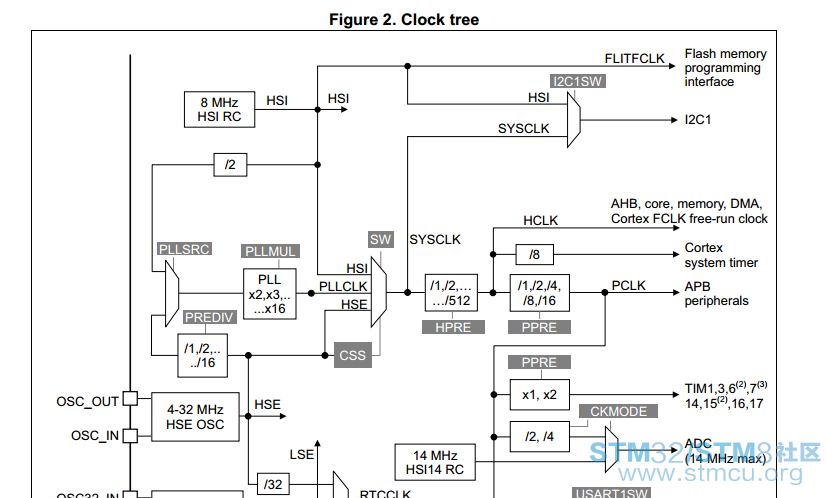

首先我将STM32F0xx.h中做以下更改: #if !defined (HSE_VALUE) #define HSE_VALUE ((uint32_t)16000000) /*!< Value of the External oscillator in Hz*/ #endif /* HSE_VALUE */ 其次 SystemInit ()中SetSysClock()如下: static void SetSysClock(void) { __IO uint32_t StartUpCounter = 0, HSEStatus = 0; /******************************************************************************/ /* PLL (clocked by HSE) used as System clock source */ /******************************************************************************/ /* SYSCLK, HCLK, PCLK configuration ----------------------------------------*/ /* Enable HSE */ RCC->CR |= ((uint32_t)RCC_CR_HSEON); /* Wait till HSE is ready and if Time out is reached exit */ do { HSEStatus = RCC->CR & RCC_CR_HSERDY; StartUpCounter++; } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT)); if ((RCC->CR & RCC_CR_HSERDY) != RESET) { HSEStatus = (uint32_t)0x01; } else { HSEStatus = (uint32_t)0x00; } if (HSEStatus == (uint32_t)0x01) { /* Enable Prefetch Buffer and set Flash Latency */ FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY; /* HCLK = SYSCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; /* PCLK = HCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE_DIV1; /* PLL configuration */ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL)); RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLMULL6); /* Enable PLL */ RCC->CR |= RCC_CR_PLLON; /* Wait till PLL is ready */ while((RCC->CR & RCC_CR_PLLRDY) == 0) { } /* Select PLL as system clock source */ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW)); RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL; /* Wait till PLL is used as system clock source */ while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL) { } } else { /* If HSE fails to start-up, the application will have wrong clock configuration. User can add here some code to deal with this error */ } } 该如何更改? |

PREDIV æ¯ä¸æ¯å¯ä»¥åé¢å¢ï¼

请都大神--STM32F072CB芯片开启HSI48时钟问题

谁能解释一下STM32F0的RTC_IRQHandler中断中EXTI_Line17的作用?

【STM32F0开发日志/评测/笔记】+互补PWM波的产生

STM32F030 PB14和PB15无法输出PWM求助

【STM32F030探索套件】序列之五 外部中断

【STM32F0开发日志---二】+ucosii.2.92移植在STM32F030

上传个STM32F0+5110+内部温度传感器的菜鸟实例

【STM32F030探索套件使用问题】STM32F030 SPI方式驱动ST7565LCD失败

求一份STM32F051 I2C驱动LCD 12864的例程

STM32F0 M0 向结构体赋值进入HardFault异常

微信公众号

微信公众号

手机版

手机版