|

STM32F4xxxx MCU 硬件开发入门 前言 本应用笔记为系统设计人员提供了所需的开发板硬件实现概述,关注如下特性:

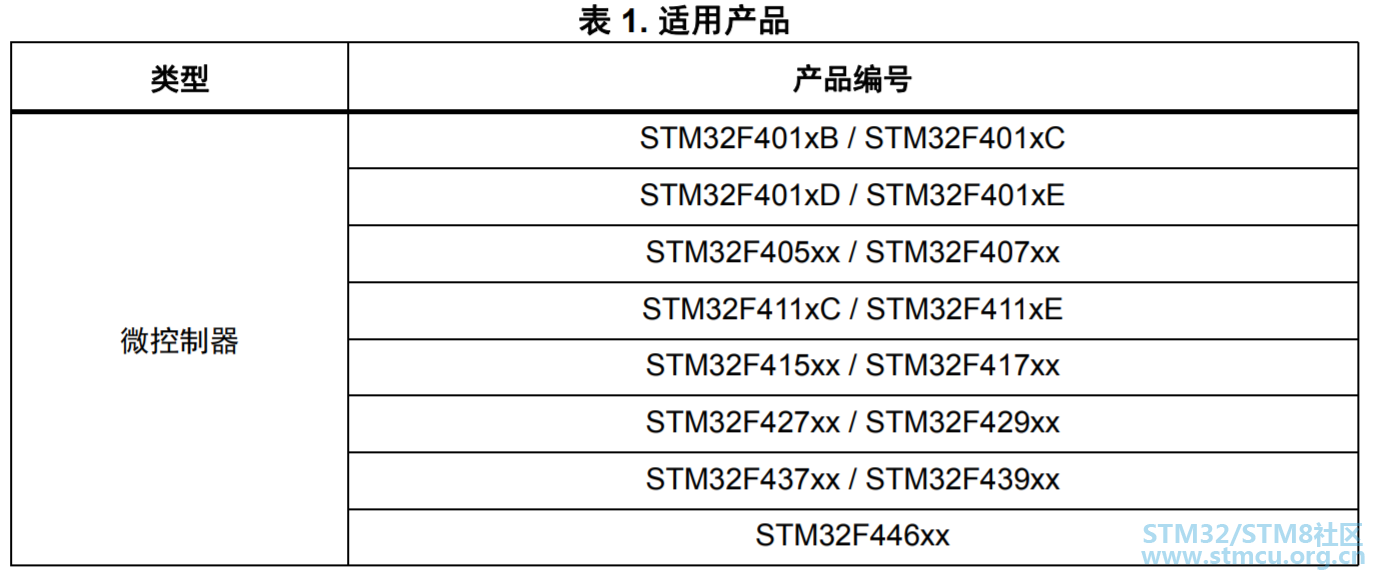

本文档展示了如何使用表 1 中列举的大容量高性能微控制器,同时讲述了基于这些产品开发应用所需的最低硬件资源要求。 本文还包括了详细的参考设计原理图,说明了其主元件、接口和模式。

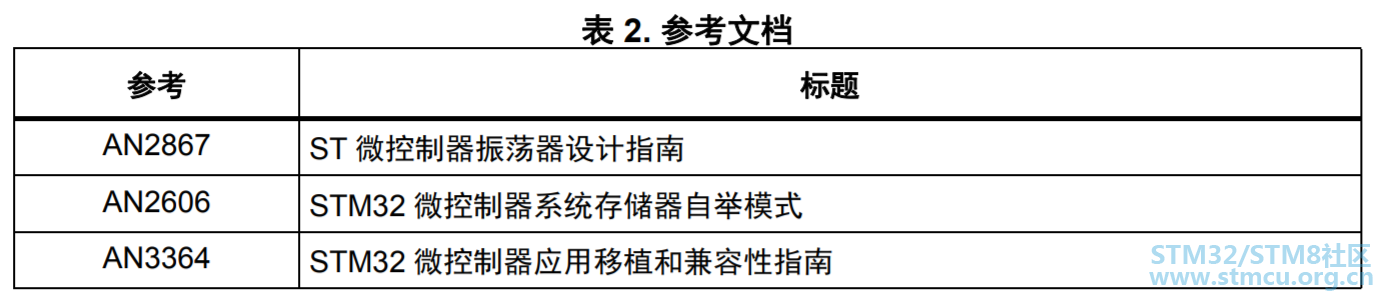

1 参考文档 以下文档可从 www.st.com 获得。

2 电源 2.1 前言 工作电压 (VDD) 范围是 1.8 V 到 3.6 V,正如产品数据手册所述,在某些约束条件下也可以降低至 1.7 V。内嵌的稳压器用于提供内部 1.2 V 数字电源。 当主电源 VDD 断电时,可通过 VBAT 电压为实时时钟 (RTC) 和备份寄存器供电。 2.1.1 独立 A/D 转换器电源和参考电压 为了提高转换精度, ADC 配有独立电源引脚,可以单独滤波并屏蔽 PCB 上的噪声。

在具有 100 个或更多引脚的封装上 为了确保测量低电压时具有更高的精度,用户可以在 VREF+ 上连接单独的 ADC 外部参考电压输入。 VREF+ 上的电压的取值范围是从 (VDDA- 1.2 V) 到 VDDA (最小值为 1.7 V)。 当存在 Vref- 引脚时 (取决于封装), VREF- 必须从外部连至 VSSA。 在具有少于 100 个引脚的封装上 当 VREF+ 引脚和 VREF- 引脚没有引出时,它们内部连至 ADC 电源电压 (VDDA) 和地 (VSSA)。 2.1.2 电池备份 为了在 VDD 关闭后保留备份寄存器的内容,可以将 VBAT 引脚连接到电池或其它电源供电的可选备用电压。 VBAT 引脚还为 RTC 单元供电,因此即使当主数字供电 (VDD)关闭时 RTC 也能工作。 VBAT 电源的开关由复位模块中内置的掉电复位 (PDR)电路进行控制。 若应用中没有使用外部电池,则强烈建议将 VBAT 外部连至 VDD。 |

| 已读 |

| 收藏 |

微信公众号

微信公众号

手机版

手机版