|

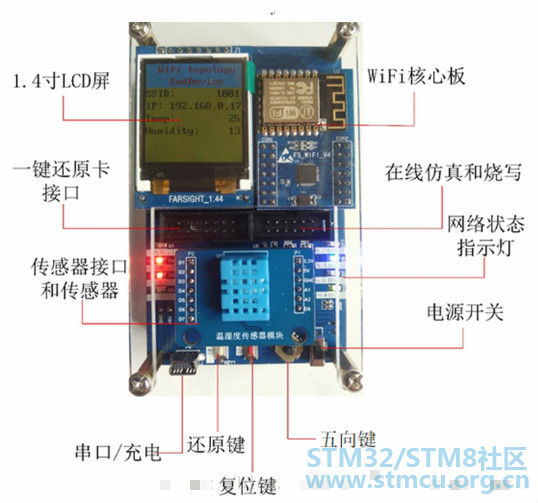

一、ARM体系结构概述内容概述: 必须要get到的ARM知识 Cortex-M0处理器介绍 认识STM32 STM32F0硬件平台介绍

STM32的核心部件CPU是Cortex-M 系列处理器

ARM处理器家族:

早先经典处理器 包括ARM7、ARM9、ARM11家族。

Cortex-M 系列 为单片机驱动的系统提供的低成本优化方案,应用于传统 的微控制器市场,智能传感器,汽车周边部件等。

Cortex-A 系列 针对开放式操作系统的高性能处理器; 应用于智能手机,数字电视,智能等高端运用。

Cortex-R 系列 针对实时系统、满足实时性的控制需求; 应于汽车制动系统,动力系统等。

ARM处理器架构:

概念:体系结构定义指令集和基于这一体系结构下处理器的 编程模型(基本数据类型、工作模型、寄存器组)。基于同种体系结构可以有多种处理器、每个处理器的性能不同,面向的应用领域也不同。

ARM体系结构发展:

目前ARM体系架构共定义了8个版本V1-V8 V1-V3 最早的版本,目前已废弃 V4-V6 经典处理器中运用的比较多 V7 目前Cortex系列处理器主要是这种架构、支持Thumb-2的32位指令集 V8 兼容ARMv7架构的特性,并支持64位数据处理

ARM指令集: 指令集的概念:处理器能够识别并执行的指令集合;每一条指令可处理一个简单或复杂操作(加、加乘…);每一条指令对应一条或几条汇编指令。

指令集常见分类: 复杂指令集(CISC):包含处理复杂操作的特定指令,指令长度不固定,执行需要多个周期。 精简指令集(RISC):指令简单而有效,格式和长度通常是固定的,大多数指令在一个周期内可以执行完毕,ARM的内核是基于RISC体系结构的

SOC的概念: SOC(片上系统)指的是在单个芯片上集成一个完整的计算机系统,所谓完整的系统一般包括中央处理器(CPU)、存储器、以及外围电路等。

Cortex-M0处理器介绍 主要内容: Cortex-M0处理器简介 Cortex-M0体系结构 Cortex-M0异常和中断 Cortex-M0指令集

Cortex-M0处理器简介: Cortex-M 系列产品主要包括 Cortex-M0、Cortex-M1、Cortex-M3、Cortex-M4、Cortex-M7 等,其中 Cortex-M0 主打低功耗和混合信号的处理,M3 主要用来替代 ARM7,重点侧重能耗与性能的平衡,而 M7 则重点放在高性能控制运算领域。

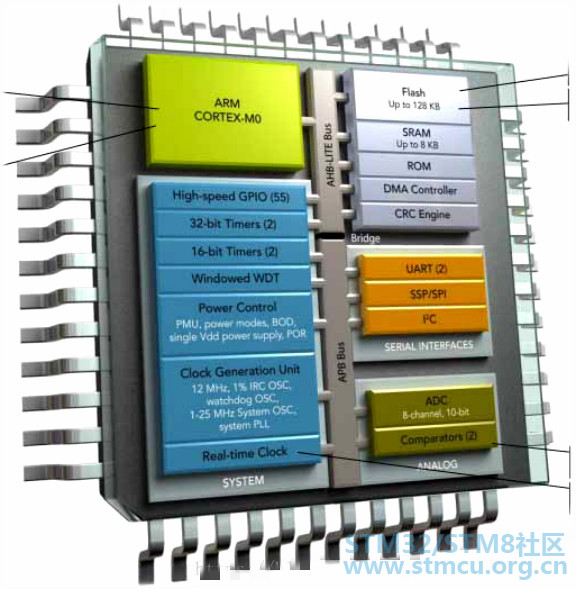

注:STM32F051微控制器内核就是ARM Cortex-M0 Cortex-M0结构框图:

Cortex-M0 微处理器主要包括处理器内核、嵌套向量中断控制器(NVIC)、调试子系统、内部总线系统构成。Cortex-M0 微处理器通过精简的高性能总线(AHB-LITE)与外部进行通信。

Cortex-M0特性: Thumb 指令集,高效、高代码密度; 高性能,使用ARMv6-M的体系架构; 中断数量可配置(1~32 个),4 级中断优先级,低中断切换时延,提供不可屏蔽中断(NMI)输入保障高可靠性系统; 门电路少,低功耗,处理器可在休眠状态下掉电以降低功耗,还可被 WIC 唤醒; 与 Cortex-M1 处理器兼容,向上兼容 Cortex-M3 和 Cortex-M4 处理器,可以很容易地升级到 Cortex-M3。Cortex-M3 和 Cortex-M4 移植到 Cortex-M0 也非常简单。

支持多种嵌入式操作系统,也被多种开发组件支持,包括 MDK(ARM Keil 微控制器开发套件)、RVDS(ARM RealView 开发组件)、IAR C 编译器等。

Cortex-M0工作模式: Cortex-M0有两种工作模式和两种工作状态: 线程模式(Thread Mode): 芯片复位后,即进入线程模式,执行用户程序; 处理模式(Handler Mode)。 当处理器发生了异常或者中断,则进入处理模式进行处理、处理完成后返回线程模式。 Thumb状态:正常运行时处理器的状态 调试状态:调试程序时处理器的状态

Cortex-M0寄存器组——通用寄存器:

Cortex-M0 处理器内核有 13 个通用寄存器以及多个特殊寄存器,如图 所示。具体介绍如下:

R0-R12:通用寄存器。其中 R0-R7 为低端寄存器,可作为 16 位或 32 位指令操作数,R8-R12 为高端寄存器,只能用作 32 位操作数 R13:堆栈指针 SP,Cortex-M0 在不同物理位置上存在两个栈指针,主栈指针 MSP,进程栈指针 PSP。在处理模式下,只能使用主堆栈,在线程模式下,可以使用主堆栈也可以使用进程堆栈,这主要是由 CONTROL 寄存器控制完成。 系统上电的默认栈指针是MSP R14:连接寄存器(LR),用于存储子程序或者函数调用的返回地址 R15:程序计数器(PC),存储下一条将要执行的指令的地址。

Cortex-M0寄存器组——特殊寄存器:

xPSR:组合程序状态寄存器,该寄存器由三个程序状态寄存器组成:

应用PSR(APSR):包含前一条指令执行后的条件标志 中断PSR(IPSR): 包含当前ISR的异常编号 执行PSR(EPSR) : 包含Thumb状态位

PRIMSK:中断屏蔽特殊寄存器。

CONTROL:控制寄存器。 控制处理器处于线程模式时,使用哪个堆栈: =0,使用MSP =1,使用PSP 处理器模式时,固定使用MSP

Cortex-M0异常和中断:

Cortex-M0 处理器最多支持 32 个外部中断(通常称为 IRQ)和一个不可屏蔽中断(NMI),另外 Cortex-M0 还支持许多系统异常(Reset、HardFault、SVCall、PendSV、SysTick),它们主要用于操作系统和错误处理,参见下表

Cortex-M0指令集:

ARM 处理器支持两种指令集:ARM 和 Thumb。

EPSR 寄存器的 T 标志位负责指令集的切换,Cortex-M0只支持Thumb指令。

ARM指令集:32位精简指令集; 指令长度固定; 降低编码数量产生的耗费,减轻解码和流水线的负担。

Thumb指令集:Thumb指令集是ARM指令集的一个子集; 指令宽度16位; 与32位指令集相比,大大节省了系统的存储空间; Thumb指令集不完整,所以必须配合ARM指令集一同使用。

注:Thumb 与 ARM 相比,代码体积小了 30%,但性能也低了 20%。2003 年,ARM 公司引入了 Thumb-2 技术,具备了一些 32 位的 Thumb 指令,使得原来很多只有 ARM 指令能够完成的功能,用 Thumb 指令也可以完成了。Cortex-M0 基于的 ARMv6-M 体系结构,该体系结构的处理器只是用了16位Thumb指令和部分32位Thumb指令

内容概述:

STM32的应用 STM32产品的介绍 STM32产品命名规范 STM32F0体系架构 STM32:从字面上来理解,ST 是意法半导体,M 是 Microelectronics 的缩写,32 表示32 位,合起来理解,STM32 就是指 ST 公司开发的 32 位微控制器。在如今的 32 位控制器当中,STM32 可以说是最璀璨的新星,它受宠若娇,大受工程师和市场的青睐,无芯能出其右。

STM32的应用: 可穿戴 物联网 无人机 工业控制 医疗电子 汽车电子 电力系统 石油系统 燃气系统 …….

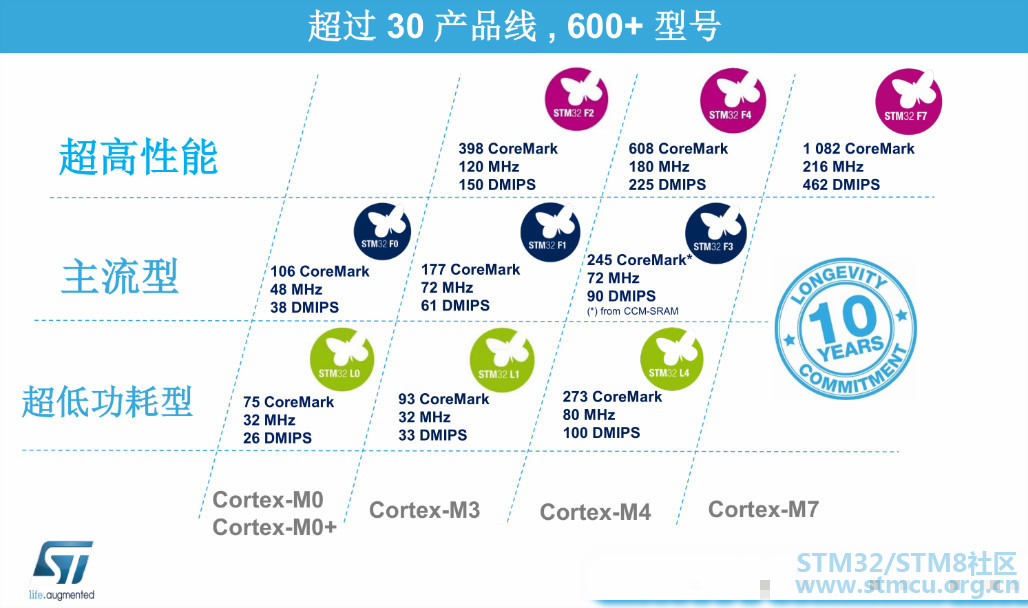

STM32产品介绍:

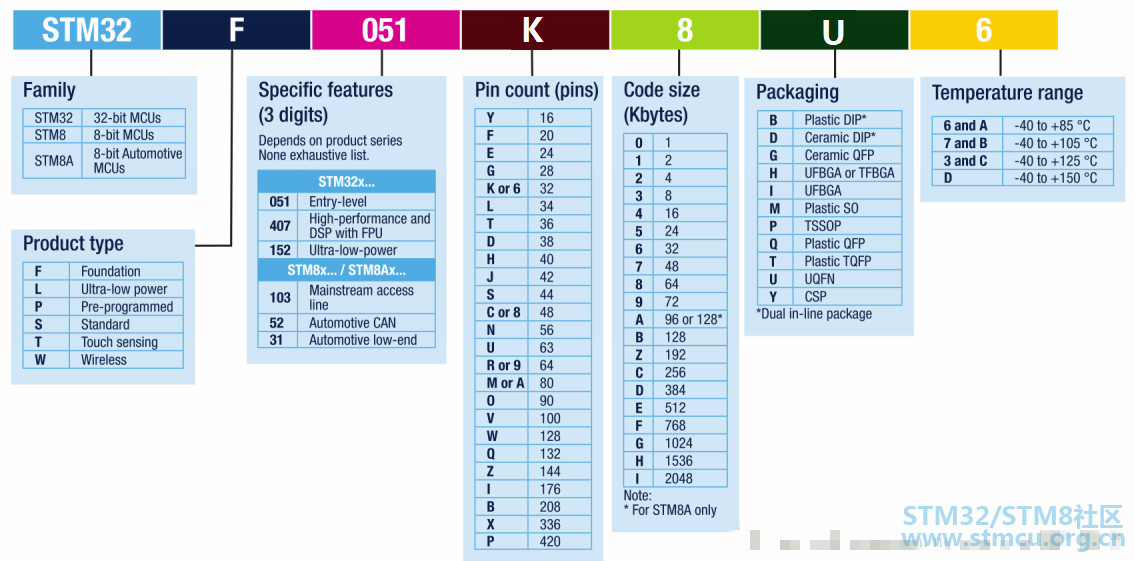

STM32产品命名规范:

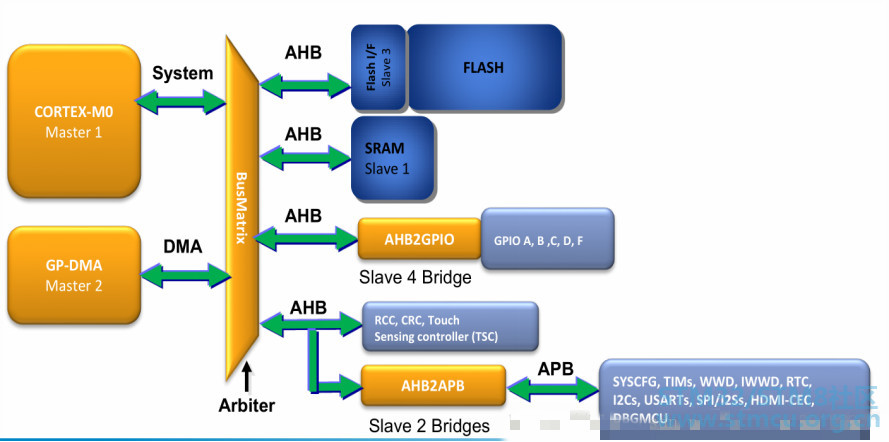

STM32F0系统架构:

系统主要由以下几个模块组成 :

二个主模块 :

Cortex-M0 内核及先进高性能总线 (AHB bus) 通用 DMA ( GP-DMA -- general-purpose DMA)

四个从模块 : 内部 FLASH 内部SRAM 专门用于连接 GPIO 口的 AHB2 AHB 到 APB 的桥 , 所有的外设都挂在 APB 总线上

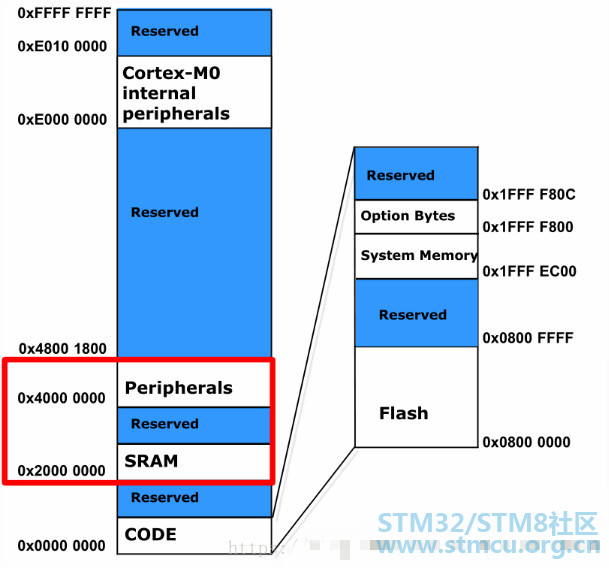

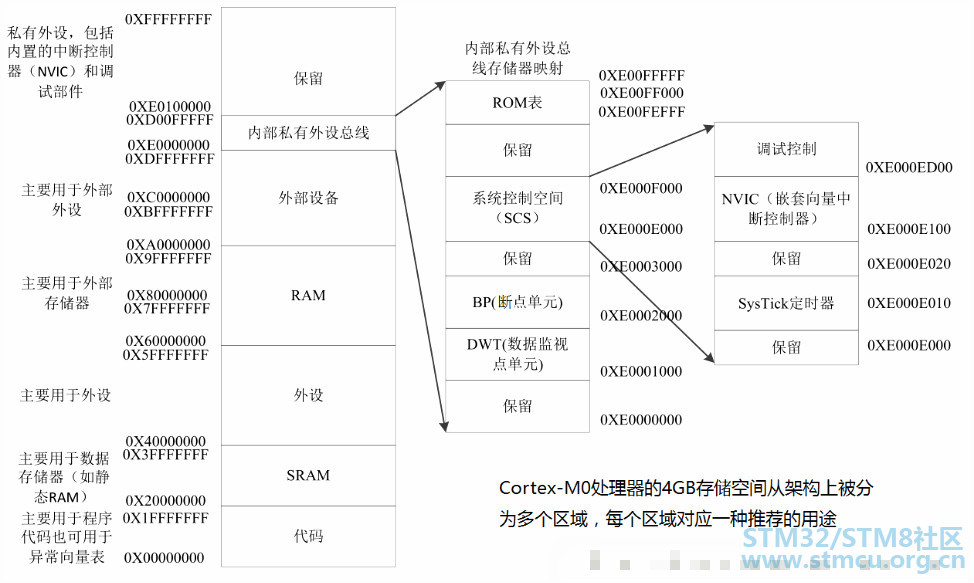

二、STM32开发环境搭建内容概要: Keil MDK-ARM简介及安装 STM32CubeMX简介及安装 STM32F0存储器映射 STM32F0启动文件分析 STM32F0存储器映射 内容概述: Cortex-M0存储器映射 STM32F0存储器映射 寄存器的访问方式 Cortex-M0存储器映射:

存储器本身没有地址,给存储器分配地址的过程叫存储器映射

注:被控单元的FLASH,RAM和AHB到APB的桥(即片上外设),这些功能部件共同排列在一个 4GB 的地址空间内。我们在编程的时候,可以通过他们的地址找到他们,然后来操作他们

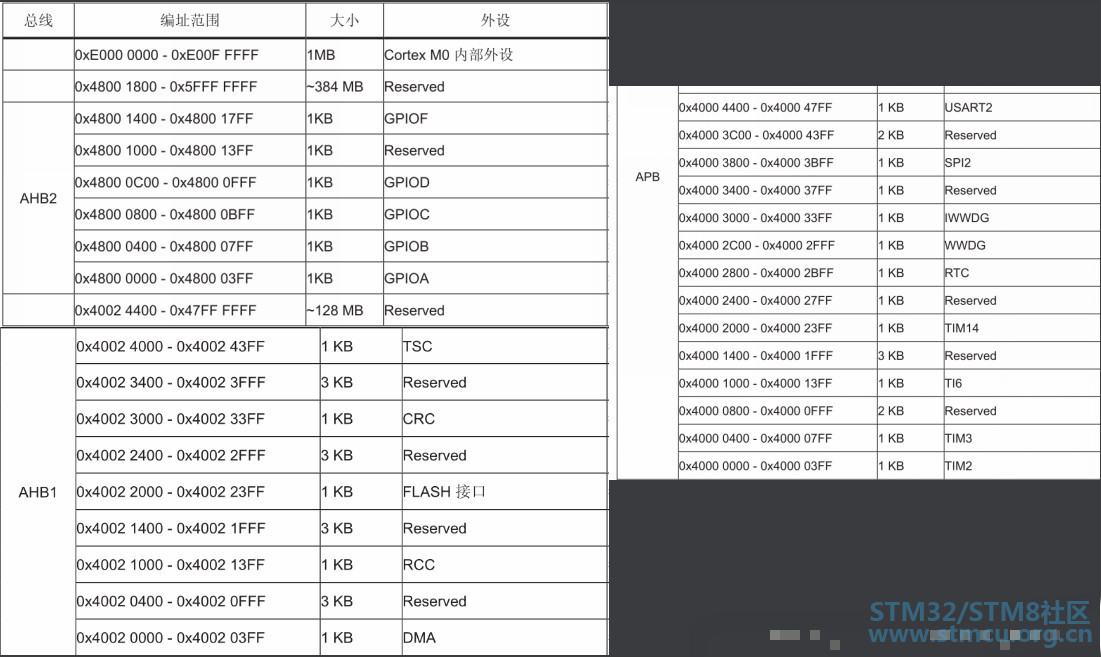

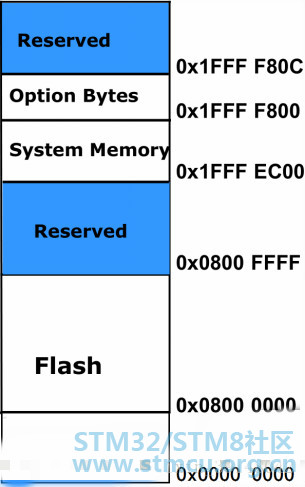

STM32F0存储器映射:

可寻址4GB字节空间 多达64KB片上闪存 多达8K的SRAM

STM32F05x 存储器映像和外设寄存器编址:在芯片手册上可查到

寄存器访问:

以GPIOA寄存器组为例,读写ODR寄存器方法: 已知GPIOA的起始地址为0x48000000

各寄存器的偏移地址如下: MODER; /*Address offset: 0x00 */ OTYPER; /*Address offset: 0x04 */ OSPEEDR; /*Address offset: 0x08 */ PUPDR; /*Address offset: 0x0C */ IDR; /*Address offset: 0x10 */ ODR; /*Address offset: 0x14 */ BSRR; /*Address offset: 0x18 */ LCKR; /*Address offset: 0x1C */ 第一种方式:对地址进行宏定义

改进

第二种方式:用结构体封装寄存器 用上面的方法去定义地址,还是稍显繁琐、根据我们每一类外设对应的寄存器组地址都是连续增长的特点,我们引入 C 语言中的结构体语法对寄存器进行封装

注:我们访问GPIOA的控制寄存器组时、直接使用宏定义好 GPIO_TypeDef 类型的指针,而且指针指向 GPIOA端口的首地址,这样我们直接用宏GPIOA访问改外设的任意一个寄存器 GPIOA->MODER = 0x20 ; GPIOA->OSPEEDR = 0x16 ;

内容概要: STM32F0启动模式 C语言程序内存排布 启动文件startup_stm32f051.s分析

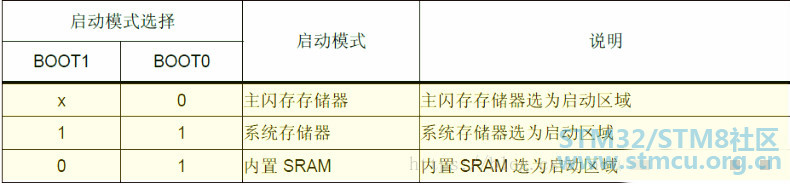

STM32F0的启动模式:

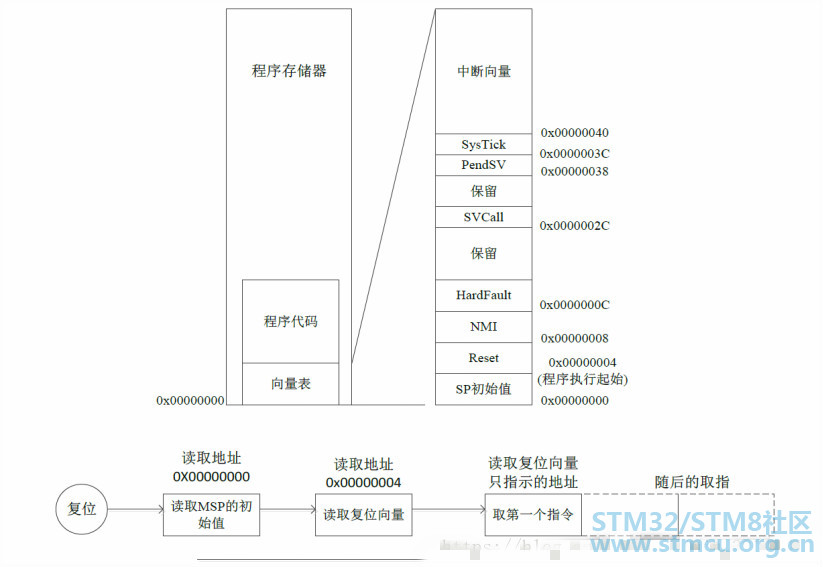

注:Cortex-M0 的程序映像通常是从地址 0x00000000 开始的、系统复位后,处理器首先读取向量表中的前两个字(8 个字节),第一个字存入 MSP,第二个字为复位向量,它表示程序执行的起始地址(复位处理)

根据启动模式的不同,用户闪存、系统闪存和SRAM都 可以映射到0x0的低端地址; 我们的板子boot0直接接地,因此启动区域为flash启动

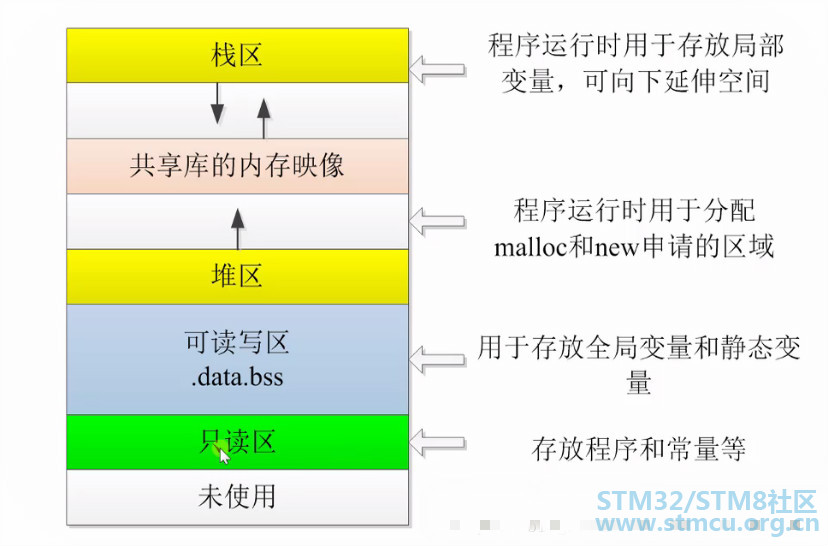

C语言内存排布:

注:栈的作用是用于局部变量,函数调用,函数形参等的开销 堆主要用来动态内存的分配 |

| 谢谢分享,学习一下 |

【MCU实战经验】+基于stm32L的低功耗物联网温度测量节点

【NUCLEO-WBA65RI评测】物联网 LED

【NUCLEO-WBA65RI评测】蓝牙体温计

【NUCLEO-WBA65RI评测】Home Assistant 物联网心率计

意法半导体与高通达成无线物联网战略合作

《RT-Thread设备驱动开发指南》书籍学习记录

[STM32WB55评测] 开箱

【我心中的STM32WBA52】

【我心中的STM32WBA52】

将STM 32 Lora DiscoveryKit连接到AWS物联网(三)

微信公众号

微信公众号

手机版

手机版