.png) STMCU小助手

发布时间:2021-11-28 21:00

STMCU小助手

发布时间:2021-11-28 21:00

|

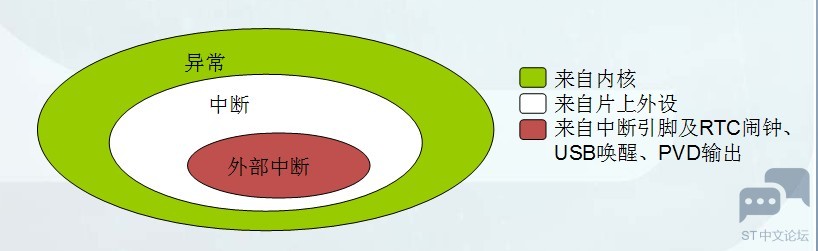

stm32是一款基于cortex m3的单片机,其对中断的控制在核内部,因此stm32对中断处理与cortex m3区别不大 一、几个概念 异常与中断:《权威指南》译者给出的定义为:“所有能打断正常执行流的事件都称为异常”、“异常与中断的区别在于,那240个中断对CM3核来说是‘突发事件’,也就是说该请求信号来自CM3核的外面,对CM3核来说是‘异步’的;而异常则是因CM3核的活动产生的,在执行指令或访问存储器时产生的,对CM3核是‘同步’的”。我认为他第一句和第二句矛盾。对这个问题有两个理解: 第一种就是第一句的理解。第二种理解为:编号(权威手册表述)0~15的为异常,16~255的‘外部中断’就是中断。我认为这只是概念的冲突,并不影响对芯片的使用,本文采用第一种理解。 外部中断:对这个概念的理解有两个出发点,若讨论内核,则来自核以外的中断,即编号16~255的都叫外部中断。另外一种是从stm32芯片出发来理解,所谓的“外部”是指受EXTI控制的中断。本文研究的是单片机,采用第二种理解,同时把16~255号称为中断。

事件与通道。事件还不能算为一个中断。上面谈到的16~255号中断,在stm32中其实是中断通道的概念,多个要申请中断的事件可能会公用一个中断通道,在核看来他们是一样的,只有在中断服务子程序里读标志位才能分辨到底是谁申请的中断。就好像一个宿舍里好几个人,通过一部公用电话给警局报警,警局只知道是这个号码(中断通道)报的警,但不知道是宿舍里哪一个人(事件),若想知道是谁在打电话,则需要询问(读相关标志位,如TIM_GetITStatus(TIM3, TIM_IT_Update))。 CM3核支持240个中断,但是,st采用的只有68个,即68个中断通道。 二、优先级 有三个异常,复位、NMI、硬fault的优先级是负的,是最高的,是软件不能编程的,比其他任何异常都高。对他们的理解没有难度,就一个:优先级最高。 再来看其他的异常,他们也有硬件优先级,随着编号的增大而降低。他们的优先级都是可以编程的,软件优先级权限高于硬件。软件优先级数字越大优先级越低。 什么叫抢占。当系统正在相应某异常L时,如果来了抢占优先级更高的异常H,则H可以抢占L。 那么抢占优先级也就好理解了,它是关于中断嵌套的。从优先级则与嵌套无关,当抢占优先级相同的异常有不只一个挂起时,就最先响应从优先级最高的异常。 优先级分组。CM3利用一个字节对中断进行优先级分组。即确定这个字节的几位用来表示抢占优先级,几位表示从优先级。stm32没有用完这一个字节,只用了高四位,所以分组最多有16个抢占优先级,最少没有抢占优先级,对的,没有抢占优先级。《权威指南》里“从优先级至少一位”的说法不准确。 每个中断通道都在NVIC内有一个字节(PRI_N,stm32用到其中高4位)来表示其优先级。 这基本能讲通NVIC的原理了。 |

【评分有奖】STM32 AI Sidekick聊天工具上线,快来体验一下吧!

ST TouchGFX 实操系列视频+如何选择正确的帧缓冲区策略

ST TouchGFX 实操系列视频++如何添加图像

ST TouchGFX 实操系列视频+如何进行屏幕转换

ST TouchGFX 实操系列视频+控件的淡入淡出

ST TouchGFX 实操系列视频+移动控件的三种方法

ST TouchGFX 实操系列视频+如何创建用户界面(UI)

ST TouchGFX 实操系列视频+如何安装TouchGFX Designer和STM32Cube软件环境

【经验分享】STM32F1 GPIO工作原理

【经验分享】STM32F0xx_DMA收发USART数据配置详细过程

微信公众号

微信公众号

手机版

手机版