.png) STMCU小助手

发布时间:2021-12-22 13:22

STMCU小助手

发布时间:2021-12-22 13:22

|

25.1 初学者重要提示 TCM : Tightly-Coupled Memory 紧密耦合内存 。ITCM用于指令,DTCM用于数据,特点是跟内核速度一样,而片上RAM的速度基本都达不到这个速度。 特别注意本章25.5小节里面各块RAM的DMA操作问题。 25.2 各块RAM在总线中的位置 这个知识点在前面章节做过介绍,本章再次梳理下这个知识点。

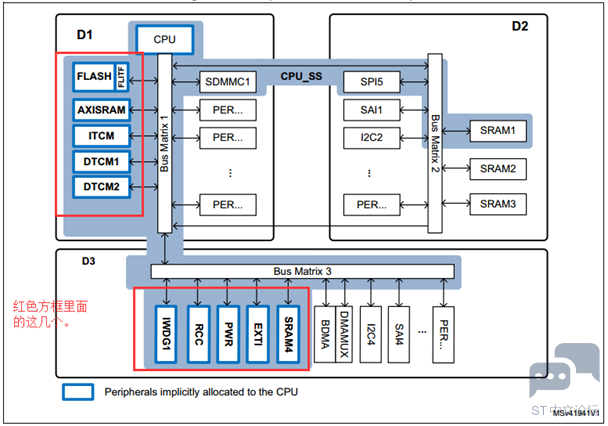

这个图可以方便识别总线所外挂的外设,共分为三个域:D1 Domain,D2 Domain和D3 Domain。 1、 ITCM和DTCM 这两个是直连CPU的。 2、 D1 Domain D1域中的各个外设是挂在64位A**线组成6*7的矩阵上。 6个从接口端ASIB1到ASIB6 外接的主控是LTDC,DMA2D,MDMA,SDMMC1,AXIM和D2-to-D1 AHB 总线。 7个主接口端AMIB1到AMIB7 外接的从设备是AHB3总线,Flash A,Flash B,FMC总线,QSPI和AXI SRAM。另外AHB3也是由A**线分支出来的,然后再由AHB3分支出APB3总线。 3、 D2 Domain D2域的各个外设是挂在32位AHB总线组成10*9的矩阵上。 10个从接口 外接的主控是D1-to-D2 AHB 总线,AHBP总线,DMA1,DMA2,Ethernet MAC,SDMMC2,USB HS1和USB HS2。 9个主接口 外接的从设备是SRAM1,SRMA2,SRAM3,AHB1,AHB2,APB1,APB2,D2-to-D1 AHB总线和D2-to-D3 AHB总线。 4、 D3 Domain D3域的各个外设是挂在32位AHB总线组成3*2的矩阵上。 3个从接口 外接的主控D1-to-D3 AHB总线,D2-to-D3 AHB总线和BDMA。 2个主接口 外接的从设备是AHB4,SRAM4和Bckp SRAM。另外AHB4也是这个总线矩阵分支出来的,然后再由AHB4分支出APB4总线 25.3 各块RAM特性 各块RAM的特性对比如下,特别注意他们支持的最大速度和容量大小。 TCM区 TCM : Tightly-Coupled Memory 紧密耦合内存 。ITCM用于运行指令,也就是程序代码,DTCM用于数据存取,特点是跟内核速度一样,而片上RAM的速度基本都达不到这个速度,所以有降频处理。 速度:400MHz。 DTCM地址:0x2000 0000,大小128KB。 ITCM地址:0x0000 0000,大小64KB。 AXI SRAM区 位于D1域,数据带宽是64bit,挂在A**线上。除了D3域中的BDMB主控不能访问,其它都可以访问此RAM区。 速度:200MHz。 地址:0x2400 0000,大小512KB。 用途:用途不限,可以用于用户应用数据存储或者LCD显存。 SRAM1,SRAM2和SRAM3区 位于D2域,数据带宽是32bit,挂在AHB总线上。除了D3域中的BDMB主控不能访问这三块SRAM,其它都可以访问这几个RAM区。 速度:200MHz。 SRAM1:地址0x3000 0000,大小128KB,用途不限,可用于D2域中的DMA缓冲,也可以当D1域断电后用于运行程序代码。 SRAM2:地址0x3002 0000,大小128KB,用途不限,可用于D2域中的DMA缓冲,也可以用于用户数据存取。 SRAM3:地址0x3004 0000,大小32KB,用途不限,主要用于以太网和USB的缓冲。 SRAM4区 位于D3域,数据带宽是32bit,挂在AHB总线上,大部分主控都能访这块SRAM区。 速度:200MHz。 地址:0x3800 0000,大小64KB。 用途:用途不限,可以用于D3域中的DMA缓冲,也可以当D1和D2域进入DStandby待机方式后,继续保存用户数据。 Backup SRAM区 备份RAM区,位于D3域,数据带宽是32bit,挂在AHB总线上,大部分主控都能访问这块SRAM区。 速度:200MHz。 地址:0x3880 0000,大小4KB。 用途:用途不限,主要用于系统进入低功耗模式后,继续保存数据(Vbat引脚外接电池)。 25.4 各块RAM的时钟问题 正常情况下,系统上电后,CPU要访问的外设是需要使能对应的时钟位,但是下面这几个,CPU上电即可访问,而且芯片没有对应的寄存器使能位。

也就是说AXI SRAM,SRAM4,ITCM和DTCM可以在上电后直接使用。而SRAM1,SRAM2,SRAM3是需要使能的,但是实际测试发现,不使能也可以正常使用。不过,建议用到时候开启下时钟,防止意想不到的问题发生。 对于V7板子配套的例子,在bsp.c文件的函数SystemClock_Config末尾做了个条件编译,大家可以根据需要来开启这三个时钟:

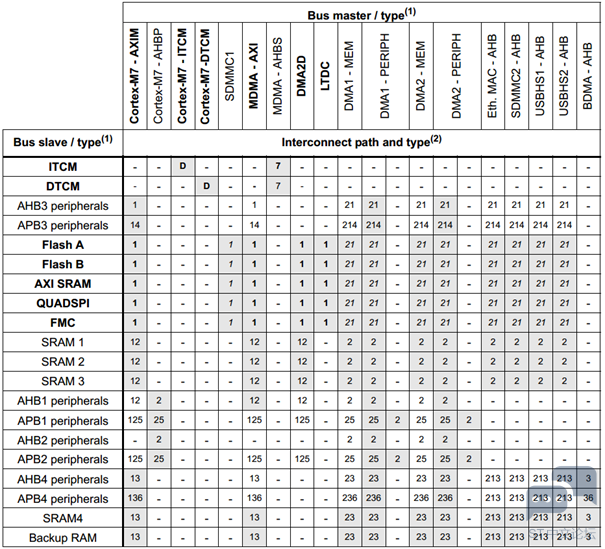

25.5 各块RAM的DMA问题 了解这个问题之前,要先看下面的Bus Master总线主控端和Bus Slave设备端的控制互联:

加粗字体是64位总线(ITCM,DTCM,Flash A,Flash,AXI SRAM,FMC等),普通字体是32位总线。 访问通路(每个小方块里面的字符) 任何有数字的表示有访问通路。 短横杠“-”表示不可访问。 有灰色阴影的表示有实用价值的访问通路。 表格中具体数值所代表的含义 D=direct, 1=via AXI bus matrix, 2=via AHB bus matrix in D2, 3=via AHB bus matrix in D3, 4=via AHB/APB bridge in D1, 5=via AHB/APB bridge in D2, 6=via AHB/APB bridge in D3, 7=via AHBS bus of Cortex-M7, 多个数值组合 = 互连路径以数字的顺序经过多个矩阵或/和桥。 总线访问类型 普通字体表示32位总线。 斜体表示32位总线主机端/ 64位总线从机端。 粗体表示64位总线。 通过这个总线互联图,要了解到下面三个重要知识点: DTCM和ITCM不支持DMA1,DMA2和BDMA,仅支持MDMA。 AXI SRAM,SRAM1,SRAM2,SRAM3不支持BDMA,支持MDMA,DMA1和DMA2。 SRAM4支持所有DMA,即MDMA,DMA1,DMA2和BDMA。 25.6 实际工程推荐的RAM分配方案 鉴于DTCM是400MHz的,而其它的RAM都是200MHz,推荐工程的主RAM空间采用TCM,而其它需要大RAM或者DMA的场合,使用剩余RAM空间。 本教程配套的例子基本都是采用的这个方案,让TCM的性能得到最大发挥。 25.7 总结 本章节就为大家讲解这么多,通过本章节主要是为后面三个章节的学习做铺垫。 |

STM32H750 外扩 QSPI FLASH 跑 2 小时就死机?LAT1151 官方根治方案

STM32H723 多通道序列 ADC 启动不了?寄存器操作必须等 ADRDY 就绪

经验分享 | STM32H7 LPTIM+DMAMUX+BDMA应用演示

经验分享 | STM32H7系列ADC DMA传输异常案例分享

经验分享 | STM32H7 MDMA 与通用DMA的联动传输示例

STM32H750 基于 Keil 制作 QSPI 外部 Flash 下载算法 全流程实操指南

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

微信公众号

微信公众号

手机版

手机版