.png) STMCU小助手

发布时间:2021-12-22 14:45

STMCU小助手

发布时间:2021-12-22 14:45

|

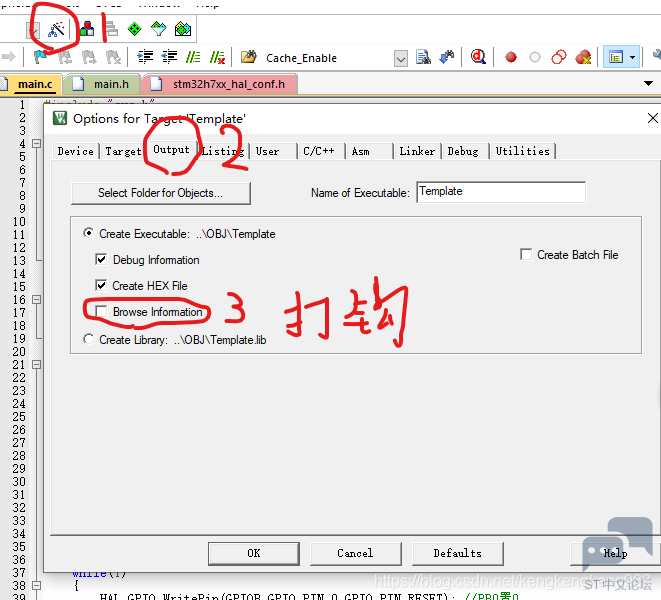

1.前期准备 keil安装 slink安装 STM32Cube安装 2.开发配置 按照 STM32H7开发指南-HAL库版本_V1.0 配置 3.整体把控 1) AXI线:(AXI线在STM32H7中有着举足轻重的作用。高并发性全靠这个总线了) AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。AXI 是AMBA 中一个新的高性能协议。AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。 AXI的特点编辑 单向通道体系结构。信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。 支持多项数据交换。通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。 独立的地址和数据通道。地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。 增强的灵活性。AXI技术拥有对称的主从接口,无论在点对点或在多层系统中,都能十分方便地使用AXI技术。 2)keil MDK需要使用 go to def (跑到定义)的话需作如下操作

… … … 10.STM32H7的FLASH,RAM和栈使用情况 ROM, FLASH和RAM的区别 ROM: 只读存储器-因而常用于存储各种固化程序和数据。 RAM: 随机存储器-所以主要用于存储短时间使用的程序.它主要用来存储程序中用到的变量。凡是整个程序 中,所用到的需要被改写的量(包括全局变量、局部变量、堆栈段等),都存储在RAM中。 flash: 闪存-因此适合用于做程序存储器。 11.第11章看得云里雾里的,哈哈,先放一放 12. STM32H7的HAL库框架设计学习 1)每一次开发新的芯片时都得先设置晶振 HAL库有一个专门的配置文件叫stm32h7xx_hal_conf.h***, 这个文件里面有一个很重要的参数,就是HSE_VALUE*,大家所设计板子使用的实际晶振大小一定要与这个数值一致。比如H750的外置晶振是25MHz,那么这里就务必配置宏定义为: #define HSE_VALUE ((uint32_t)25000000) 2)MCU,CPU,MPU,DSP 13. STM32H7启动过程详解 1) 启动文件 启动文件主要完成如下工作,即程序执行过程:

Cortex-M内核处理器复位后,处于线程模式,指令权限是特权级别(最高级别),堆栈设置为使用主堆栈MSP。 2) BOOT启动模式(H7只需要用boot0 ,我的毕业设计是接地) 关于DMA,TCM(ITCM和DTCM)和CacheDMA DMA: 这是一种通过硬件实现的数据传输机制 TCM: ITCM是cortex内核中指令传输总线,DTCM是cortex内核中数据传输总线, 是cpu内核同flash及sram之 间传输指令和数据的通道, Cache:Cache是集成在CPU内部的极高速的缓存,CPU外设的暂时数据存储,(信差),CPU,访问外设前,先访问它, 如果有数据,就直接拿其数据,没有的话再访问外设 |

STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H723 SPI 通讯异常排查:实时观察窗口的 “隐形干扰” 解决方案

经验分享 | STM32H7 SPI NSS 脉冲模式灵活应用:解决外置 ADC 通信干扰问题

经验分享 | STM32H7 双核调试配置:STM32CubeIDE 下 M7+M4 协同调试实操

经验分享 | STM32H7 TouchGFX 花屏速解:更换 HyperRAM 后 latency 值适配实操

经验分享 | STM32H743 BDMA+LPTIM+LPUART应用演示

经验分享 | STM32H7Sx MCE 加密解密:外部存储安全防护全解析

如何在STM32和Arduino上实现卷积神经网络

详解STM32单片机的堆栈

STM32 开发者指南:ST.com 全新 MCU 产品阵容视觉布局深度解析

微信公众号

微信公众号

手机版

手机版