.png) STMCU小助手

发布时间:2022-3-16 11:01

STMCU小助手

发布时间:2022-3-16 11:01

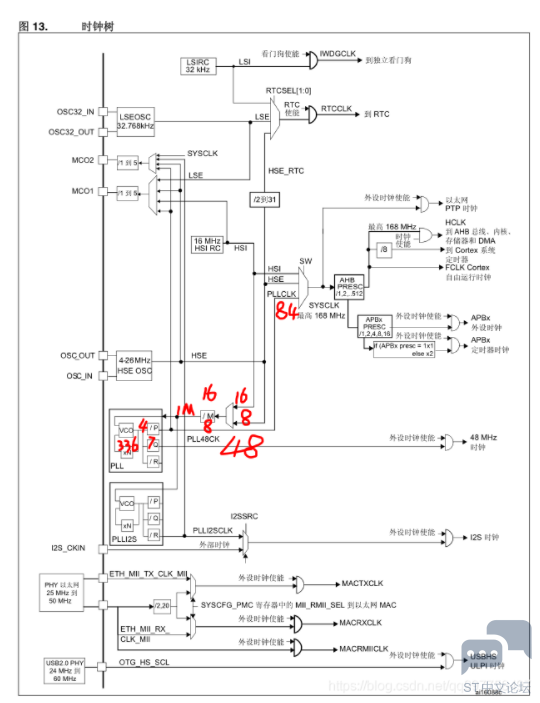

之前有用过STM32的F4系列单片机,该单片机的强大之处可以度娘一下,因为打算系统的学习下,所以自己做了一个板子用作学习,把资料都准备好,主要是官方的标准库及例程,学32第一件事情就是要搞清楚时钟,相对传统的51,32的时钟相对复杂很多,M3内核如此,M4内核更甚。下面贴出M4的时钟树:

可以看到时钟树很复杂,我用的芯片是STM32F401系列的,官方给的数据是最高时钟能达到84M,我也有朋友直接超频到120M用的,不过在产品设计上还是要以稳定为主。上图的注释是我后来加的,这里主要记录一下我如何配置系统时钟及踩到坑。在最开始的时候使用官方的例程,发现时钟不对,查底层的时候发现官方测试的目标板使用的是25M的晶体,而我们常用的是8M,我这里也使用的8M晶体,所以我进行了如下修改: ![{]BHAHF[IPI}_T2%ZONP[ZV.png {]BHAHF[IPI}_T2%ZONP[ZV.png](data/attachment/forum/202203/16/110209l6tfz6yij7okya04.png)

首先常用的系统源是PLL,而在M4内核上PLL时钟是经过内部16M或者外部晶振经过M除频、N倍频和P除频来的。这里我自己写了一个时钟函数,可以选择外部时钟和内部时钟。代码如下:

这个函数在主函数的入口处执行,注释的也很详细。传入参数有两个,第一个是选择内部时钟或者外部时钟,代码中有定义,第二个是M除频,在使用外部时钟的时候需要根据目标版的晶体频率选择,以保证经过晶体频率经过M除频后是1MHz的频率。如果是选用的内部时钟,则第二个参数无效,可以看到代码里面直接是16的除频而没有用到输入的参数作为M除频。这是因为内部时钟是固定的16MHz,所以就固定死了。亲测这个函数是有效的。但是我在使用的时候开始就出现了问题。在一些外设的配置中时钟就不对,这里拿串口作为例子。通过串口的配置底层可以看到一个函数:

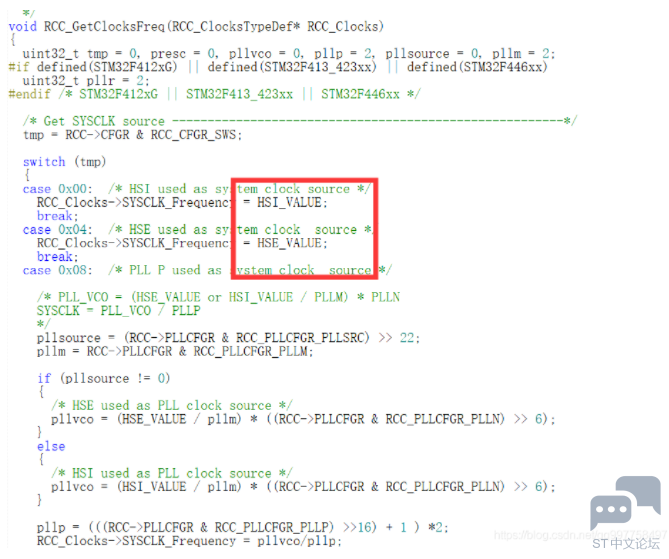

可以看到串口的波特率是系统根据时钟去自动计算的,所以在计算之前需要得到时钟频率,此时会调用上图的获取时钟函数。这个地方也是我采坑的地方。花了点时间终于找到问题,跳进去时钟获取函数去看发现了一个宏定义:

就是这个,一个是内部时钟一个是外部时钟,继续跟进会看到: ![XWYM}WEY1{9YHQ]4RP4HA1X.png XWYM}WEY1{9YHQ]4RP4HA1X.png](data/attachment/forum/202203/16/110211fjmjj8mzzlw8rmlc.png)

它上面标的是25Mhz,这就是外设时钟不对的地方。其实时钟那条线都是完全ok的,只不过在配置这个串口的时候调用了这个错误的宏定义,然后就导致外设输出结果不对。找到问题就好办了,把25M改成自己的8M,问题解决,世界安静了。 |

微信公众号

微信公众号

手机版

手机版