01. STM32F4时钟系统概述

时钟系统是 CPU 的脉搏,就像人的心跳一样。所以时钟系统的重要性就不言而喻了。 STM32F4 的时钟系统比较复杂,不像简单的 51 单片机一个系统时钟就可以解决一切。于是有人要问,采用一个系统时钟不是很简单吗?为什么 STM32 要有多个时钟源呢? 因为首先 STM32 本身非常复杂,外设非常的多,但是并不是所有外设都需要系统时钟这么高的频率,比如看门狗以及 RTC 只需要几十 k 的时钟即可。同一个电路,时钟越快功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的 MCU 一般都是采取多时钟源的方法来解决这些问题。

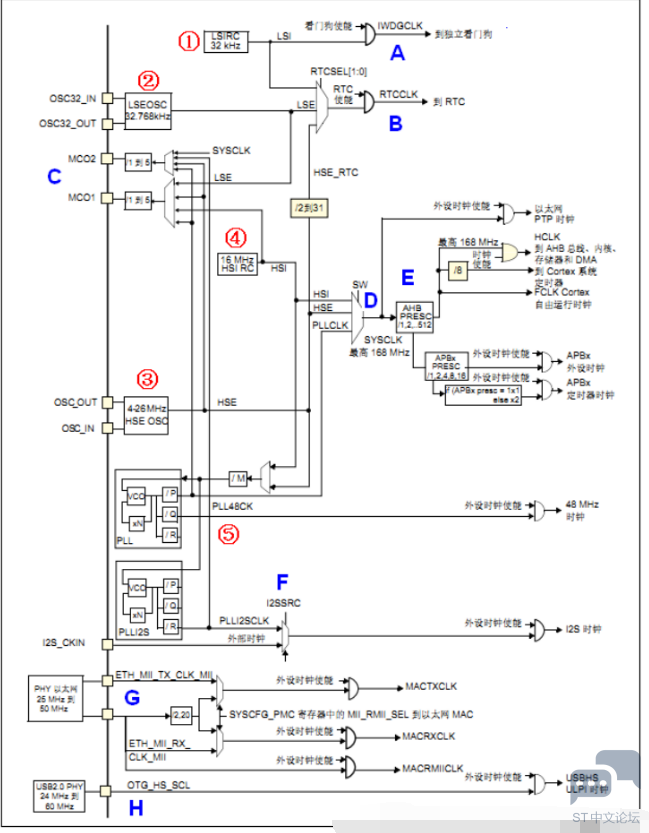

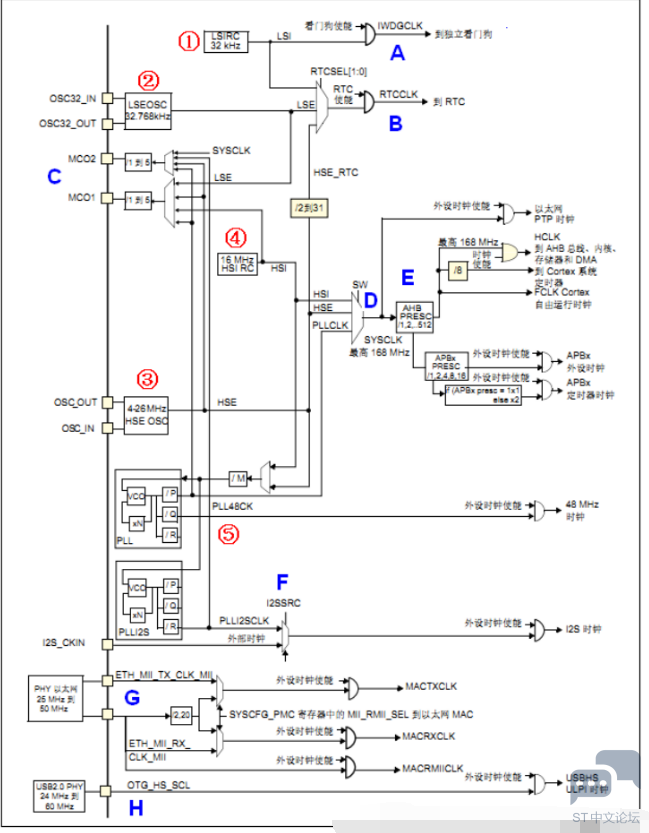

02. STM32F4时钟系统图

在 STM32F4 中,有 5 个最重要的时钟源,为 HSI、HSE、LSI、LSE、PLL。其中 PLL 实际是分为两个时钟源,分别为主 PLL 和专用 PLL。从时钟频率来分可以分为高速时钟源和低速时钟源,在这 5 个中 HSI,HSE 以及 PLL 是高速时钟,LSI 和 LSE 是低速时钟。从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的方式获取时钟源,其中 HSE 和LSE 是外部时钟源,其他的是内部时钟源。下面我们看看 STM32F4 的这 5 个时钟源,我们讲解顺序是按图中红圈标示的顺序:

①、LSI 是低速内部时钟,RC 振荡器,频率为 32kHz 左右。供独立看门狗和自动唤醒单元使用。

②、LSE 是低速外部时钟,接频率为 32.768kHz 的石英晶体。这个主要是 RTC 的时钟源。

③、HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~26MHz。我们的开发板接的是 8M 的晶振。HSE 也可以直接做为系统时钟或者 PLL 输入。

④、HSI 是高速内部时钟,RC 振荡器,频率为 16MHz。可以直接作为系统时钟或者用作 PLL输入。

⑤、PLL 为锁相环倍频输出。STM32F4 有两个 PLL:

1) 主 PLL(PLL)由 HSE 或者 HSI 提供时钟信号,并具有两个不同的输出时钟。

第一个输出 PLLP 用于生成高速的系统时钟(最高 168MHz)

第二个输出 PLLQ 用于生成 USB OTG FS 的时钟(48MHz),随机数发生器的时钟和 SDIO时钟。

2)专用 PLL(PLLI2S)用于生成精确时钟,从而在 I2S 接口实现高品质音频性能。

A. 这里是看门狗时钟输入。从图中可以看出,看门狗时钟源只能是低速的 LSI 时钟。

B. 这里是 RTC 时钟源,从图上可以看出,RTC 的时钟源可以选择 LSI,LSE,以及HSE 分频后的时钟,HSE 分频系数为 2~31。

C. 这里是 STM32F4 输出时钟 MCO1 和 MCO2。MCO1 是向芯片的 PA8 引脚输出时钟。它有四个时钟来源分别为:HSI,LSE,HSE 和 PLL 时钟。MCO2 是向芯片的PC9 输出时钟,它同样有四个时钟来源分别为:HSE,PLL,SYSCLK 以及 PLLI2S时钟。MCO 输出时钟频率最大不超过 100MHz。

D. 这里是系统时钟。从图 4.3.1 可以看出,SYSCLK 系统时钟来源有三个方面:HSI,HSE 和 PLL。在我们实际应用中,因为对时钟速度要求都比较高我们才会选用 STM32F4 这种级别的处理器,所以一般情况下,都是采用 PLL 作为 SYSCLK时钟源。根据前面的计算公式,大家就可以算出你的系统的 SYSCLK 是多少。

E. 这里我们指的是以太网 PTP 时钟,AHB 时钟,APB2 高速时钟,APB1 低速时钟。这些时钟都是来源于 SYSCLK 系统时钟。其中以太网 PTP 时钟是使用系统时钟。AHB,APB2 和 APB1 时钟是经过 SYSCLK 时钟分频得来。这里大家记住,AHB最大时钟为168MHz, APB2高速时钟最大频率为84MHz,而APB1低速时钟最大频率为 42MHz。

F. 这里是指 I2S 时钟源。从图 4.3.1 可以看出,I2S 的时钟源来源于 PLLI2S 或者映射到 I2S_CKIN 引脚的外部时钟。I2S 出于音质的考虑,对时钟精度要求很高。探索者 STM32F4 开发板使用的是内部 PLLI2SCLK。

G. 这是 STM32F4 内部以太网 MAC 时钟的来源。对于 MII 接口来说,必须向外部PHY 芯片提供 25Mhz 的时钟,这个时钟,可以由 PHY 芯片外接晶振,或者使用STM32F4 的 MCO 输出来提供。然后,PHY 芯片再给 STM32F4 提供ETH_MII_TX_CLK 和 ETH_MII_RX_CLK 时钟。对于 RMII 接口来说,外部必须提供 50Mhz 的时钟驱动 PHY 和 STM32F4 的 ETH_RMII_REF_CLK,这个 50Mhz时钟可以来自 PHY、有源晶振或者 STM32F4 的 MCO。我们的开发板使用的是RMII 接 口 , 使 用 PHY 芯 片 提 供 50Mhz 时 钟 驱 动 STM32F4 的ETH_RMII_REF_CLK。

H. 这里是指外部 PHY 提供的 USB OTG HS(60MHZ)时钟。

03. STM32F4时钟初始化配置

STM32F4 时钟系统初始化是在 system_stm32f4xx.c 中的 SystemInit()函数中完成的。对于系统时钟关键寄存器设置主要是在 SystemInit 函数中调用 SetSysClock()函数来设置的。我们可以先看看 SystemInit ()函数体。

- /**

- * @brief Setup the microcontroller system

- * Initialize the Embedded Flash Interface, the PLL and update the

- * SystemFrequency variable.

- * @param None

- * @retval None

- */

- void SystemInit(void)

- {

- /* FPU settings ------------------------------------------------------------*/

- #if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

- SCB->CPACR |= ((3UL << 10*2)|(3UL << 11*2)); /* set CP10 and CP11 Full Access */

- #endif

- /* Reset the RCC clock configuration to the default reset state ------------*/

- /* Set HSION bit */

- RCC->CR |= (uint32_t)0x00000001;

- /* Reset CFGR register */

- RCC->CFGR = 0x00000000;

- /* Reset HSEON, CSSON and PLLON bits */

- RCC->CR &= (uint32_t)0xFEF6FFFF;

- /* Reset PLLCFGR register */

- RCC->PLLCFGR = 0x24003010;

- /* Reset HSEBYP bit */

- RCC->CR &= (uint32_t)0xFFFBFFFF;

- /* Disable all interrupts */

- RCC->CIR = 0x00000000;

- #if defined(DATA_IN_ExtSRAM) || defined(DATA_IN_ExtSDRAM)

- SystemInit_ExtMemCtl();

- #endif /* DATA_IN_ExtSRAM || DATA_IN_ExtSDRAM */

- /* Configure the System clock source, PLL Multiplier and Divider factors,

- AHB/APBx prescalers and Flash settings ----------------------------------*/

- SetSysClock();

- /* Configure the Vector Table location add offset address ------------------*/

- #ifdef VECT_TAB_SRAM

- SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM */

- #else

- SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH */

- #endif

- }

在设置完相关寄存器后,接下来 SystemInit 函数内部会调用 SetSysClock 函数。

- /**

- * @brief Configures the System clock source, PLL Multiplier and Divider factors,

- * AHB/APBx prescalers and Flash settings

- * @Note This function should be called only once the RCC clock configuration

- * is reset to the default reset state (done in SystemInit() function).

- * @param None

- * @retval None

- */

- static void SetSysClock(void)

- {

- #if defined(STM32F40_41xxx) || defined(STM32F427_437xx) || defined(STM32F429_439xx) || defined(STM32F401xx) || defined(STM32F412xG) || defined(STM32F413_423xx) || defined(STM32F446xx)|| defined(STM32F469_479xx)

- /******************************************************************************/

- /* PLL (clocked by HSE) used as System clock source */

- /******************************************************************************/

- __IO uint32_t StartUpCounter = 0, HSEStatus = 0;

- /* Enable HSE */ //HSE时钟使能

- RCC->CR |= ((uint32_t)RCC_CR_HSEON);

- //等待HSE时钟稳定

- /* Wait till HSE is ready and if Time out is reached exit */

- do

- {

- HSEStatus = RCC->CR & RCC_CR_HSERDY;

- StartUpCounter++;

- } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

- if ((RCC->CR & RCC_CR_HSERDY) != RESET)

- {

- HSEStatus = (uint32_t)0x01;

- }

- else

- {

- HSEStatus = (uint32_t)0x00;

- }

- if (HSEStatus == (uint32_t)0x01)

- {

- /* Select regulator voltage output Scale 1 mode */

- RCC->APB1ENR |= RCC_APB1ENR_PWREN;

- PWR->CR |= PWR_CR_VOS;

- //AHB不分频

- /* HCLK = SYSCLK / 1*/

- RCC->CFGR |= RCC_CFGR_HPRE_DIV1;

- #if defined(STM32F40_41xxx) || defined(STM32F427_437xx) || defined(STM32F429_439xx) || defined(STM32F412xG) || defined(STM32F446xx) || defined(STM32F469_479xx)

- /* PCLK2 = HCLK / 2*/ //高速APB二分频

- RCC->CFGR |= RCC_CFGR_PPRE2_DIV2;

- /* PCLK1 = HCLK / 4*/ //低速APB4分频

- RCC->CFGR |= RCC_CFGR_PPRE1_DIV4;

- #endif /* STM32F40_41xxx || STM32F427_437x || STM32F429_439xx || STM32F412xG || STM32F446xx || STM32F469_479xx */

- #if defined(STM32F401xx) || defined(STM32F413_423xx)

- /* PCLK2 = HCLK / 1*/

- RCC->CFGR |= RCC_CFGR_PPRE2_DIV1;

- /* PCLK1 = HCLK / 2*/

- RCC->CFGR |= RCC_CFGR_PPRE1_DIV2;

- #endif /* STM32F401xx || STM32F413_423xx */

- #if defined(STM32F40_41xxx) || defined(STM32F427_437xx) || defined(STM32F429_439xx) || defined(STM32F401xx) || defined(STM32F469_479xx)

- /* Configure the main PLL */

- RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |

- (RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);

- #endif /* STM32F40_41xxx || STM32F401xx || STM32F427_437x || STM32F429_439xx || STM32F469_479xx */

- #if defined(STM32F412xG) || defined(STM32F413_423xx) || defined(STM32F446xx)

- /* Configure the main PLL */

- RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |

- (RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24) | (PLL_R << 28);

- #endif /* STM32F412xG || STM32F413_423xx || STM32F446xx */

- /* Enable the main PLL */

- RCC->CR |= RCC_CR_PLLON;

- /* Wait till the main PLL is ready */

- while((RCC->CR & RCC_CR_PLLRDY) == 0)

- {

- }

- #if defined(STM32F427_437xx) || defined(STM32F429_439xx) || defined(STM32F446xx) || defined(STM32F469_479xx)

- /* Enable the Over-drive to extend the clock frequency to 180 Mhz */

- PWR->CR |= PWR_CR_ODEN;

- while((PWR->CSR & PWR_CSR_ODRDY) == 0)

- {

- }

- PWR->CR |= PWR_CR_ODSWEN;

- while((PWR->CSR & PWR_CSR_ODSWRDY) == 0)

- {

- }

- /* Configure Flash prefetch, Instruction cache, Data cache and wait state */

- FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS;

- #endif /* STM32F427_437x || STM32F429_439xx || STM32F446xx || STM32F469_479xx */

- #if defined(STM32F40_41xxx) || defined(STM32F412xG)

- /* Configure Flash prefetch, Instruction cache, Data cache and wait state */

- FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS;

- #endif /* STM32F40_41xxx || STM32F412xG */

- #if defined(STM32F413_423xx)

- /* Configure Flash prefetch, Instruction cache, Data cache and wait state */

- FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_3WS;

- #endif /* STM32F413_423xx */

- #if defined(STM32F401xx)

- /* Configure Flash prefetch, Instruction cache, Data cache and wait state */

- FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_2WS;

- #endif /* STM32F401xx */

- /* Select the main PLL as system clock source */

- RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

- RCC->CFGR |= RCC_CFGR_SW_PLL;

- /* Wait till the main PLL is used as system clock source */

- while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL);

- {

- }

- }

- else

- { /* If HSE fails to start-up, the application will have wrong clock

- configuration. User can add here some code to deal with this error */

- }

- #elif defined(STM32F410xx) || defined(STM32F411xE)

- #if defined(USE_HSE_BYPASS)

- /******************************************************************************/

- /* PLL (clocked by HSE) used as System clock source */

- /******************************************************************************/

- __IO uint32_t StartUpCounter = 0, HSEStatus = 0;

- /* Enable HSE and HSE BYPASS */

- RCC->CR |= ((uint32_t)RCC_CR_HSEON | RCC_CR_HSEBYP);

- /* Wait till HSE is ready and if Time out is reached exit */

- do

- {

- HSEStatus = RCC->CR & RCC_CR_HSERDY;

- StartUpCounter++;

- } while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

- if ((RCC->CR & RCC_CR_HSERDY) != RESET)

- {

- HSEStatus = (uint32_t)0x01;

- }

- else

- {

- HSEStatus = (uint32_t)0x00;

- }

- if (HSEStatus == (uint32_t)0x01)

- {

- /* Select regulator voltage output Scale 1 mode */

- RCC->APB1ENR |= RCC_APB1ENR_PWREN;

- PWR->CR |= PWR_CR_VOS;

- /* HCLK = SYSCLK / 1*/

- RCC->CFGR |= RCC_CFGR_HPRE_DIV1;

- /* PCLK2 = HCLK / 2*/

- RCC->CFGR |= RCC_CFGR_PPRE2_DIV1;

- /* PCLK1 = HCLK / 4*/

- RCC->CFGR |= RCC_CFGR_PPRE1_DIV2;

- /* Configure the main PLL */

- RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |

- (RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);

- /* Enable the main PLL */

- RCC->CR |= RCC_CR_PLLON;

- /* Wait till the main PLL is ready */

- while((RCC->CR & RCC_CR_PLLRDY) == 0)

- {

- }

- /* Configure Flash prefetch, Instruction cache, Data cache and wait state */

- FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_2WS;

- /* Select the main PLL as system clock source */

- RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

- RCC->CFGR |= RCC_CFGR_SW_PLL;

- /* Wait till the main PLL is used as system clock source */

- while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL);

- {

- }

- }

- else

- { /* If HSE fails to start-up, the application will have wrong clock

- configuration. User can add here some code to deal with this error */

- }

- #else /* HSI will be used as PLL clock source */

- /* Select regulator voltage output Scale 1 mode */

- RCC->APB1ENR |= RCC_APB1ENR_PWREN;

- PWR->CR |= PWR_CR_VOS;

- /* HCLK = SYSCLK / 1*/

- RCC->CFGR |= RCC_CFGR_HPRE_DIV1;

- /* PCLK2 = HCLK / 2*/

- RCC->CFGR |= RCC_CFGR_PPRE2_DIV1;

- /* PCLK1 = HCLK / 4*/

- RCC->CFGR |= RCC_CFGR_PPRE1_DIV2;

- /* Configure the main PLL */

- RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) | (PLL_Q << 24);

- /* Enable the main PLL */

- RCC->CR |= RCC_CR_PLLON;

- /* Wait till the main PLL is ready */

- while((RCC->CR & RCC_CR_PLLRDY) == 0)

- {

- }

- /* Configure Flash prefetch, Instruction cache, Data cache and wait state */

- FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_2WS;

- /* Select the main PLL as system clock source */

- RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

- RCC->CFGR |= RCC_CFGR_SW_PLL;

- /* Wait till the main PLL is used as system clock source */

- while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL);

- {

- }

- #endif /* USE_HSE_BYPASS */

- #endif /* STM32F40_41xxx || STM32F427_437xx || STM32F429_439xx || STM32F401xx || STM32F469_479xx */

- }

先使能外部时钟 HSE,等待 HSE 稳定之后,配置AHB,APB1,APB2 时钟相关的分频因子,也就是相关外设的时钟。等待这些都配置完成之后,打开主 PLL 时钟,然后设置主 PLL 作为系统时钟 SYSCLK 时钟源。如果 HSE 不能达到就绪状态(比如外部晶振不能稳定或者没有外部晶振),那么依然会是 HSI 作为系统时钟。

在这里要特别提出来,在设置主 PLL 时钟的时候,会要设置一系列的分频系数和倍频系数参数。大家可以从 SetSysClock 函数的这行代码看出:

- /* Configure the main PLL */

- RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |

- (RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);

这些参数是通过宏定义标识符的值来设置的。默认的配置在 System_stm32f4xx.c 文件开头的地方配置。对于我们开发板,我们的设置参数值如下:

- #define PLL_M 8

- #define PLL_Q 7

- #define PLL_N 336

- #define PLL_P 2

这里还有个特别需要注意的地方,就是我们还要同步修改 stm32f4xx.h 中宏定义标识符HSE_VALUE 的值为我们的外部时钟:

- #if !defined (HSE_VALUE)

- #define HSE_VALUE ((uint32_t)8000000) /*!< Value of the External oscillator in Hz */

- #endif /* HSE_VALUE */

这里默认固件库配置的是 25000000,我们外部时钟为 8MHz,所以我们根据我们硬件情况修改为 8000000 即可。

04. 时钟配置总结

最后我们总结一下 SystemInit()函数中设置的系统时钟大小:

SYSCLK(系统时钟) =168MHz

AHB 总线时钟(HCLK=SYSCLK) =168MHz

APB1 总线时钟(PCLK1=SYSCLK/4) =42MHz

APB2 总线时钟(PCLK2=SYSCLK/2) =84MHz

PLL 主时钟 =168MHz

|

.png) STMCU小助手

发布时间:2022-6-10 20:08

STMCU小助手

发布时间:2022-6-10 20:08

微信公众号

微信公众号

手机版

手机版