.png) STMCU小助手

发布时间:2022-7-11 22:41

STMCU小助手

发布时间:2022-7-11 22:41

|

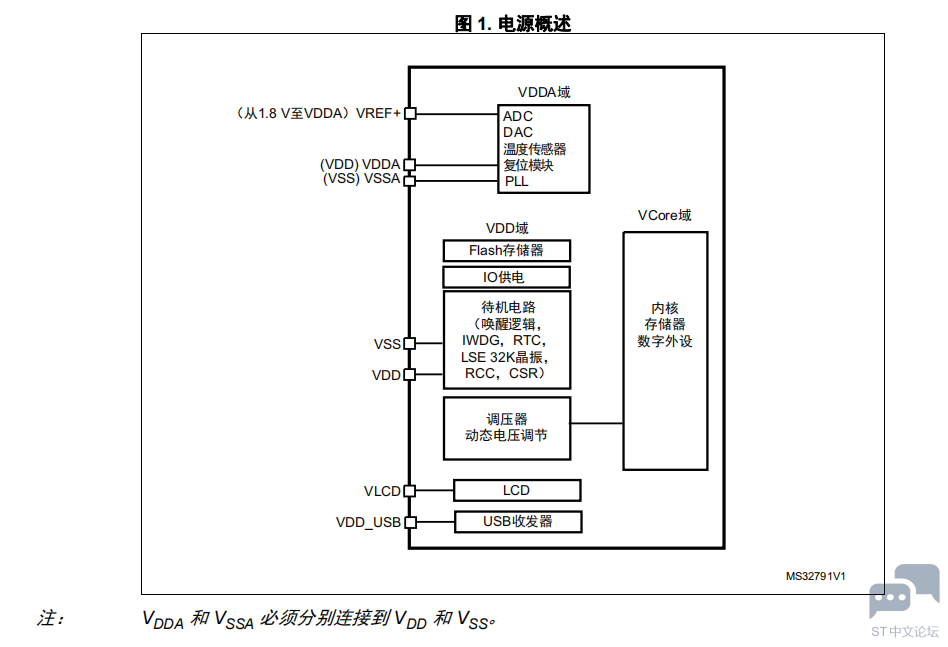

前言 本应用笔记为系统开发者们提供了所需的开发板特性硬件实现概述,如供电电源、时钟管理、复位控制、自举模式设置、调试管理。它显示了如何使用 STM32L0xx 产品系列,说明了开发 STM32L0xx 应用所需的最低硬件资源。 本文还包括了详细的参考设计原理图,说明了其主元件、接口和模式。 1 电源 1.1 前言 该芯片要求为不同的供电引脚提供不同的电源: • VDD = 1.65 V 到 3.6 V:I/O 和内部调压器的外部电源。通过 VDD 引脚从外部提供。对于 VDD 低于 1.8V 的情况,请参见 第 1.3.3 节:欠压复位 (BOR) • VDDA = VDD:ADC/DAC、比较器、复位模块、RC、PLL 的外部模拟电源。 当使用 DAC时,施加于 VDDA 的最低电压为 1.8 V。 VDDA 电平必须一直等于 VDD。在上电和正常工作期间, VDD 和 VDDA 之间容许的最大差值为 300 mV。 • VLCD= 2.5 到 3.6 V,当 LCD 控制器采用外部供电时须提供该电压。当 LCD 由内部嵌入式升压转换器所产生的电压供电时, VLCD 引脚必须连接至电容器。如果完全无需使用 LCD,那么该引脚应连接至 VDDA。 • VDD_USB = 3.0 到 3.6 V,VDD_USB 是 USB 收发器的专用独立 USB 电源。3.0V 的最小值可确保提供 USB 所需的信号电压。对于不使用 USB 的应用场合,必须提供VDD_USB = 1.65 到 3.6 V。 数字电源电压 (VCORE)配有嵌入式的线性调压器,具有 1.2 至 1.8 V 的三个不同的可编程范围。 为达到全速、全功能,器件需要 1.71 至 3.6 V 的工作电压供电 (VDD),可达到接近 1.8 V的数字电源电压 VCORE (产品电压范围 1)。 当 VDD 工作于 1.65 至 3.6 V 时,可选择产品电压范围 2 (VCORE = 1.5 V)和 3 (VCORE = 1.2 V)。因此,频率分别限定为 16 MHz 和 4.2 MHz。 当不使用 DAC 和欠压复位 (BOR)时,器件可在 1.8 V 下至 1.65 V 的电源电压工作。

1.1.1 独立 A/D 转换器电源和参考电压 为了提高转换精度, ADC 和 DAC 配有独立电源,可以单独滤波并屏蔽 PCB 上的噪声。 • ADC 电压源从单独的 VDDA 引脚输入。 • VSSA 引脚提供了独立的电源接地连接。 VDDA 和 VREF 需要一个稳定的电压。 VDDA 上的耗电电流可达若干 mA (若需更多信息,请参见产品手册中的 IDD (ADCx)、 IDD (DAC)、 IDD (COMPx)和 IDDA)。 当可行时 (取决于封装), VREF- 必须连至 VSSA。 VSSA 和 VREF- 必须直接连接至 VSS,不得使用任何滤波器件,以免引起 ESD 问题。 在某些带有引脚 VREF+ 的封装上,为确保低电压输入和输出上的更好精度,用户可将 VREF+连接至一个独立的,低于 VDD 的外部参考电压源。对于模拟输入 (ADC)或输出 (DAC)信号, VREF+ 为最高电压,以满量程值表示。 对于不设有该专用引脚的封装, VREF+ 会在内部链接到 ADC 电压源 (VDDA)。 1.1.2 独立 LCD 电源 (仅适用于 STM32L0x3) VLCD 引脚用于控制玻璃 LCD 的对比度。可用两种方法使用这一引脚: • 它可从外部电路接收所需的最大电压,由微控制器通过 segment 和 common 线供给玻璃LCD。 • 还可用它连接外部电容,微控制器将该电容用于内部的升压转换器。此升压转换器由软件控制,以向玻璃 LCD 的 segment 和 common 线提供所需的电压。请参考专门的产品数据手册以获得该电容值。 向 segment 和 common 线提供的电压定义了玻璃 LCD 像素的对比度。当在帧间配置了死区时,可降低此对比度。 对于大像素的 LCD,像素的高电容值会降低 LCD 的信号波形质量。所以该器件可以将内部的 VLCD 线路(LCD_VLCD1、LCD_VLCD2、LCD_VLCD3)连接至可选的电容。这种方式通过限制使用高阻值电阻网络来改善段线和共用线的信号波形质量,这样无须额外流耗即可改善信号质量。这些去耦合电容的电容值必须根据 LCD 玻璃和 PCB 的电容值进行调整。作为参考,用户可将去耦电容器的电容值设为 LCD 和 PCB 电容值的 10 倍。 LCD 引线必须按照偏置配置来连接。

1.1.3 调压器 此内部调压器在复位后始终处于使能状态。可配置其为内核提供三个不同的电压范围。选择 一个低 Vcore 范围可降低耗电,但会降低最大可接受内核速度。以降序排列的耗电范围如 下: • 范围 1,仅对高于 1.71 V 的 VDD 可用,具有最大速度; • 范围 2 具有高至 16 MHz 的 CPU 频率; • 范围 3 具有高至 4.2 MHz 的 CPU 频率。 注: 在范围 1 中,当 VDD 低于 2.0V 时,必须管理处于运行模式的 CPU 频率,以避免单次动作的变化比例超过 4。两次动作之间的延迟必须达到 5µs。当从低功耗模式唤醒时则无此限制。 根据应用的不同,调压器可采用三种不同的模式工作: • 在运行模式中,调压器为 Vcore 域 (内核、存储器和数字外设)提供全功率; • 在停止模式、低功耗运行与低功耗等待模式中,调压器为 Vcore 域提供低功耗,以保留寄存器和 SRAM 的内容。 • 在待机模式中,调压器掉电。除了由备用电路供电的部分,寄存器和 SRAM 的内容丢失。 1.2 电源方案 电路由稳定的供电电源 VDD 供电。 • VDD 引脚必须连至带有外部去耦电容的 VDD ;封装的单个钽电容或陶瓷电容 (最低4.7 µF,典型 10 µF) + 每个 VDD 引脚一个 100 nF 陶瓷电容)。 • VDDA 引脚必须连至两个外部去耦电容 (100 nF 陶瓷电容 + 1 µF 钽电容或陶瓷电容)。 • VREF+ 引脚可连至 VDDA 外部供电电源。若在 VREF+ 上施加了一个单独的外部参考电压, 则必须将一个 100 nF 和一个 1 µF 电容连至此引脚。若需补偿 Vref 上的峰值耗电,当采样速度高时,可将 1 µF 电容增加至最大 10 µF。当使用 ADC 或 DAC 时, VREF+ 必须保持在 1.8 V 和 VDDA 之间。当 ADC 和 DAC 未激活时, VREF+ 可接地;这可让用户能够关闭外部电压参考。 • 可采用更多措施过滤数字噪声:VDDA 可通过铁氧体磁环连至 VDD。这种情况下,注意保持 (VDDA- VDD) 差小于 300 mV。 ![G6O0`NM([ULVL]K0ZHBKBYX.png G6O0`NM([ULVL]K0ZHBKBYX.png](data/attachment/forum/202207/11/224330ul9ht2tkfhnr5rhf.png)

• 选项 1:由专用 VLCD 电源为 LCD 供电, VSEL 开关为开。 • 选项 2:由内部升压转换器为 LCD 供电,VSEL 开关关闭,需要外部电容以确保此转换器行为正确。 注: VLCD 引线的可用性取决于器件封装。 1.3 复位和电源监控 对主调压器和低功耗调压器的输入供电由上电 / 掉电 / 欠压复位电路监控。上电 / 掉电复位为零耗电监控,具有固定的门限电压,而欠压复位有多种门限可选,耗电极低但不为零。 此外, STM32L0xx 内置了一个可编程的电压检测器,用于将供电电压与可编程门限比较。当供电低于 VPVD 门限和 / 或当供电高于 VPVD 门限时,会生成中断。随后,中断服务程序会生成一条警告消息并且 / 或者使 MCU 进入安全状态。

1. 所有 STM32L 器件上都有 PVD,它可由软件启用或禁用。 2. BOR 仅在工作电压从 1.8 至 3.6 V 的器件上可用,除非被选项字节禁用,它会掩盖 POR/PDR 门限。 3. 当选项字节禁用 BOR 时,当 VDD 低于 PDR 电平时,会发生复位。 4. 工作于 1.65 至 3.6 V 的器件没有 BOR,当 VDD 高于 POR 电平时,会释放复位,当 VDD 低于 PDR 电平时,会发生复位。 1.3.1 上电复位 (POR)/ 掉电复位 (PDR),欠压复位 (BOR) 监控电压从 0.7 V 起。 上电期间,对于工作于 1.8 和 3.6 V 的器件, BOR 会保持器件处于复位,直到供电电压(VDD 和 VDDA)接近最低的可接受电压 (1.8 V)。在上电时,此内部复位会维持 ~1 ms,以等待供电达到最终值并稳定。 在掉电时,一旦电源低于最低限 (即 1.65 V),则立即激活复位。 在开机时,应维持一个 0.7 V 以下的预定义复位。复位释放的上限在产品数据手册的电气特性一节中定义。 ![74(W35A`4S8ZOH2]X0ZIQOL.png 74(W35A`4S8ZOH2]X0ZIQOL.png](data/attachment/forum/202207/11/224331cxfzw3bsf03eybke.png)

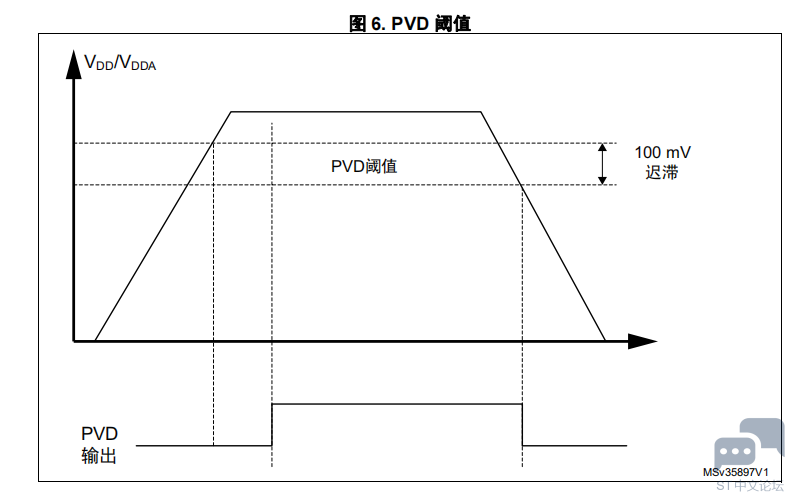

对于高于芯片最低限的可编程门限,可将欠压复位配置至需要的值。 BOR 还可用于提前检测电源压降。 BOR 的门限值可通过 FLASH_OBR 选项字节配置。 1.3.2 可编程电压检测器 (PVD) 该器件还有一个嵌入式可编程电压检测器 (PVD),用于监视 VDD/VDDA 电源并将其与 VPVD阈值进行比较。可由软件选择 1.85 V 和 3.05 V 之间的七个不同的 PVD 电平,步长为200 mV。 当 VDD/VDDA 低于 VPVD 阈值和 / 或高于 VPVD 阈值时,将产生中断。随后,中断服务程序会生成一条警告消息并且 / 或者使 MCU 进入安全状态。 PVD 由软件配置使能。该功能的用处之一就是可以在中断服务程序中执行紧急关闭系统的任务。

1.3.3 欠压复位 (BOR) 上电期间,欠压复位 (BOR) 将使器件保持复位状态,直到电源电压达到指定的 VBOR 阈值。 对于工作于 1.65 至 3.6 V 间的器件, BOR 选项不可用,电源供电由 POR/PDR 监控。由于POR/PDR 门限为 1.5 V,因此在 VPOR/VPDR 门限和最低产品工作电压 1.65 V 之间存在一个“ 盲区 ”。 对于工作于 1.8 至 3.6 V 之间的器件, BOR 在开机时一直激活,门限为 1.8 V。 当释放系统复位时,可通过加载选项字节重新配置或禁用 BOR 电平。 若 BOR 电平在开机时保持在最低电平 1.8 V,在掉电时为 1.65 V,则 BOR 完全管理系统复位,产品工作电压处于安全范围内。 当选项字节禁用 BOR 选项时,掉电复位由 PDR 控制,在 1.65 V 和 VPDR 之间存在 “ 盲区 ”。 VBOR 通过器件选项字节进行配置。默认情况下,激活最低 0 级门限。可选择五个可编程的VBOR 门限 (请参见产品手册,以获得实际的 VBOR0 至 VBOR4 门限)。 当电源电压 (VDD) 降至所选 VBOR 阈值以下时,将使器件复位。当 VDD 高于 VBOR 上限时,释放器件复位,系统可以启动。 通过对器件选项字节进行编程可以禁止 BOR。要禁止 BOR 功能, VDD 必须高于 VBOR0,以启动器件选项字节编程序列。上电和掉电由 POR 和 PDR 监控 (参见产品手册中的上电复位 (POR)/ 掉电复位 (PDR) 一节)。 BOR 阈值滞回电压约为 100 mV (电源电压的上升沿与下降沿之间) 1.3.4 系统复位 除了 RTC、备份寄存器、 RCC 控制 / 状态寄存器、 RCC_CSR 以外,一次系统复位会将所有寄存器设为其复位值。 只要发生以下事件之一,就会产生系统复位: 1. NRST 引脚低电平 (外部复位) 2. 窗口看门狗计数结束 (WWDG 复位) 3. 独立看门狗计数结束 (IWDG 复位) 4. 由软件设置复位位 (SWreset) 5. 进入所配置的待机或停止模式,生成复位 (低功耗管理复位) 6. 选项字节加载复位 7. 退出待机模式 8. 防火墙复位。 可通过查看控制 / 状态寄存器 (RCC_CSR)中的复位标志确定复位源。

STM32L 不需外部复位电路即可正确上电。仅建议一个下拉电容以提高 EMS 性能,保护器件不受非正常的复位影响 (参见图 7)。 通过内部电阻对下拉电容充电 / 放电会增加器件功耗。该电容的建议值为 100 nF,可将其降至 10 nF 以限制此功耗。 完整版请查看:附件 |

DM00112257_ZHV2.pdf

下载644.25 KB, 下载次数: 39

微信公众号

微信公众号

手机版

手机版